# digital

digital equipment corporation · maynard. massachusetts -

PDP11/20

RS64 disk file

maintenance manual

DEC-00-HRS64-E-D

1st Edition, June 1971 2nd Edition, December 1971 3rd Printing (Rev), February 1973 4th Printing (Rev), August 1973 5th Printing (Rev), October 1973

Copyright © 1971, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

UNIBUS

### CONTENTS

|         |                                               | Page |           |                                     | rag |

|---------|-----------------------------------------------|------|-----------|-------------------------------------|-----|

| CHAPTER | 1 GENERAL INFORMATION                         |      | 3.4.4     | G296 Center Tap Selector            | 3-7 |

| 1.1     | Introduction                                  | 1-1  | 3.4.5     | G738 Terminator                     | 3-7 |

| 1.2     | Purpose and Application Information           | 1-1  | 3.4.6     | G739 Peripheral Terminator          | 3-7 |

| 1.3     | Physical Description                          | 1-1  | 3.4.7     | G8001 Low-Voltage Detector          | 3-8 |

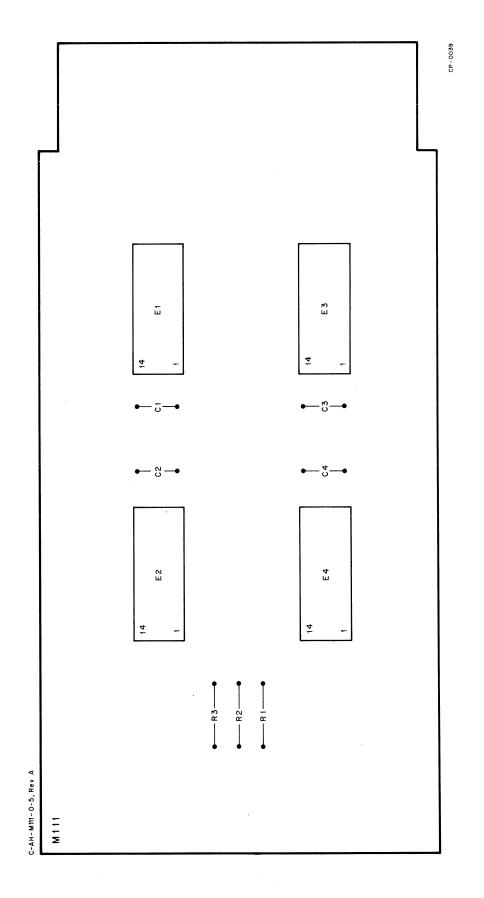

| 1.3.1   | General                                       | 1-1  | 3.4.8     | M111 Inverter                       | 3-8 |

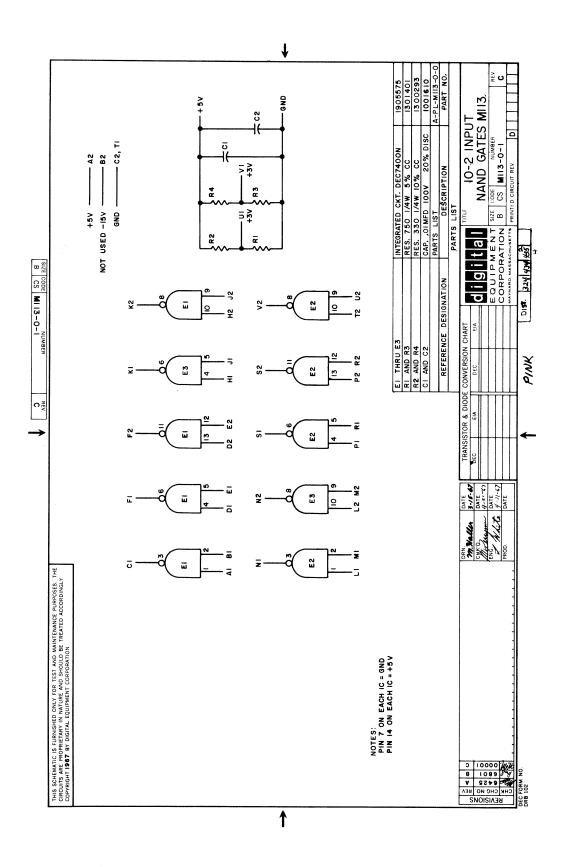

| 1.3.2   | RS64M Disk Assembly                           | 1-1  | 3.4.9     | M113 2-Input NAND Gate              | 3-8 |

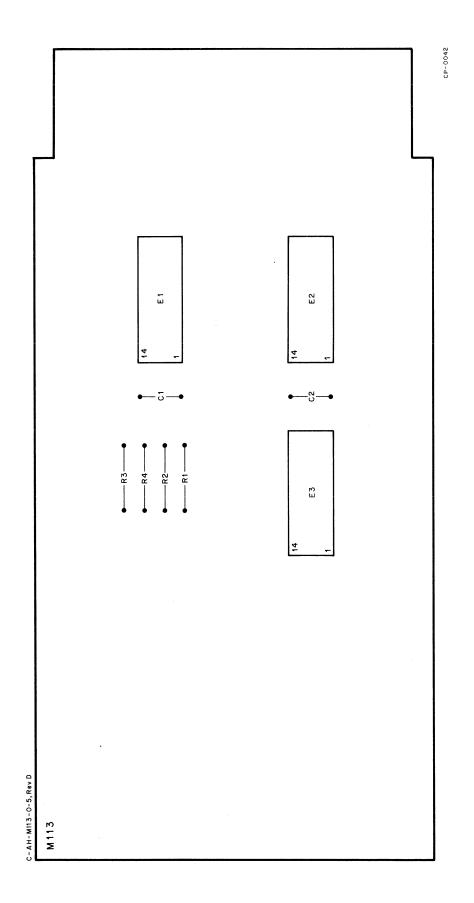

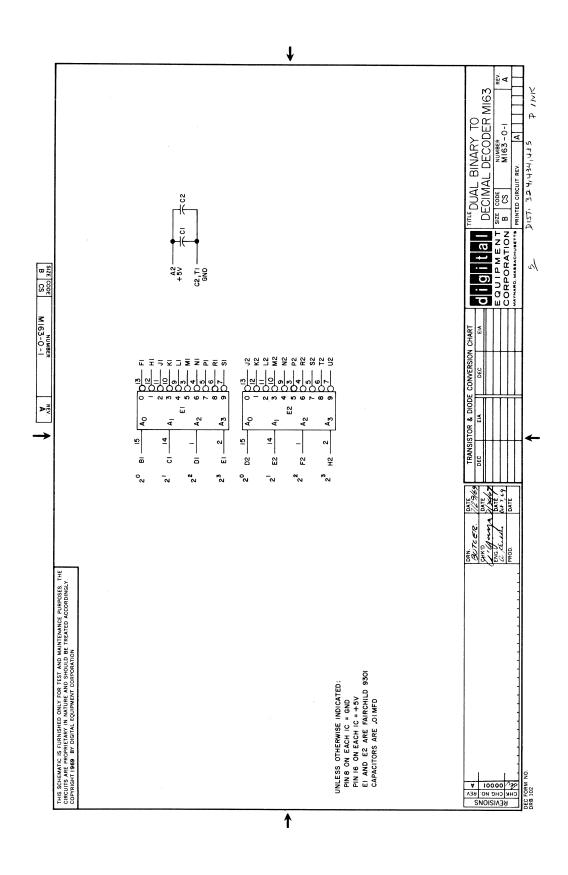

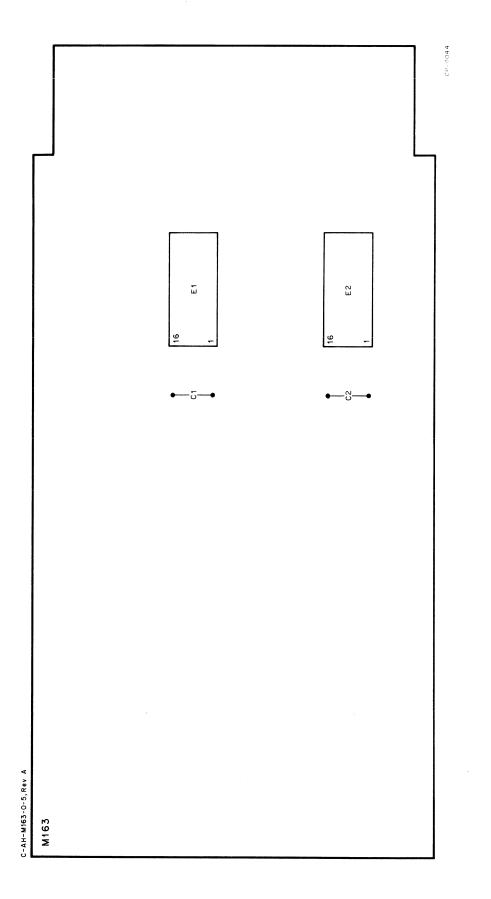

| 1.3.3   | RS64P Power Control and Logic Assembly        | 1-1  | 3.4.10    | M163 Dual Binary-To-Decimal Decoder | 3-8 |

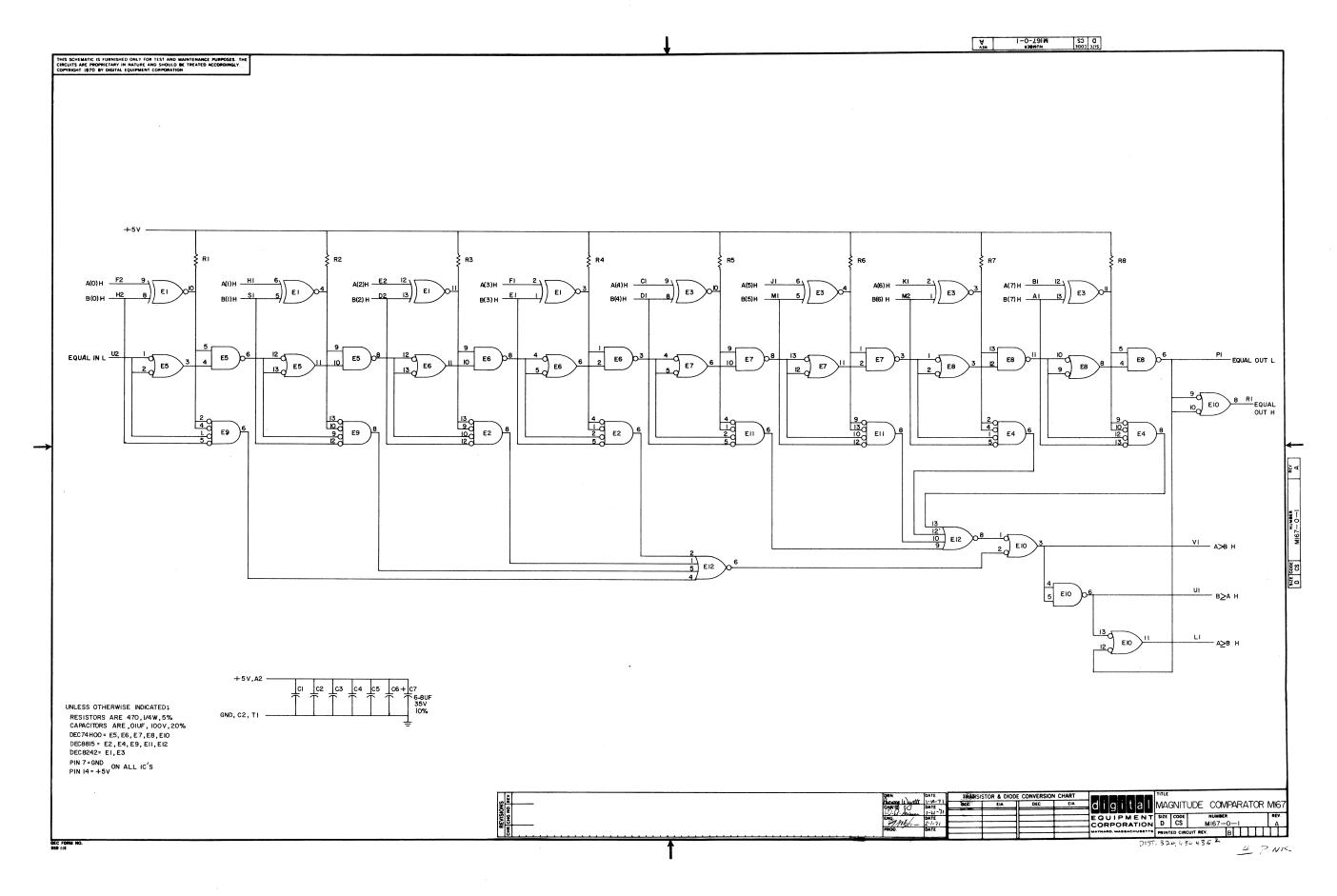

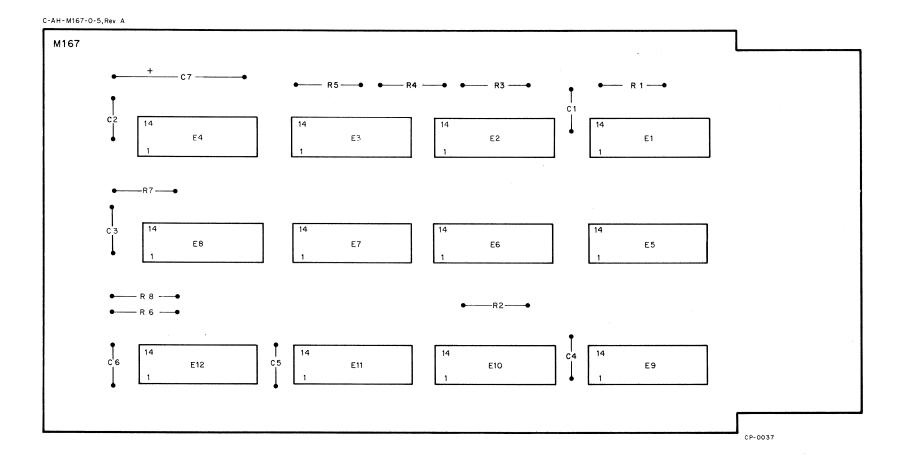

| 1.3.3.1 | Wired Assembly                                | 1-2  | 3.4.11    | M167 Magnitude Comparator           | 3-9 |

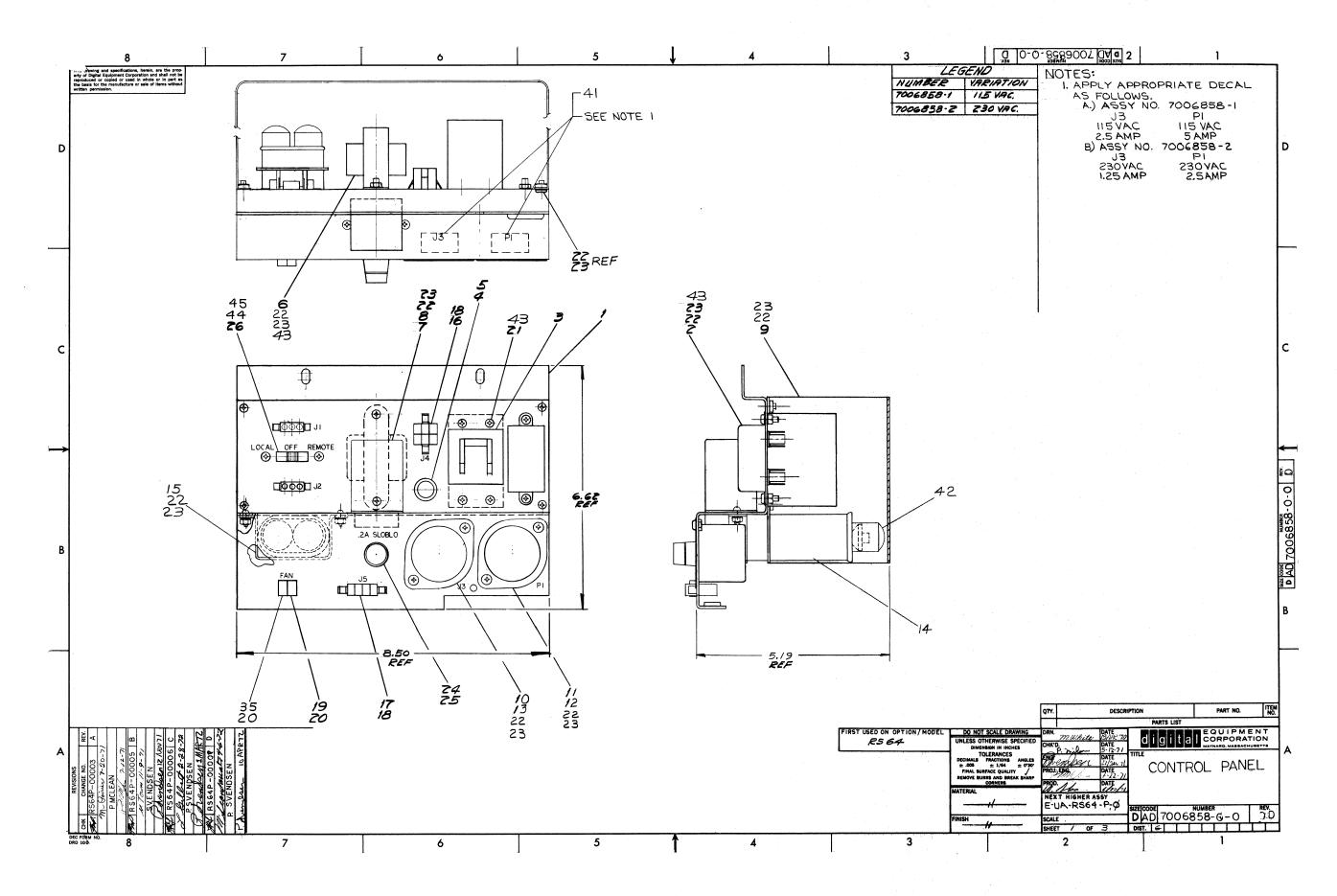

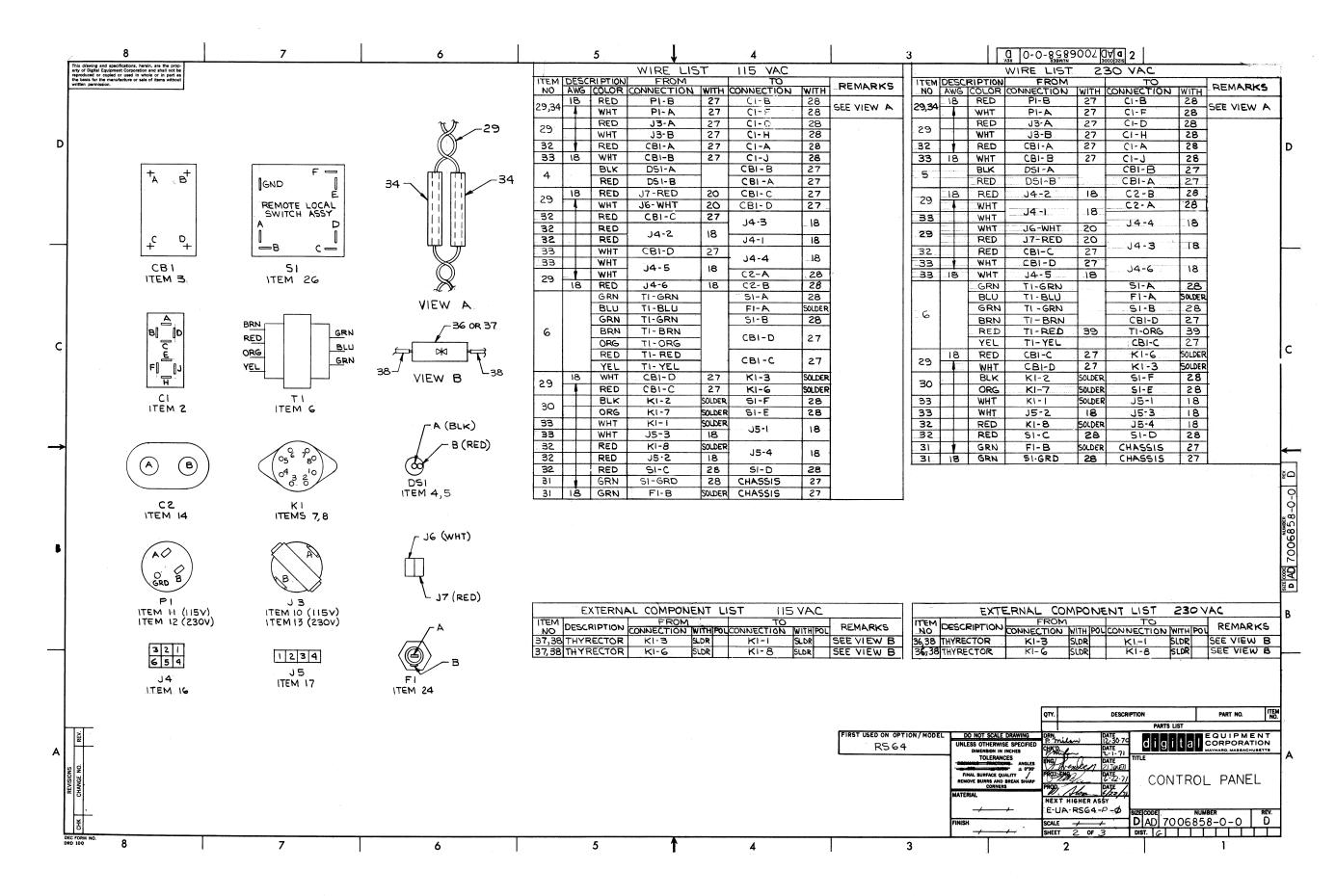

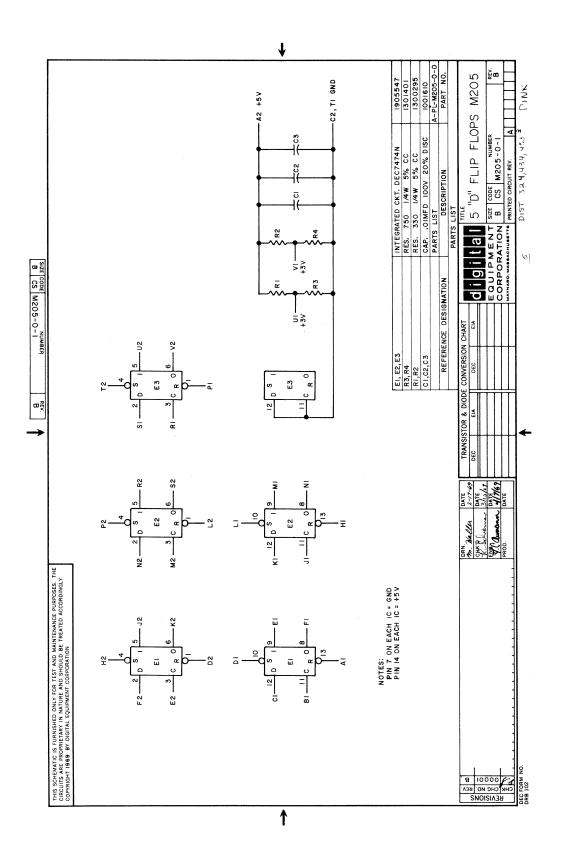

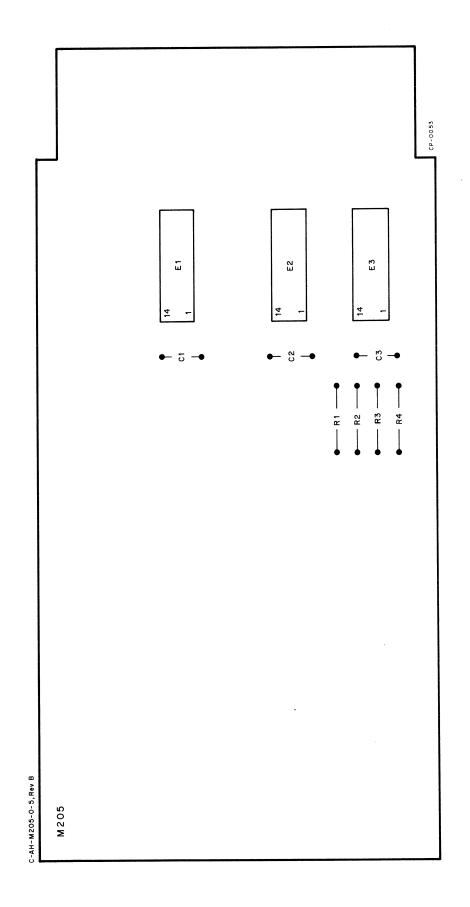

| 1.3.3.2 | Power Control Panel Assembly                  | 1-2  | 3.4.12    | M205 D-Type Flip-Flop               | 3-9 |

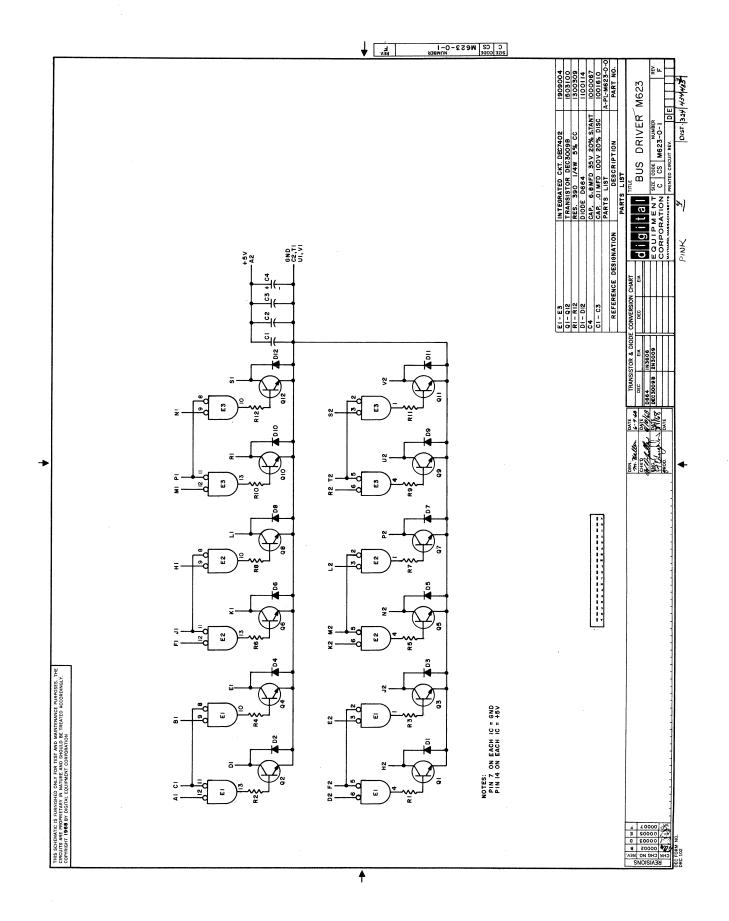

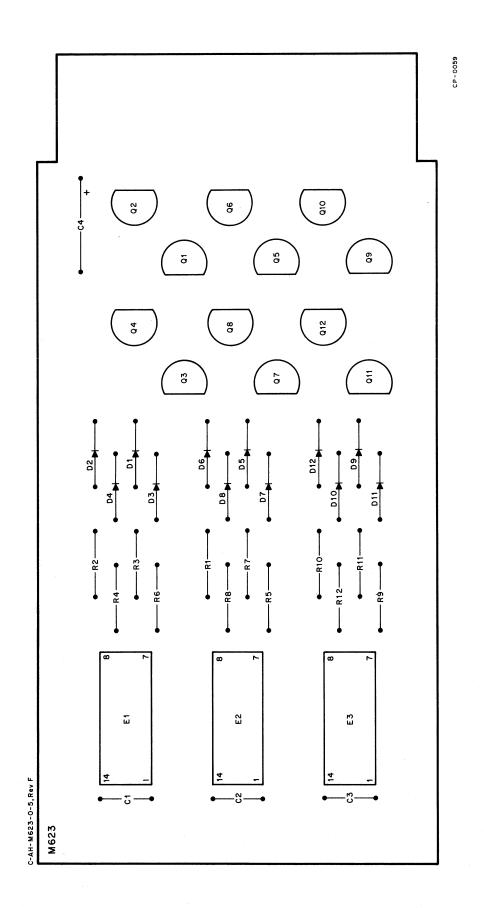

| 1.3.3.3 | Disk Select and WLO Panel Assembly            | 1-2  | 3.4.13    | M623 Bus Driver                     | 3-1 |

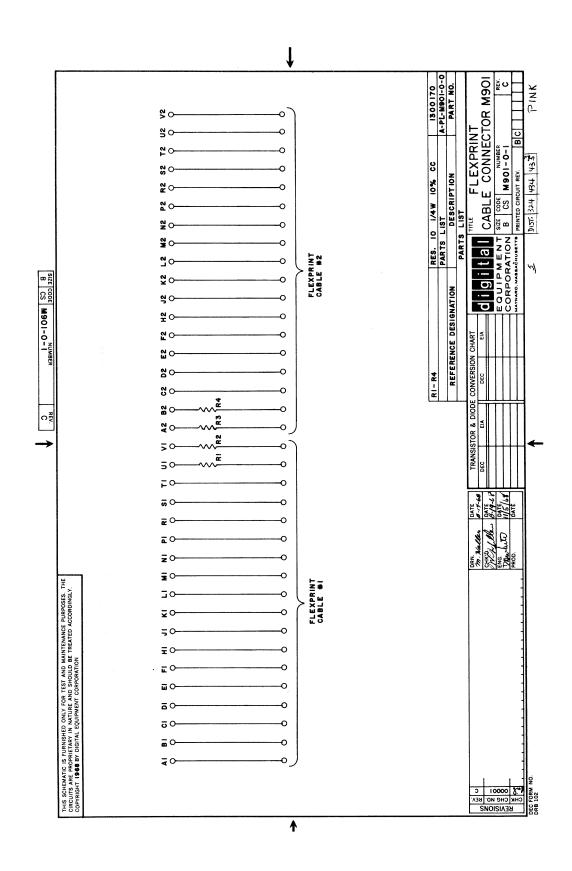

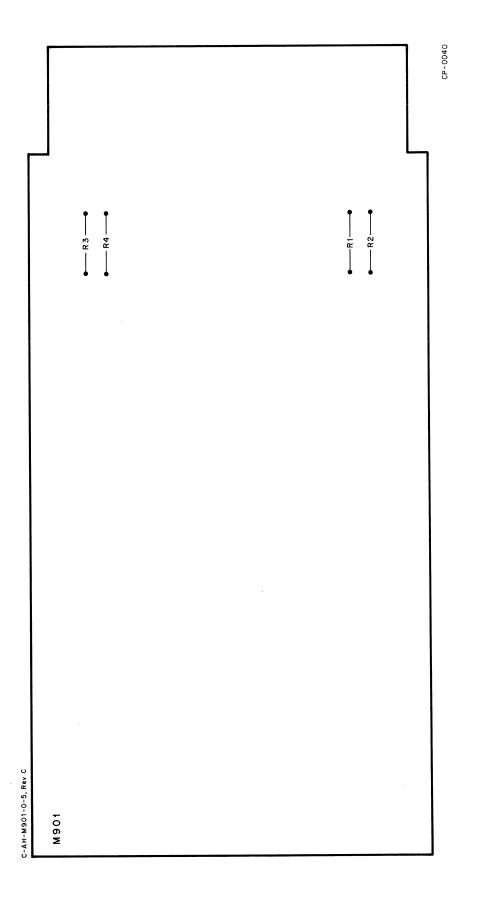

| 1.3.3.4 | Power Supply                                  | 1-2  | 3.4.14    | M901 Flat Mylar Cable Connector     | 3-1 |

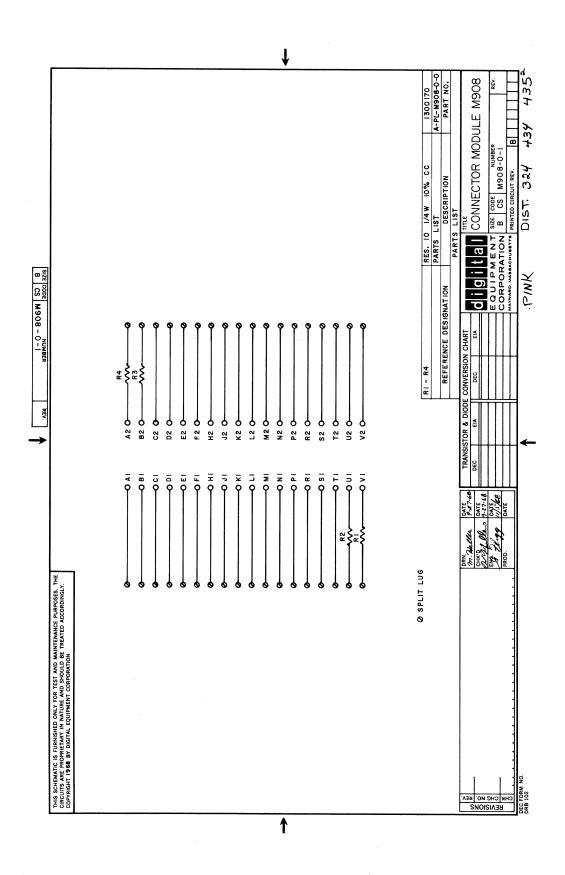

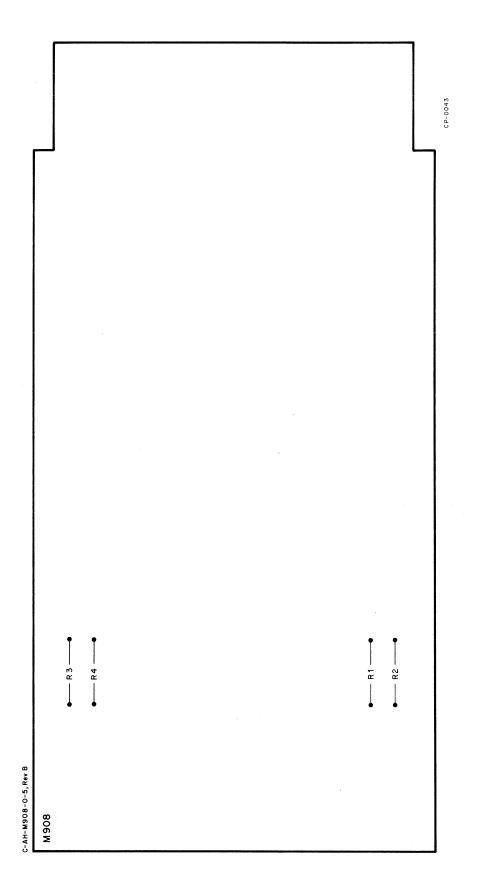

| 1.3.3.5 | Data and Timing Cable Assemblies              | 1-3  | 3.4.15    | M908 Ribbon Connector               | 3-1 |

| 1.4     | Specifications                                | 1-3  | 3.4.16    | M4201 Phase-Locked Clock            | 3-1 |

|         |                                               | 1-3  | 3.4.17    | 8-Track Matrix 5408996              | 3-1 |

| CHAPTER | 2 INSTALLATION AND OPERATION                  |      | 3.4.18    | Timing Head Matrix 5408937          | 3-1 |

| 2.1     | Unpacking and Inspection                      | 2-1  | CHAPTER 4 | 4 INTERFACING                       |     |

| 2.2     | Mechanical Installation                       | 2-1  |           |                                     |     |

| 2.3     | Power Requirements                            | 2-1  | 4.1       | Bus Voltage Spectrum                | 4-1 |

| 2.4     | Signal Connections                            | 2-1  | 4.2       | Bus Philosophy                      | 4-1 |

| 2.5     | Installation Checkout                         | 2-3  | 4.3       | Interface Signals                   | 4-1 |

| 2.6     | Preparation for Moving and Shipping Disk File | 2-3  | 4.3.1     | Disk Select (DSK SEL) 0–3           | 4-1 |

| 2.7     | Operation                                     | 2-3  | 4.3.2     | Select Acknowledge (SEL ACK)        | 4-1 |

| 2.7.1   | Power Control Panel Controls and Indicators   | 2-3  | 4.3.3     | Track Select (TK SEL) $2^0 - 2^4$   | 4-2 |

| 2.7.2   | Disk Select and WLO Panel Controls            | 2-3  | 4.3.4     | Write Lockout (WLO)                 | 4-2 |

| 2.7.3   | Operating Instructions                        | 2-4  | 4.3.5     | Clock Strobe (CLK S)                | 4-2 |

|         |                                               |      | 4.3.6     | Clock Polarity (CLK P)              | 4-2 |

| CHAPTER | 3 THEORY OF OPERATION                         |      | 4.3.7     | Address Mark                        | 4-2 |

| 2.1     |                                               |      | 4.3.8     | Data Mark                           | 4-2 |

| 3.1     | System Relationships                          | 3-1  | 4.3.9     | Address Strobe (ADR S)              | 4-2 |

| 3.2     | Disk Surface and Track Arrangement            | 3-1  | 4.3.10    | Address Polarity (ADR P)            | 4-2 |

| 3.3     | Functional Description                        | 3-1  | 4.3.11    | Read Data Strobe                    | 4-2 |

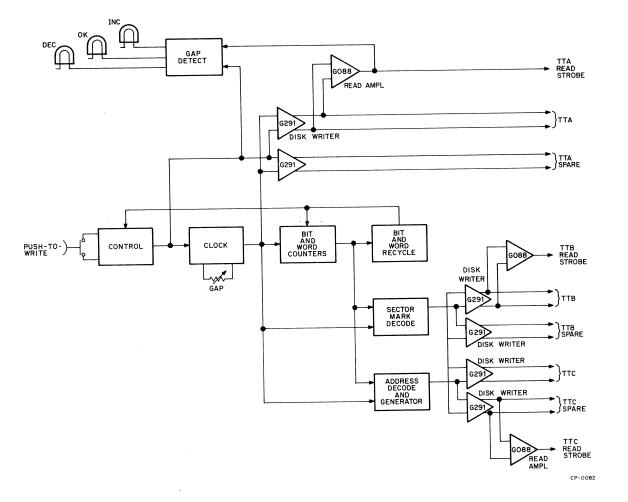

| 3.3.1   | Functional Block Description                  | 3-1  | 4.3.12    | Read Data Polarity                  | 4-2 |

| 3.3.2   | Timing Path Logic                             | 3-3  | 4.3.13    | Write Enable (WREN)                 | 4-2 |

| 3.3.3   | Data Path Logic                               | 3-3  | 4.3.14    | Write (WRT) Data                    | 4-2 |

| 3.3.4   | Read/Write Electronics                        | 3-4  | 4.3.15    | Phase-Locked Clock (PLC)            | 4-2 |

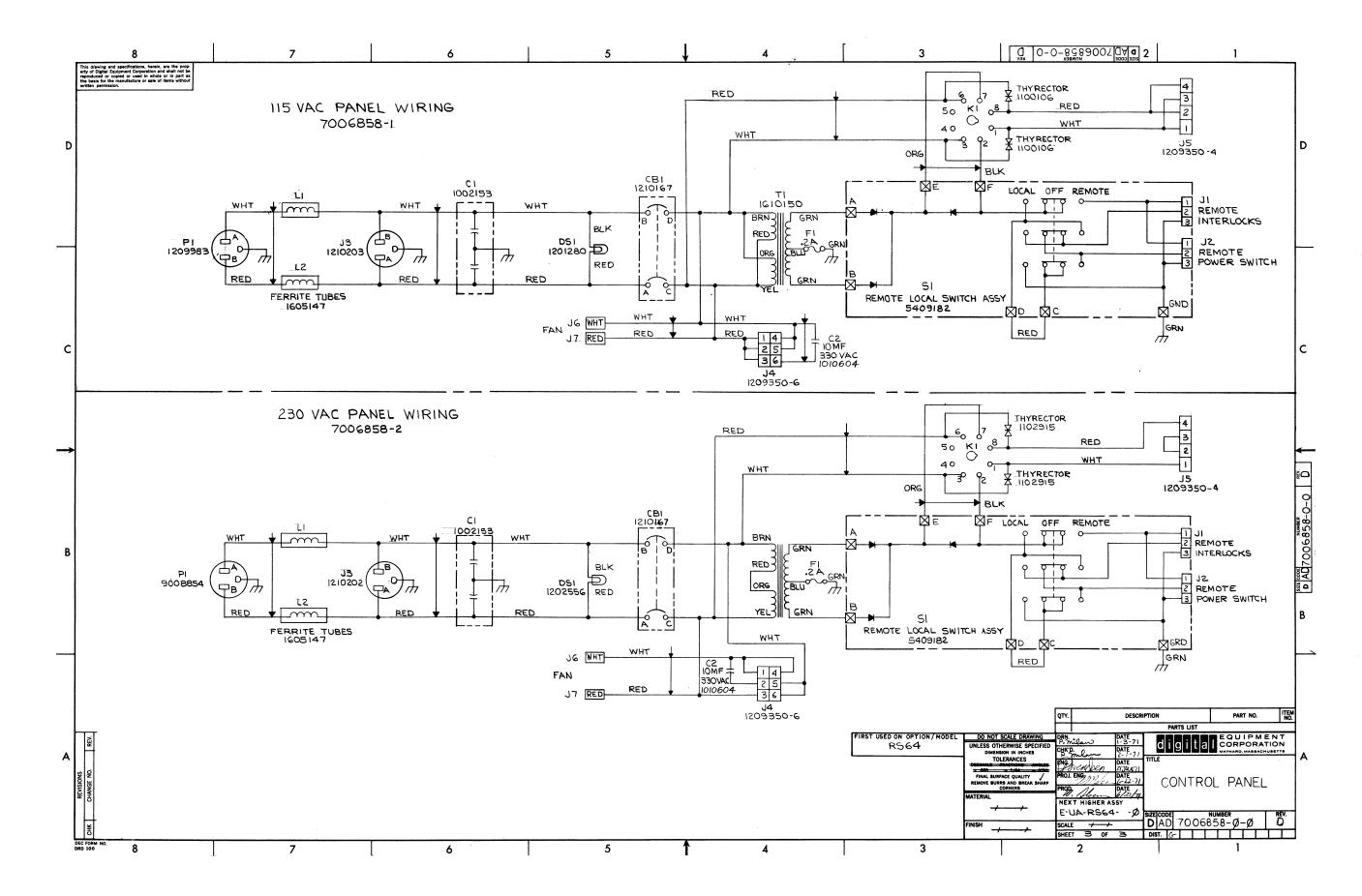

| 3.3.5   | Power Control Panel                           | 3-5  | 4.3.16    | Master Clear (M CLR)                | 4-2 |

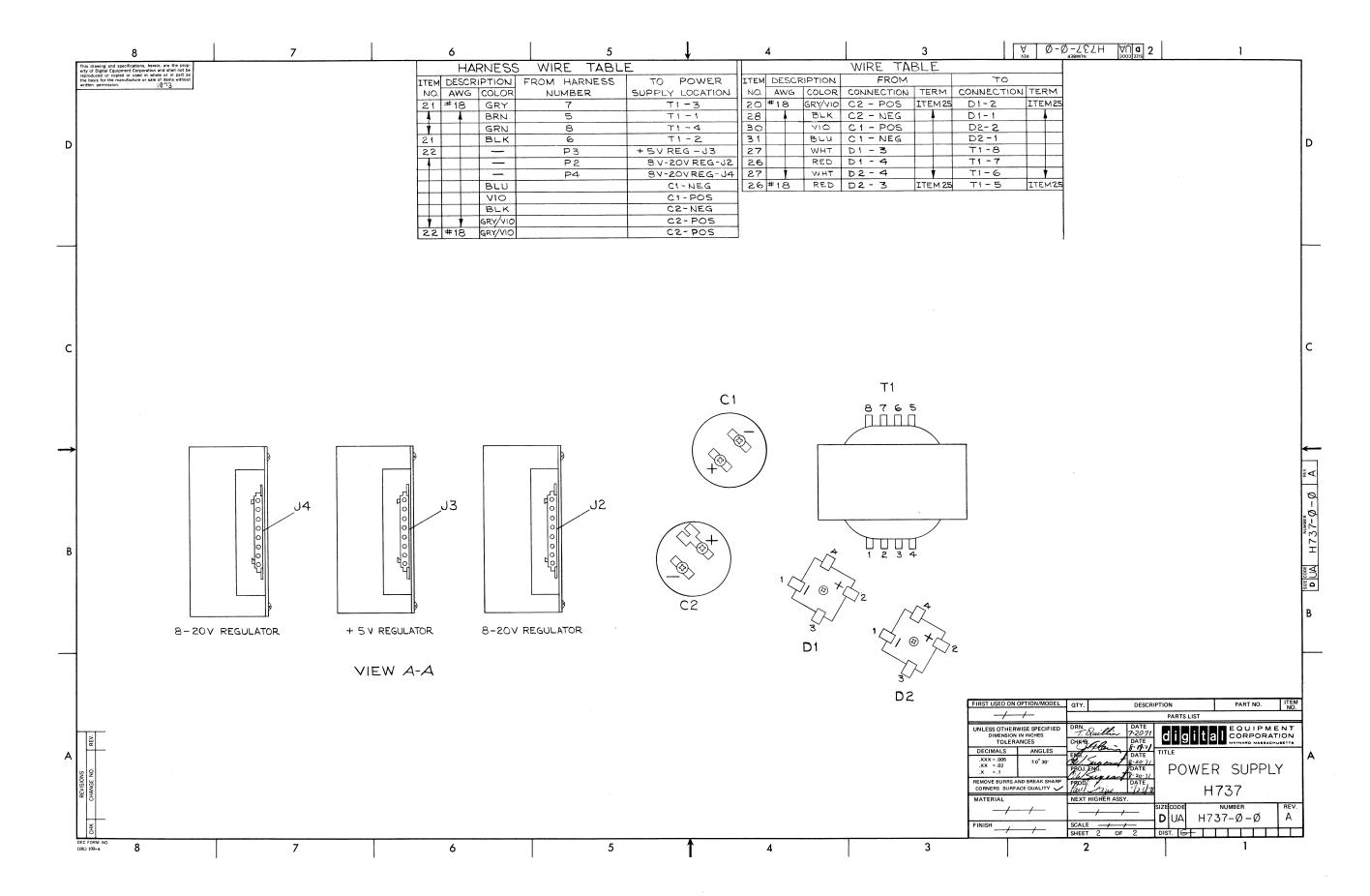

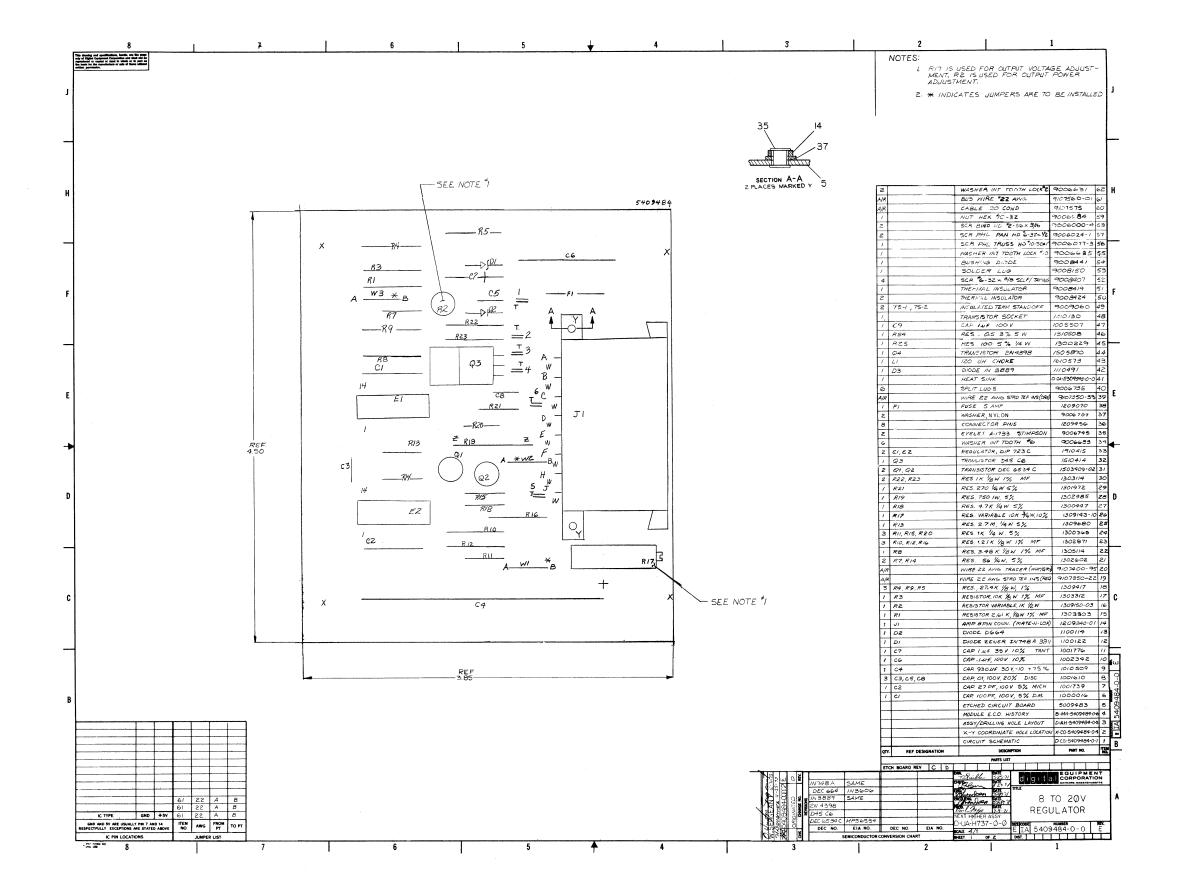

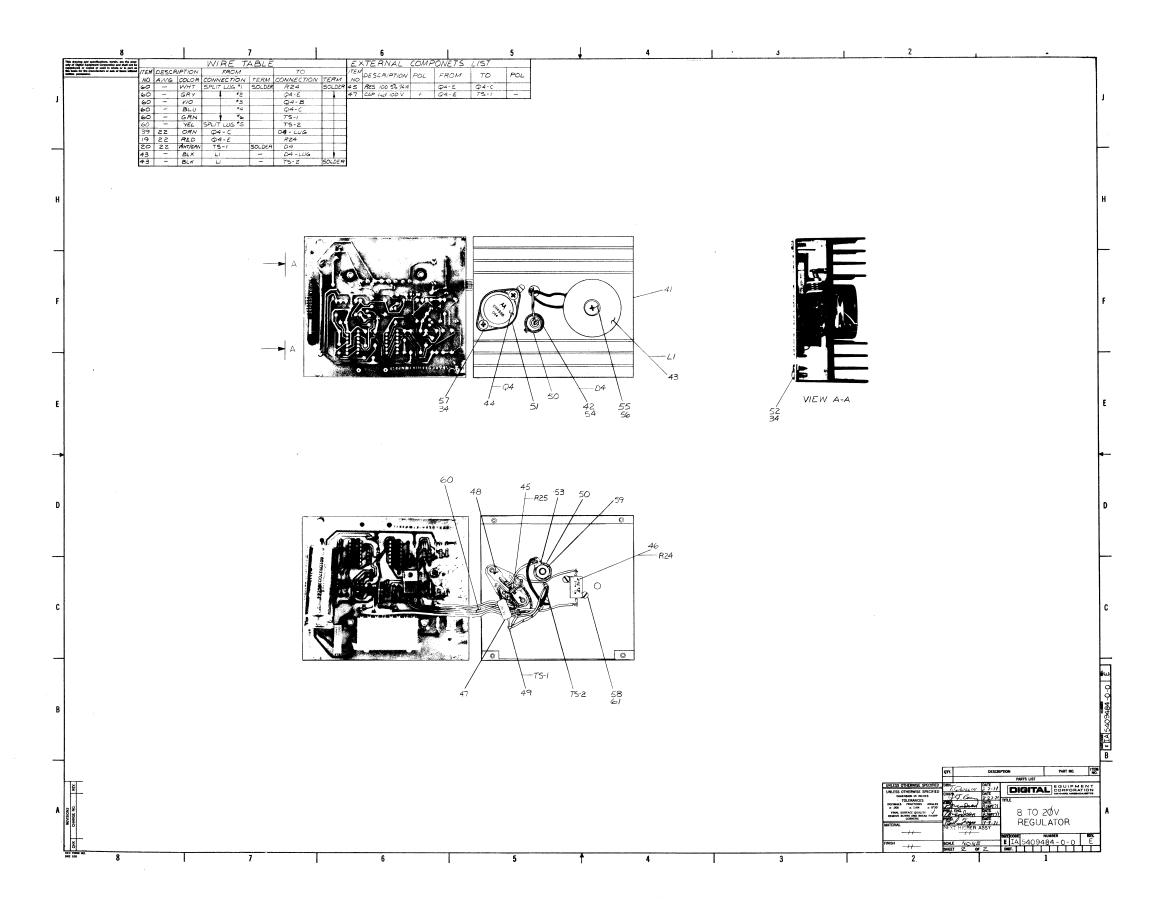

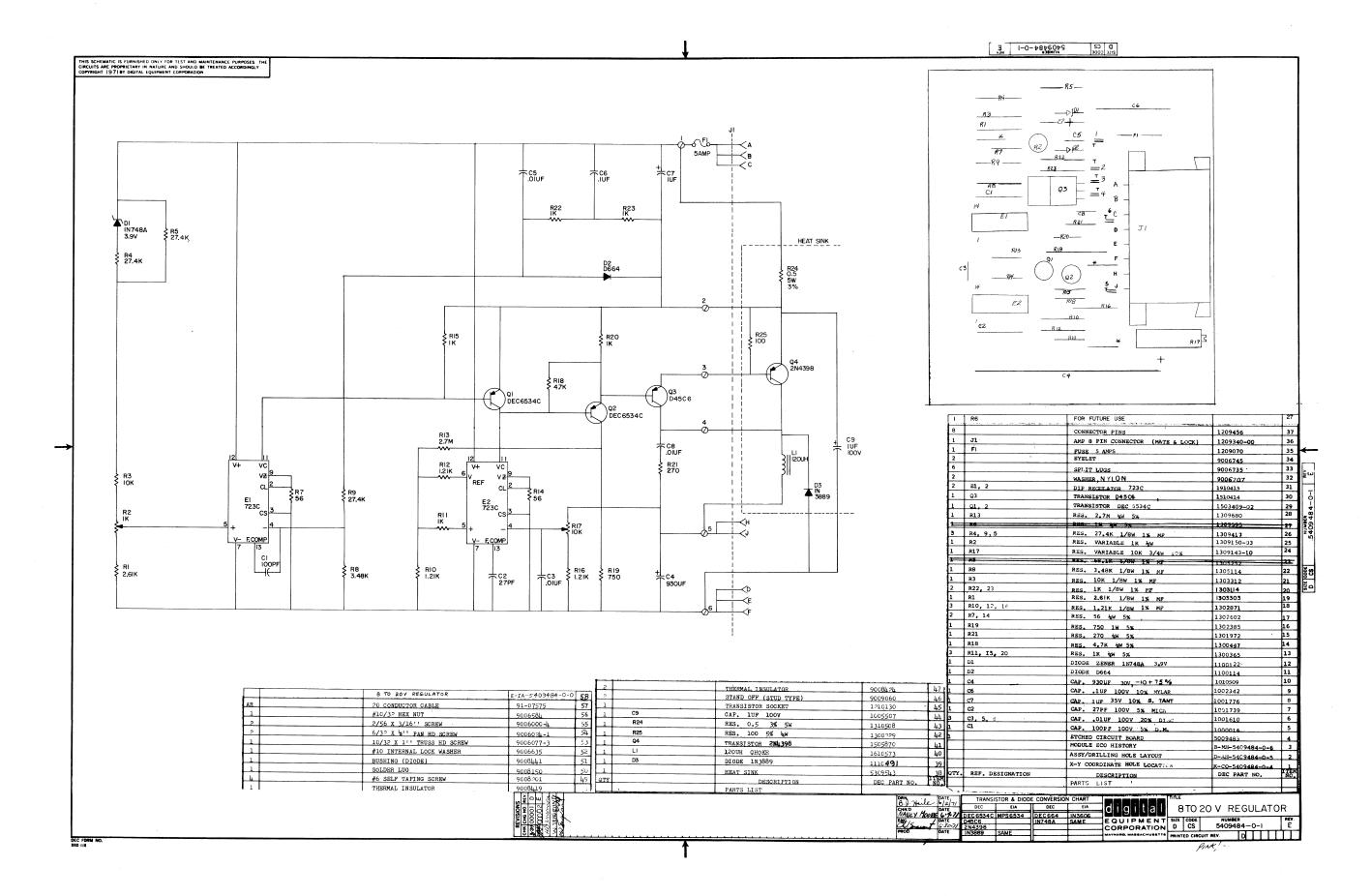

| 3.3.6   | Power Supply                                  | 3-5  | 4.3.17    | AC Low (AC LO)                      | 4-3 |

| 3.4     | Module Descriptions                           | 3-5  | 4.4       | Format Requirements                 | 4-3 |

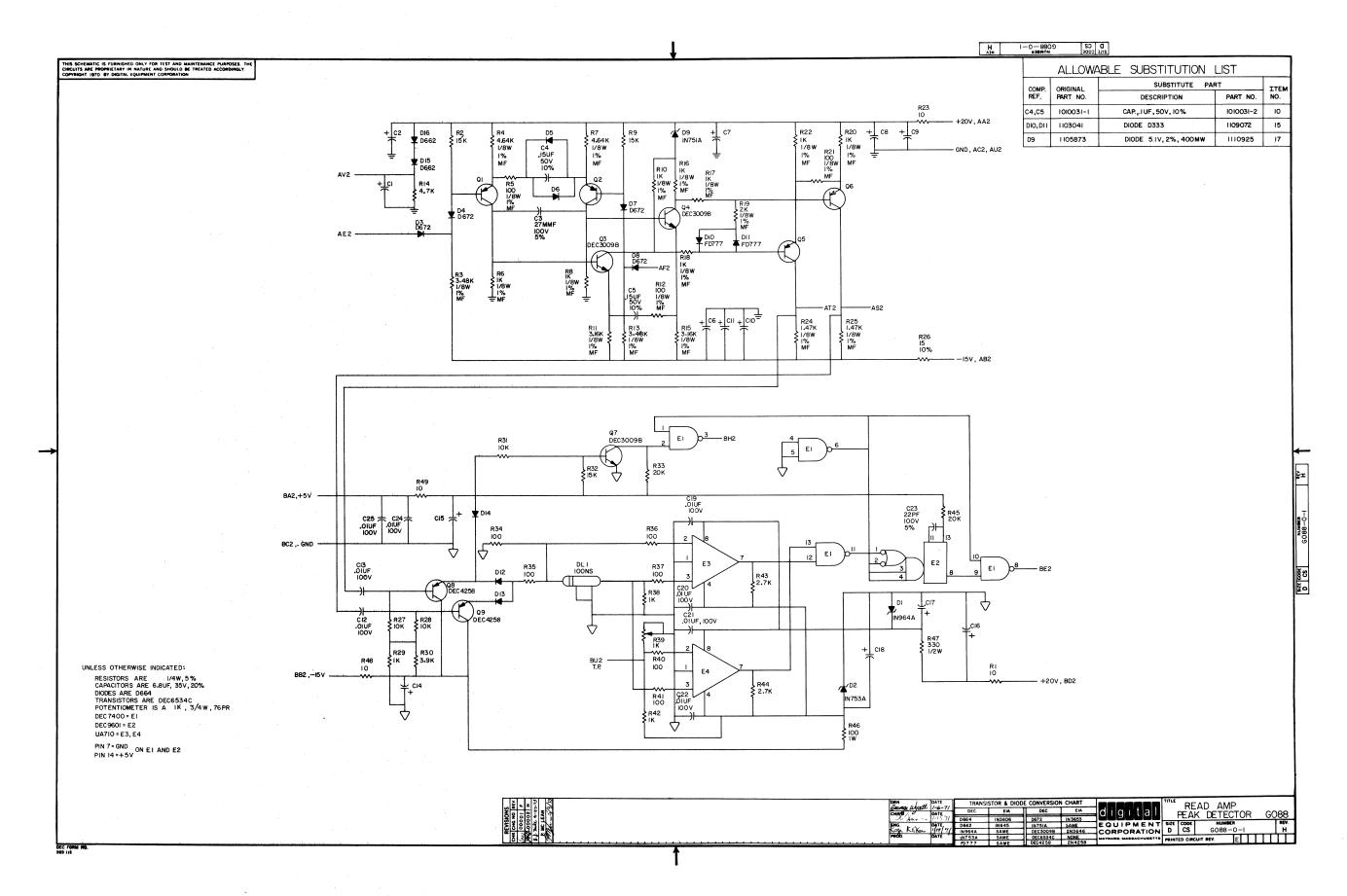

| 3.4.1   | G088 Read Amplifier-Peak Detector             | 3-5  | 4.5       | Synchronizing Logic                 | 4-3 |

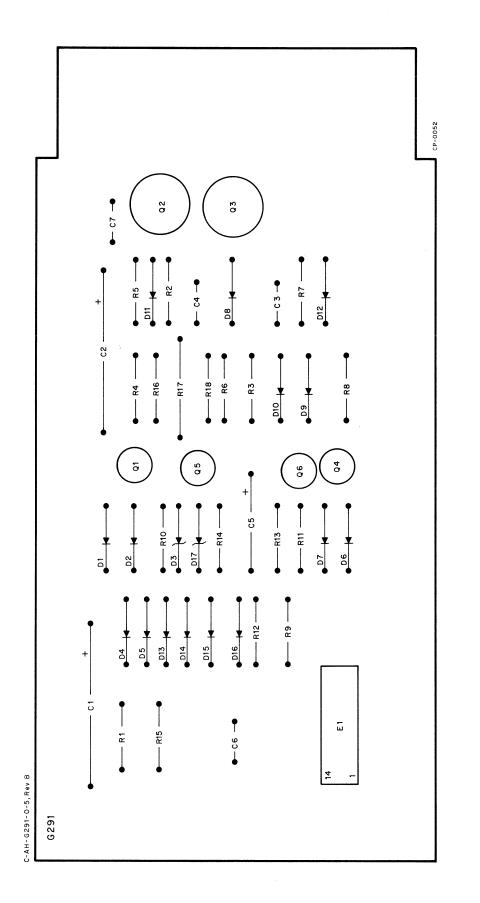

| 3.4.2   | G291 Disk Writer                              | 3-6  | 4.5.1     | Write Synchronization               | 4-3 |

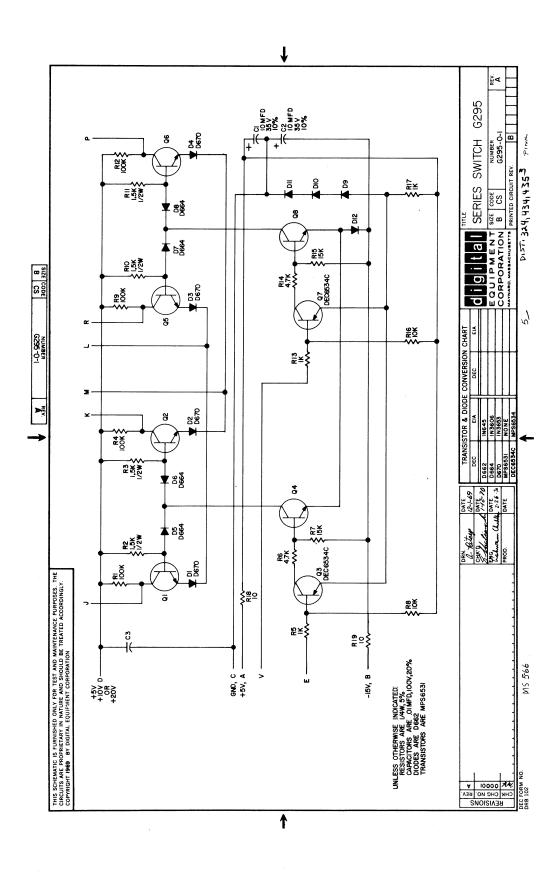

| 3.4.3   | G295 Series Switch                            | 3-6  | 152       | Read Synchronization                | 4-3 |

### **CONTENTS** (cont)

| CHAPTER 5 MAINTENANCE |                                                  | Page        | Figure No. | Title                                                  | Page  |

|-----------------------|--------------------------------------------------|-------------|------------|--------------------------------------------------------|-------|

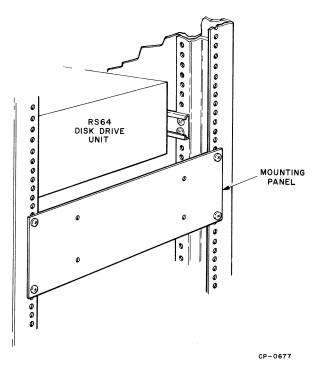

| 5.1                   | General                                          | 5-1         | 2-4        | Power Supply Mounting Panel                            | 2-4   |

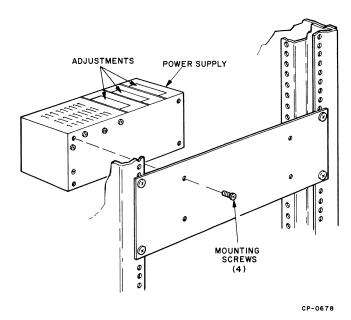

| 5.2                   | Recommended Test Equipment                       | 5-1         | 2-5        | Placement of Power Supply                              | 2-4   |

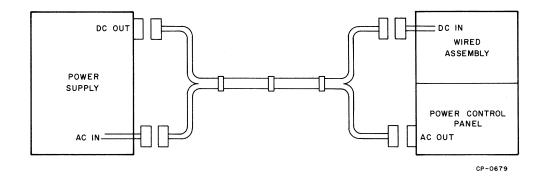

| 5.3                   | Preventive Maintenance                           | 5-1         | 2-6        | Extender Cabling Diagram                               | 2-4   |

| 5.4                   | Corrective Maintenance                           | 5-1         | 3-1        | RS64 System Relationships                              | 3-1   |

| 5.4.1                 | Module and Pin Designation                       | 5-1         | 3-2        | Disk Assembly with Cover Removed                       | 3-1   |

| 5.4.2                 | Power Control Panel Connector-Pin Identification | 5-1         | 3-3        | Disk Assembly with Head Shoes Exposed                  | 3-2   |

| 5.4.3                 | Power Supply Adjustments                         | 5-1         | 3-4        | Track Arrangement                                      | 3-2   |

| 5.4.4                 | Read Amplifier-Peak Detector Adjustments         | 5-3         | 3-5        | RS64 Functional Block Diagram                          | 3-3   |

| 5.4.5                 | Timing Track Changeover                          | 5-4         | 3-6        | Counter Timing Relationships                           | 3-3   |

| 5.4.6                 | Rewriting Timing Tracks                          | 5-4         | 3-7        | Read/Write Electronics                                 | 3-4   |

| 5.4.7                 | Troubleshooting Recommendations                  | 5-4         | 3-8        | Write and Read Waveforms                               | 3-4   |

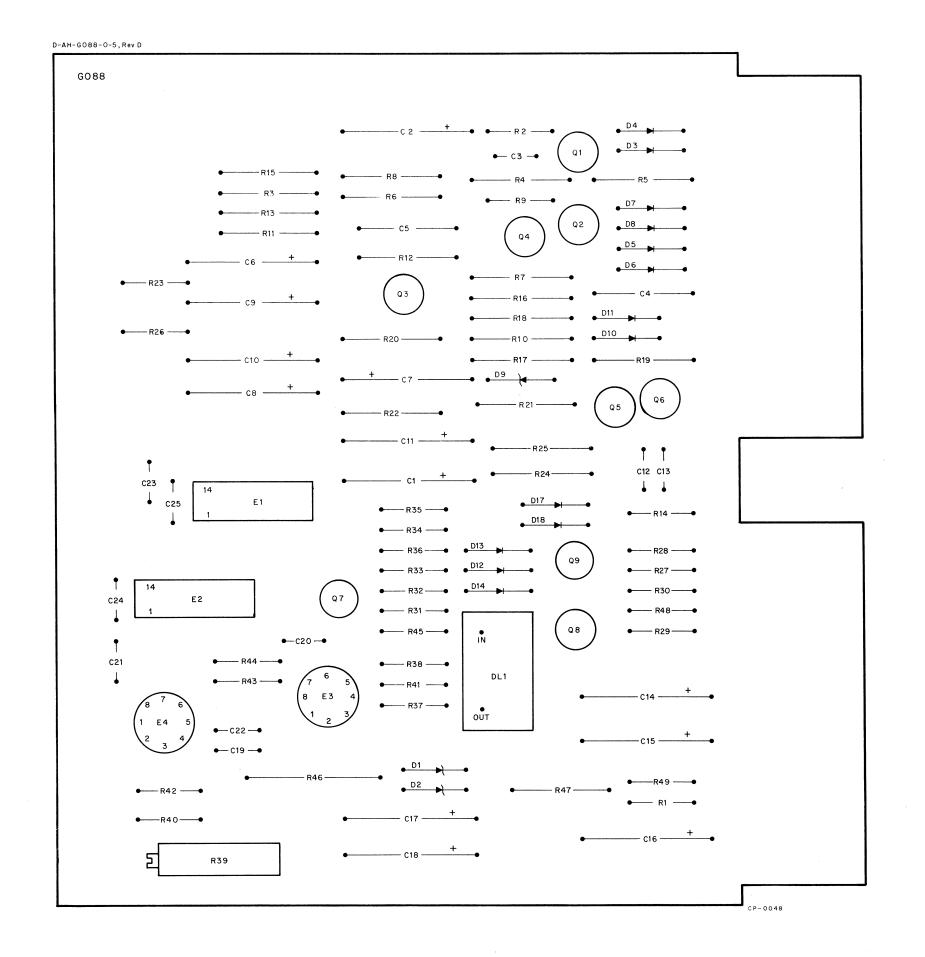

| 5.4.7.1               | General                                          | 5-4         | 3-9        | G088 Read Amplifier-Peak Detector Simplified Diagram   | 3-5   |

| 5.4.7.2               | Track Address Errors                             | 5-5         | 3-10       | G088 Read Amplifier-Peak Detector Waveforms            | 3-5   |

| 5.4.7.3               | Sector Address Errors                            | 5-5         | 3-11       | G291 Disk Writer Simplified Diagram                    | 3-6   |

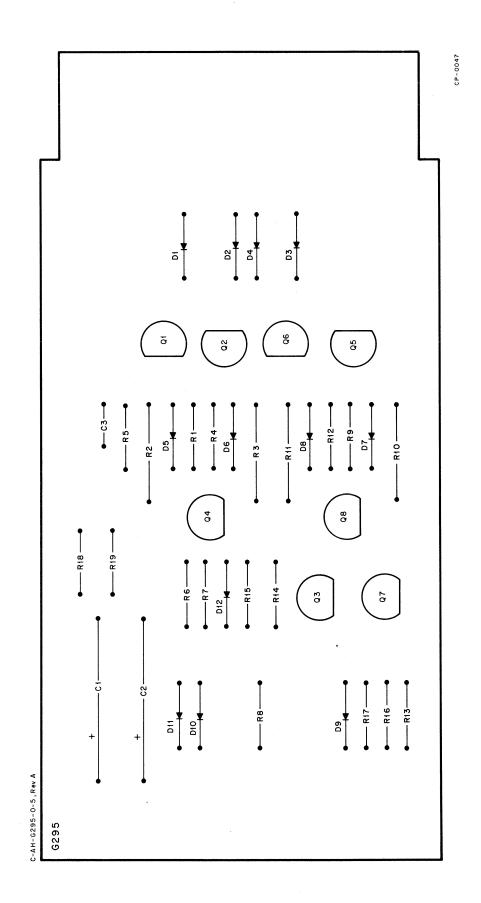

| 5.4.7.4               | Timing Errors                                    | 5-5         | 3-12       | G295 Series Switch Simplified Diagram                  | 3-6   |

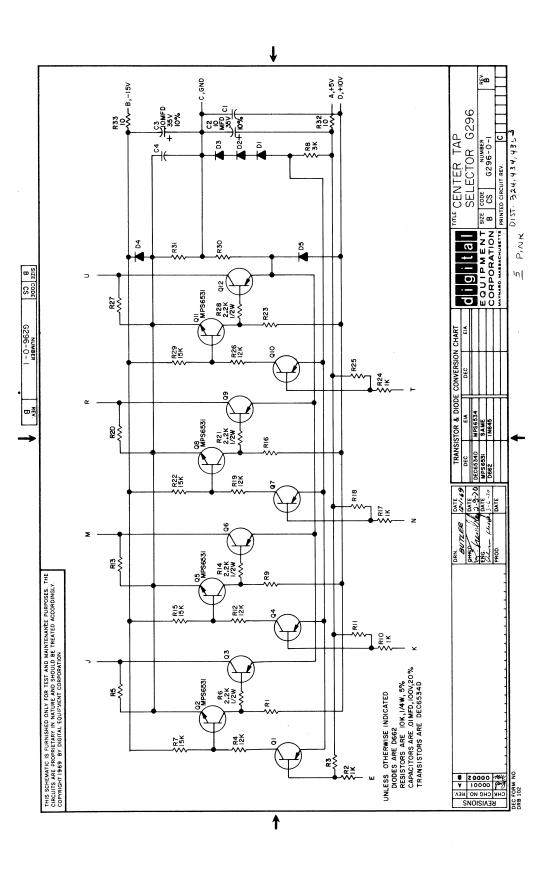

| 5.4.7.5               | Data Errors                                      | 5-6         | 3-13       | G296 Center Tap Selector Simplified Diagram            | 3-7   |

| 5.5                   | Removal and Replacement                          | 5-6         | 3-14       | M163 Decoder Simplified Diagram                        | 3-8   |

| 5.5.1                 | Removal of Disk Assembly                         | 5-6         | 3-15       | M167 Comparator Simplified Diagram                     | 3-9   |

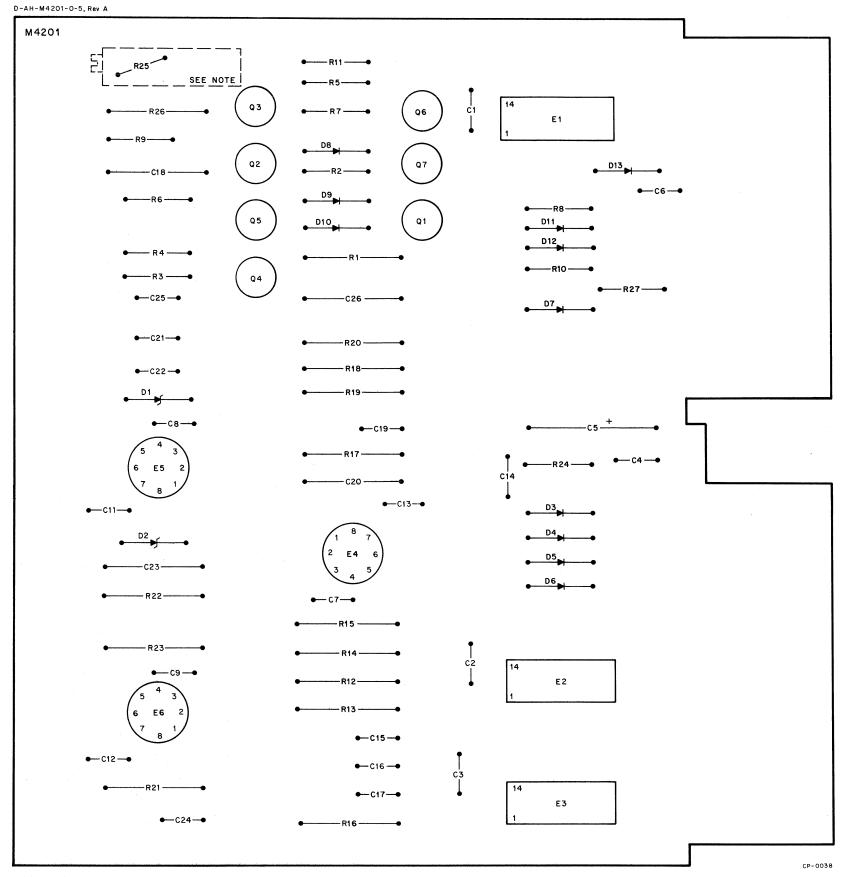

| 5.5.2                 | Reinstallation of Disk Assembly                  | 5-7         | 3-16       | M4201 Phase-Locked Clock Simplified Diagram            | 3-10  |

| 5.6                   | Recommended Spare Parts                          | 5-7         | 3-17       | M4201 Phase-Locked Clock Waveforms                     | 3-10  |

|                       |                                                  |             | 4-1        | Voltage Spectrum for Controller Bus                    | 4-1   |

| CHAPTER 6             | DRAWINGS AND MNEMONIC GLOSSARY                   |             | 4-2        | "Fast" Bus Configuration                               | 4-1   |

|                       |                                                  |             | 4-3        | "Slow" Bus Configuration                               | 4-1   |

| APPENDIX A            | A RC11 FORMAT AND RS64 TIMING TRACK WRITER       |             | 4-4        | RS64 Controller Interface                              | 4-2   |

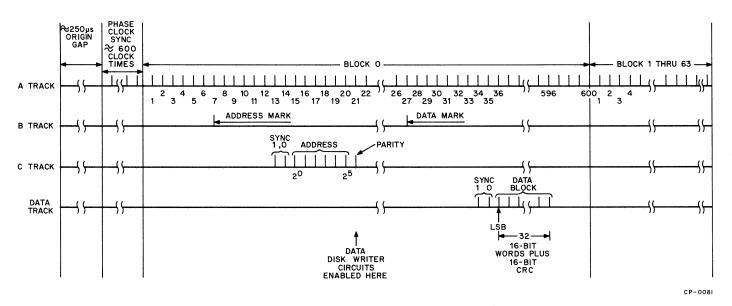

| A.1                   | RC11 Format                                      | A-1         | 4-5        | Write Synchronization                                  | 4-4   |

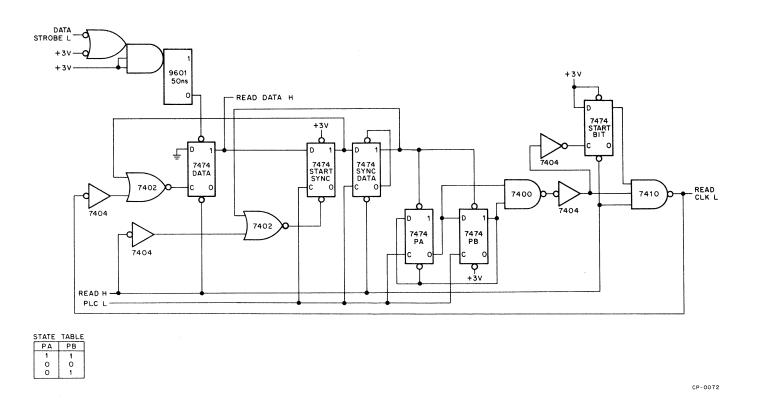

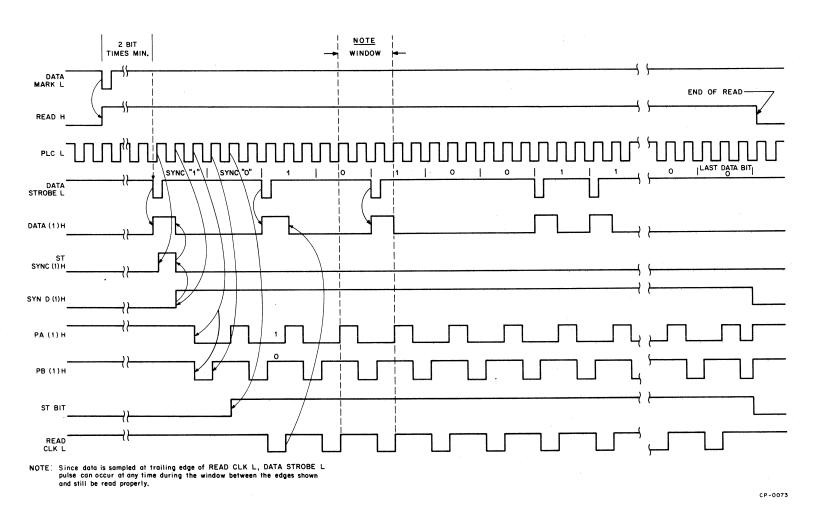

| A.1.1                 | Data Organization                                | A-1         | 4-6        | Read Synchronizing Interface Logic                     | 4-4   |

| A.1.2                 | Disk Timing Tracks                               | A-1         | 4-7        | Read Synchronizing Interface Timing                    | 4-5   |

| A.1.3                 | Addressing Data on Disk                          | A-1         | 5-1        | Module and Pin Designations                            | • 5-2 |

| A.1.4                 | Address and Data Demarkation                     | A-1         | 5-2        | Power Control Panel Connector-Pin Identification       | 5-3   |

| A.1.5                 | Controller Clocking                              | A-1         | 5-3        | Power Supply Adjustments and Connector Pin Assignments | 5-3   |

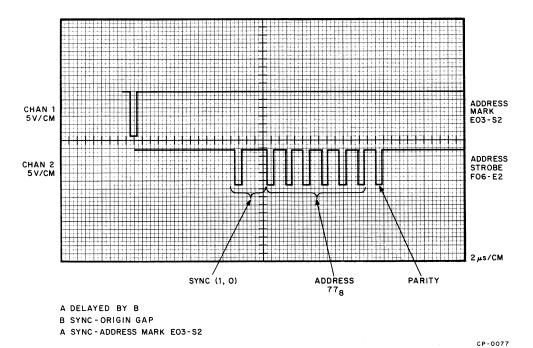

| A.1.6                 | Disk Track Format                                | A-2         | 5-4        | Address Mark and Address Strobe                        | 5-5   |

| A.2                   | RS64 Timing Track Writer                         | <b>A-</b> 2 | 5-5        | Address Strobe and Analog Signal                       | 5-5   |

|                       |                                                  |             | 5-6        | Clock Timing Signals                                   | 5-6   |

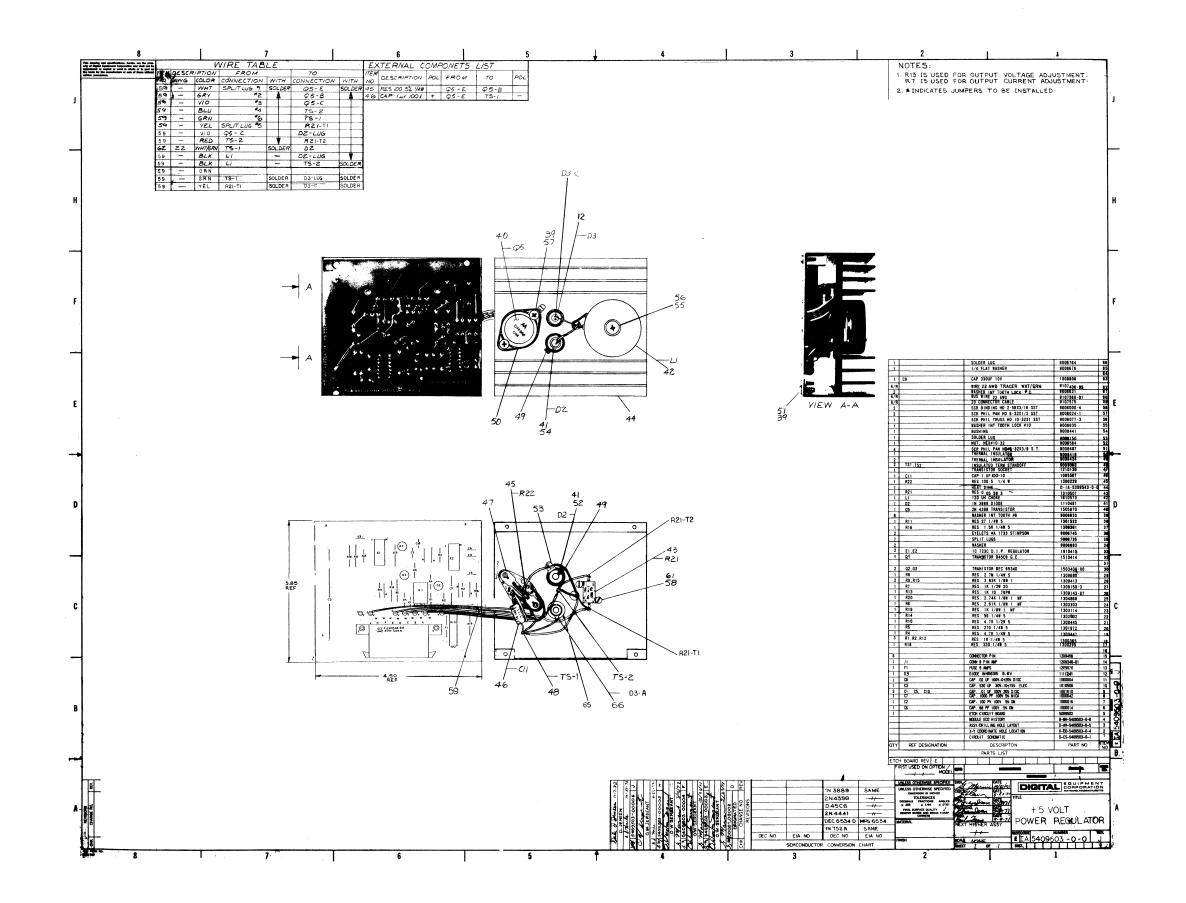

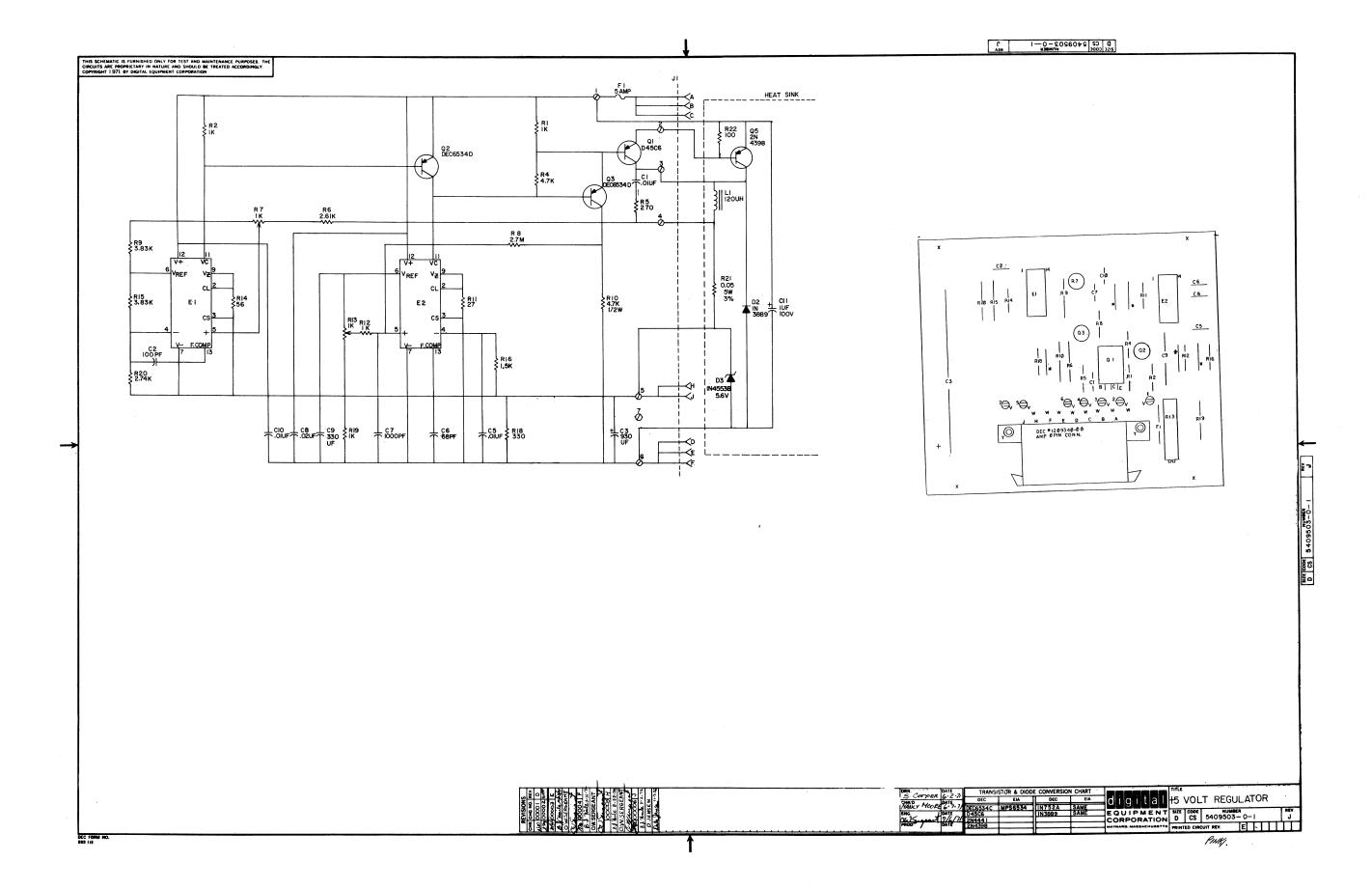

| APPENDIX E            | B POWER SUPPLY                                   |             | 5-7        | WRT Data and DSL Relationships                         | 5-6   |

| LLUST                 | RATIONS                                          |             |            |                                                        |       |

| Figure No.            | Title                                            | Page        | TABLES     |                                                        |       |

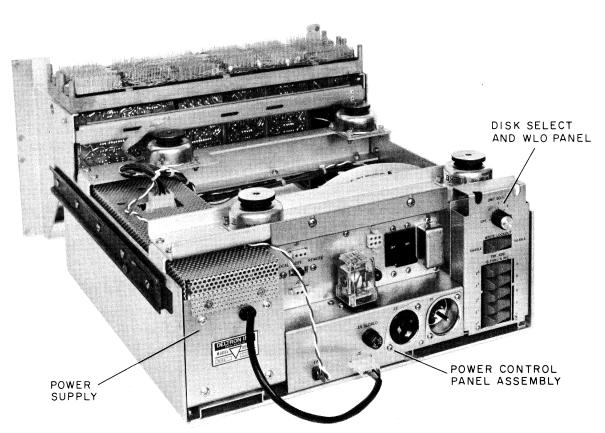

| 1-1                   | RS64 Disk File                                   | 1-1         | Table No.  | Title                                                  | Page  |

| 1-2                   | RS64 Disk File Major Assemblies                  | 1-2         | <i>~</i> . |                                                        | ı ugc |

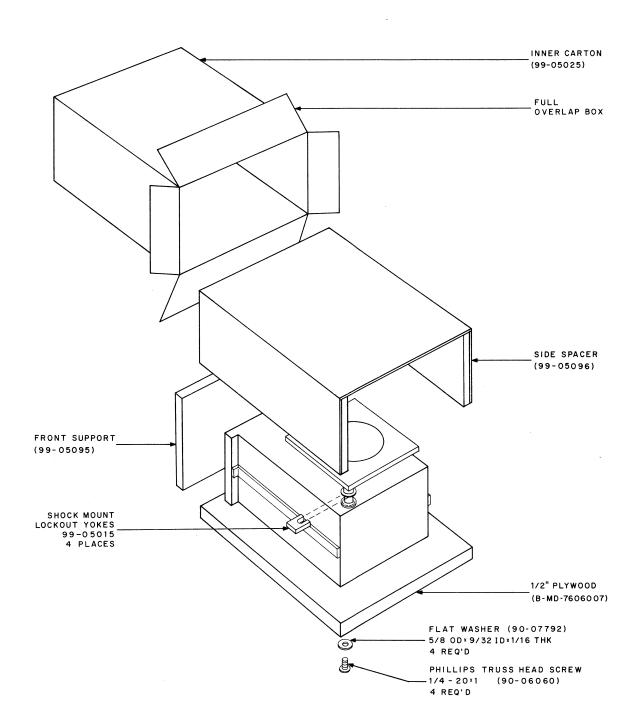

| 1-3                   | Power and Control Logic Assembly                 | 1-2         | 5-1        | Recommended Test Equipment                             | 5-1   |

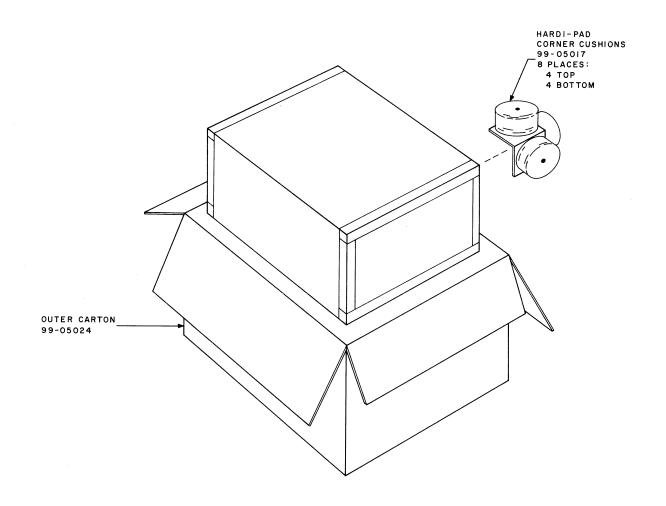

| 2-1                   | RS64 Disk File Packaging                         | 2-2         | 5-2        | Recommended Spare Parts                                | 5-7   |

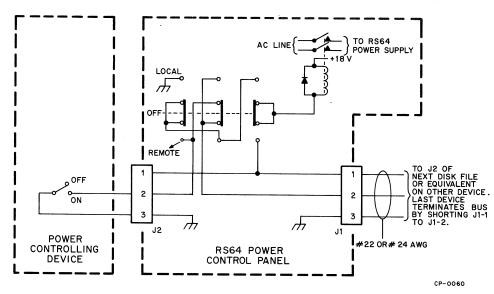

| 2-2                   | Remote Control and Interlock Connections         | 2-3         | 6-1        | Drawings                                               | 6-1   |

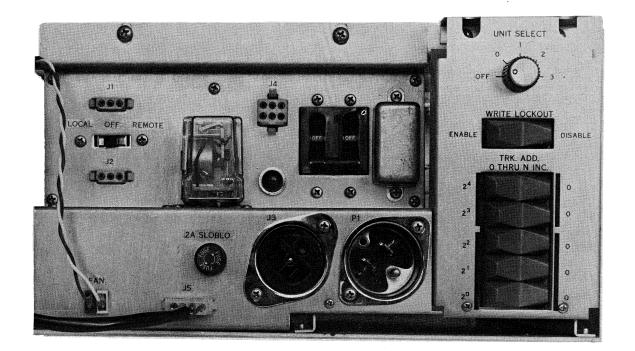

| 2-3                   | Power Control and WLO Panel                      | 2-3         | 6-2        | Signal Glossary                                        | 6-2   |

|                       |                                                  |             |            |                                                        |       |

### CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual contains instructions for interfacing, installing, operating, and maintaining the RS64 Disk File manufactured by Digital Equipment Corporation (DEC), Maynard, Massachusetts. The instructions are intended for maintenance personnel with a basic understanding of disk files but who may not necessarily be familiar with the RS64 Disk File.

The instructions are arranged in six primary divisions: General Description, Installation and Operation, Theory of Operation, Interfacing, Maintenance, and Drawings. Two appendices are also provided; (a) track writer format and relationships, and (b) the power supply.

In addition to this manual, the following documents contain information relevant to the RS64 Disk File:

- a. DEC Logic Handbook, 1970, C105

- b. Special Maintenance Procedures for Disks, DEC-SP-DISK-DA.

#### 1.2 PURPOSE AND APPLICATION INFORMATION

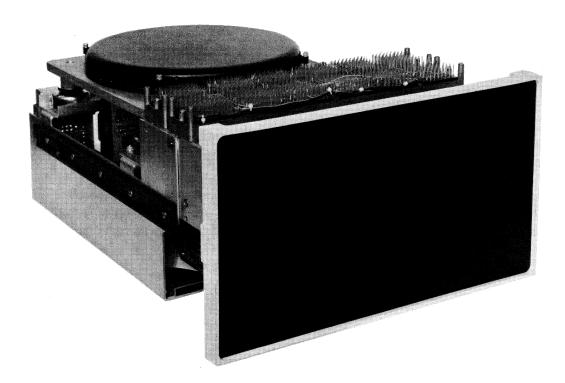

The RS64 Disk File, Figure 1-1, is a fast, random-access file that provides up to 1,280,000 bits of storage. With the disk select logic provided in each disk file, up to four RS64 Disk Files can be operated from one controller, thus providing a storage capability of up to 5,120,000 bits.

The RS64 is designed for standard 19-in. rack mounting. It is furnished with disk assembly and modularized read/write electronics contained in a slide-mounted chassis that requires 10-1/2 in. of front panel height. The power supply is mounted on the rear of the cabinet, separate from the drive chassis. Two basic models are available; the RS64A operates with 115V, 47 to 63 Hz primary power and the RS64B operates with 230V, 47 to 63 Hz primary power.

The disk assembly contains a 10-in. nickel-cobalt plated disk that is driven by an induction motor at approximately 1400 (50 Hz) or 1800 (60 Hz) rpm. Data is recorded on a single disk surface using 32 fixed read/write heads. Other features include a highly reliable, self-synchronizing clock recovery system and write protection (write lockout) for the data tracks. Three spare timing tracks are also provided.

Pertinent interfacing and design criteria, plus recommended controller interface circuits, are provided in this manual. In addition, the RS64 Power Supply is capable of providing a controller with up to 4.5A at +5V.

#### 1.3 PHYSICAL DESCRIPTION

#### 1.3.1 General

The RS64 Disk File consists of two major assemblies: disk assembly RS64M, and power control and logic assembly RS64P. These assemblies and the elements comprising them are described in subsequent paragraphs.

Figure 1-1 RS64 Disk File

#### 1.3.2 RS64M Disk Assembly

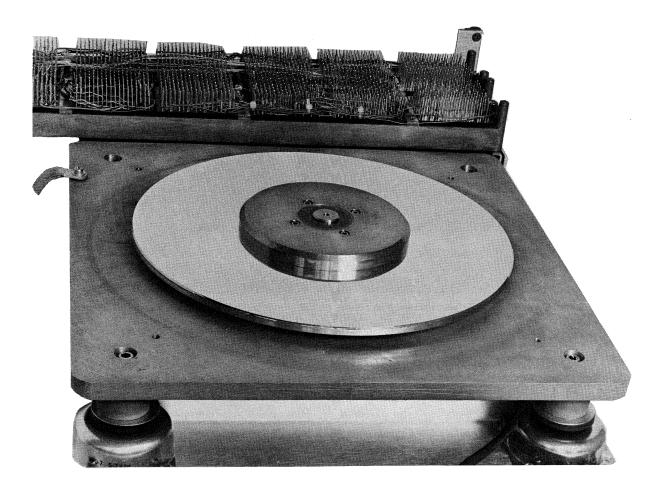

The disk assembly, Figure 1-2, consists of a 10-in. diameter nickel-cobalt plated aluminum disk, a drive motor, and five head assemblies mounted on a deck plate. The deck plate is supported by four shock mounts. A cover protects the disk and heads from dust and foreign particles. Data connections are made via connectors on the underside of the deck plate. A 4-wire power cord connects the drive motor to the RS64P power control and logic assembly.

#### 1.3.3 RS64P Power Control and Logic Assembly

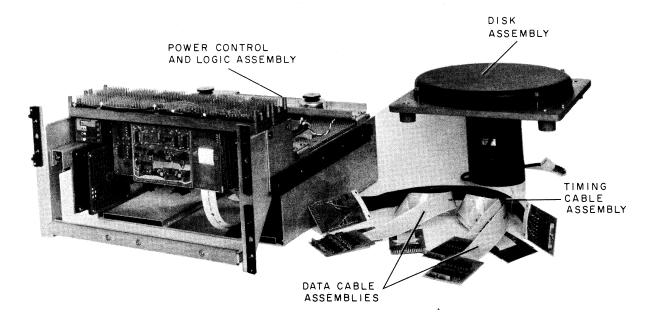

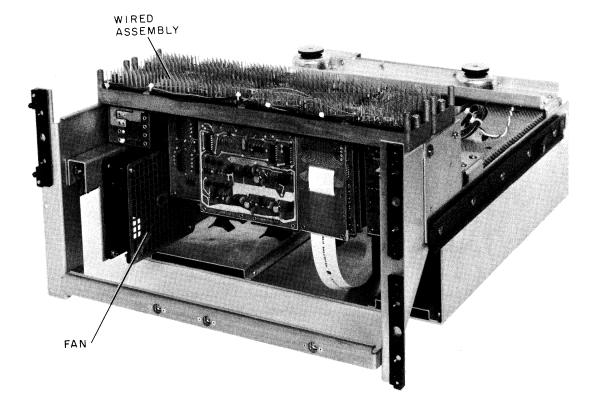

The power control and logic assembly, Figure 1-3, consists of a wired assembly for housing logic modules, a power control panel, a disk select and write lockout panel, and a power supply. It also includes two data cable assemblies and one timing cable assembly that convey signals between the disk assembly and the read/write electronics.

Figure 1-2 RS64 Disk File Major Assemblies\*

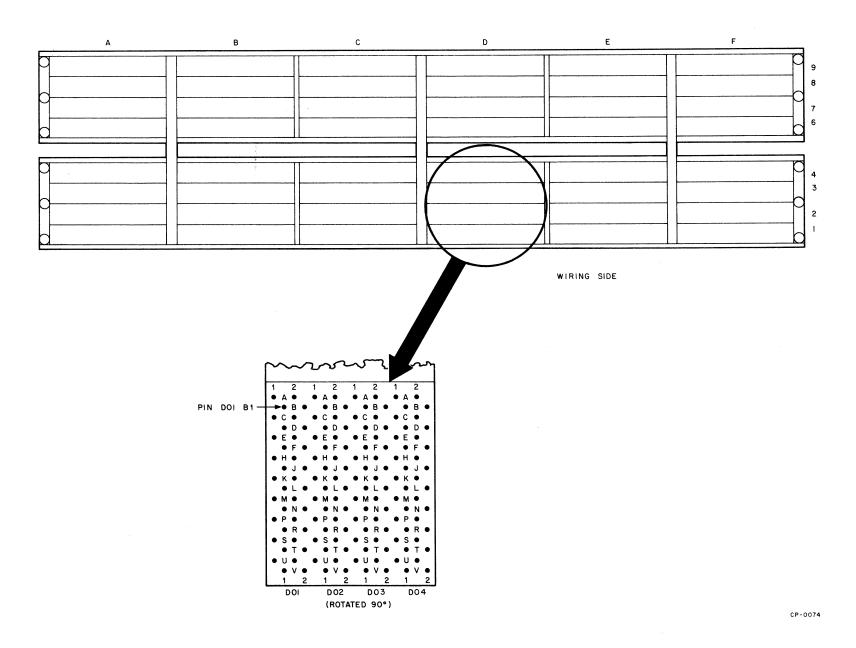

- 1.3.3.1 Wired Assembly The wired assembly contains the read/write modules and provides the connectors for the data and timing cables, the power supply extender cable, and the controller cables. The assembly consists of a logic frame that houses six connector blocks each capable of accepting eight single-height modules or four double height modules. Wire-wrap connections are used between connector blocks. A fan, located on the module side, provides forced-air cooling for the modules. The wired assembly is hinged at each end and can be rotated on its horizontal axis for convenient servicing.

- 1.3.3.2 Power Control Panel Assembly The power control panel assembly contains the receptacles for primary power connections, an RFI filter, and circuits for local/remote control of primary power. The assembly is attached to the chassis by four screws and can be removed readily for internal access. All electrical connections between the panel and other assemblies are made using connectors on the external portion of the assembly. The internal wiring of this assembly determines if the unit is used with 115V or 230V.

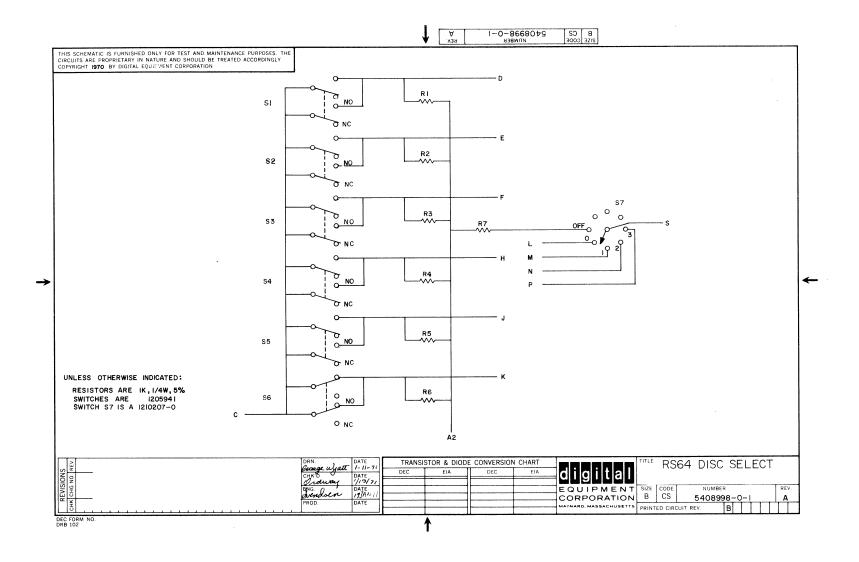

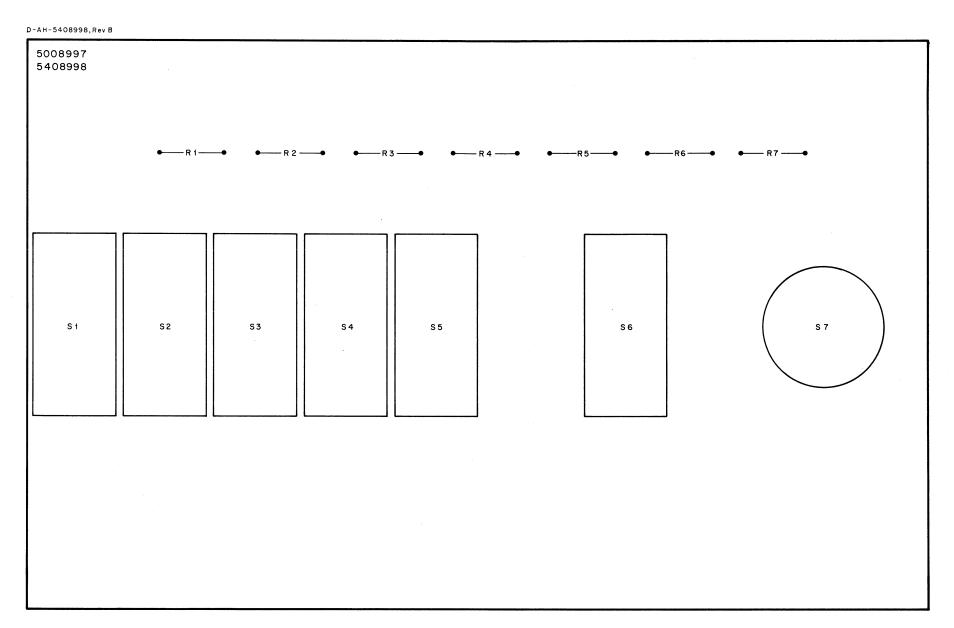

- 1.3.3.3 Disk Select and WLO Panel Assembly This assembly contains the controls for selecting disk unit assignment and track write protection (write lockout). A 5-position rotary switch is used for disk file assignment (0 through 3) and for placing the unit off-line (OFF). Five rocker switches are used for the write lockout function. The upper rocker switch enables or disables the write lockout function. With this switch in the enable position, all tracks from 00 through the track number selected by the other four rocker switches are write protected. The rotary switch and the five rocker switches are mounted on a PC module located behind the panel. A flat Mylar cable connects this assembly to the wired assembly.

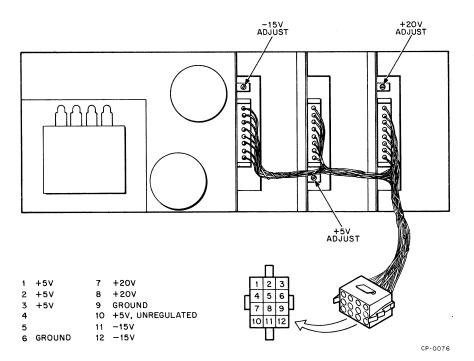

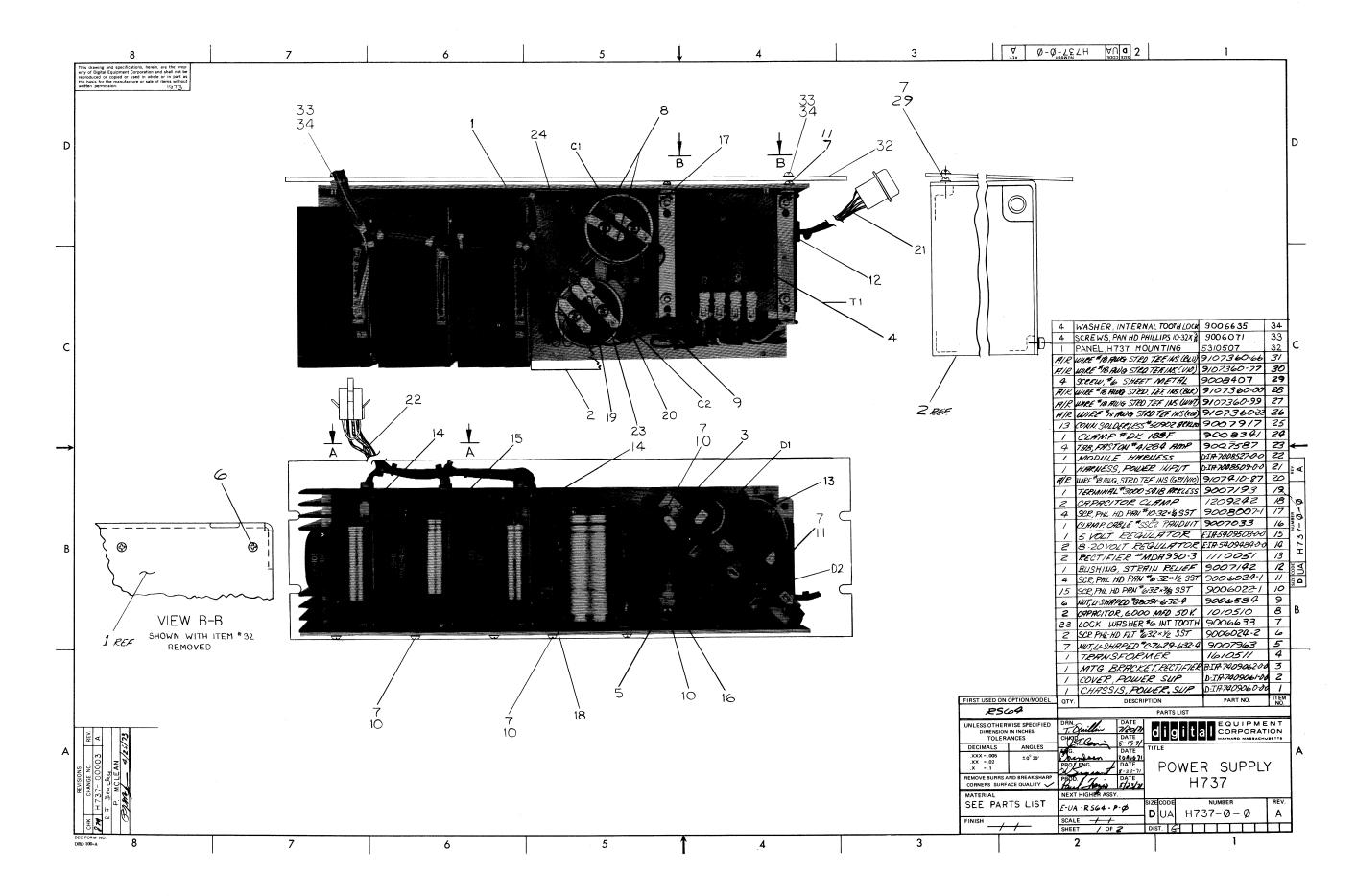

#### 1.3.3.4 Power Supply

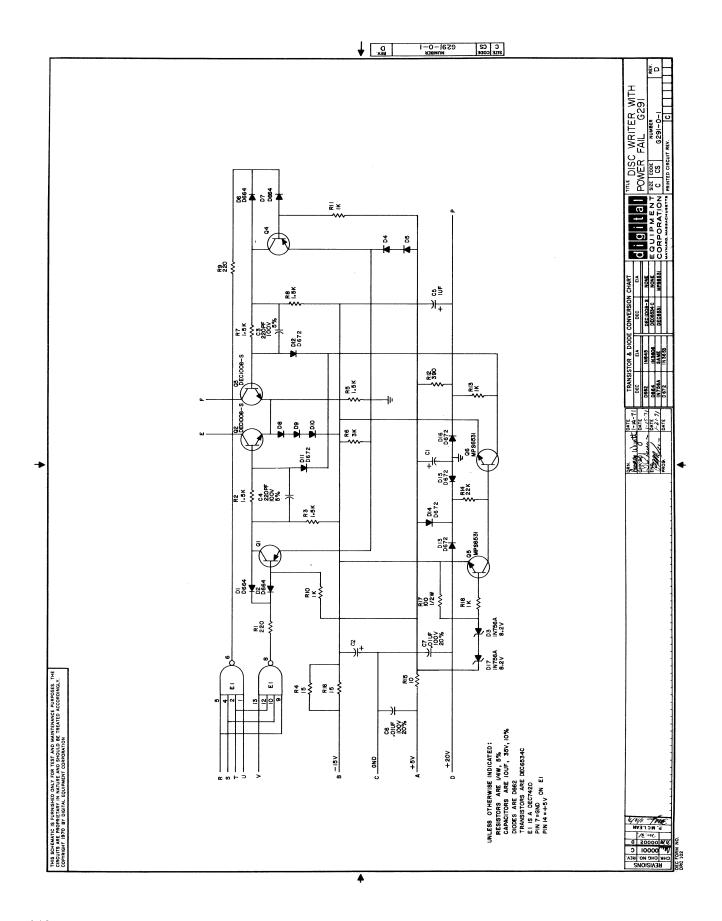

The power supply is located on the rear of the cabinet (Figure 2-5). The supply provides -15V, +5V and +20V for the read/write electronics. A power supply extender cable is used to connect the power supply and the main chassis of the drive unit. Primary ac power is routed from the power control panel to the supply via the extender cable. The dc output from the supply is routed to the wired assembly also via the extender. See Figure 2-6 for power supply cabling. Additional power supply information is given in Appendix B.

Figure 1-3 Power and Control Logic Assembly\*

<sup>\*</sup>The Power Supply has been removed from the main chassis and located on the rear of the cabinet (Figure 2-5).

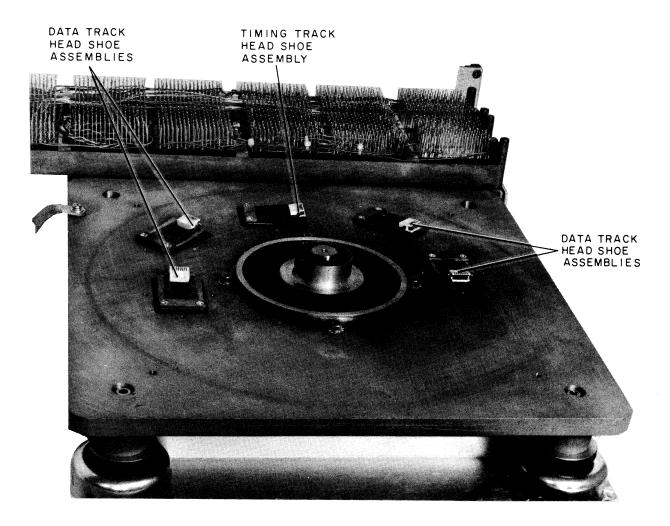

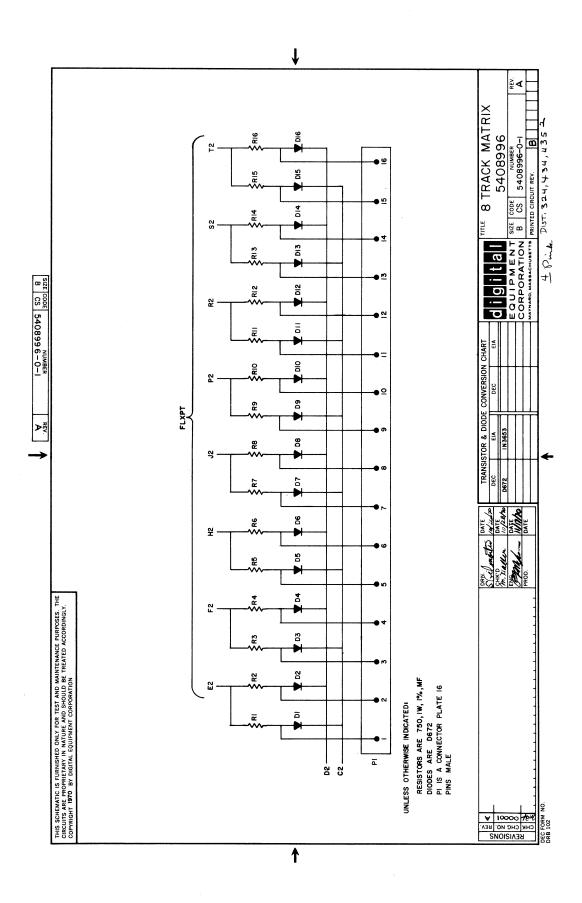

1.3.3.5 Data and Timing Cable Assemblies – Two flat Mylar data cable assemblies (Figure 1-2) interconnect the data track heads with the read/write logic. Each data cable assembly handles the signals for two head shoe assemblies; it has two 8-track matrix-connector modules at the head end. One timing matrix cable assembly (Figure 1-2) interconnects the timing heads with the read/write logic. This cable has a 6-track matrix module at the disk end and a connector module at the logic end.

#### 1.4 SPECIFICATIONS

| Storage Medium   | 10-in. diameter nickel-cobalt plated disk with proprietary protective coating |                 |

|------------------|-------------------------------------------------------------------------------|-----------------|

| Storage Capacity | Up to 1,280,000 bits                                                          |                 |

| Access Time      | 60 Hz Power                                                                   | 50 Hz Power     |

| Minimum          | 260 μs                                                                        | 260 μs          |

| Average          | 16.9 ms                                                                       | 20.3 ms         |

| Maximum          | 33.6 ms                                                                       | 40.3 ms         |

| Data Tracks      | 32                                                                            |                 |

| Bits Per Track   | Up to 40,000                                                                  |                 |

| Recording Method | Self-clocking one-                                                            | of-N, NRZI code |

| Bit Density      | 1700 bpi (maximum)                                                            |                 |

Timing Tracks 3 plus 3 spare

Write Protection Features 5 switches provide write protection on all binary track

addresses up to and including binary track address indi-

cated by switch selections.

Motor Bearing Life Expected operating life of at least 20,000 hours under a

standard computer operating environment.

115/230 Vac ±15%, single-phase, 47 to 63 Hz. Power Requirements

Starting current of 6A; nominal operating current of

2.2A.

Operating Environment 40°F to 125°F, ambient. Relative humidity of 20% to

10-1/2 in.

19 in.

80% (non-condensing).

-40°F to 135°F (non-condensing)

Storage and Shipping Environment

Physical Characteristics

Shock

Height Width Drive Chassis only Depth

Weight

Includes power supply

18-3/4 in. 64 lb

$5-20 \text{ Hz } 0.020 \text{ in. D.A. } 20-500 \text{ Hz } \pm 1.5 \text{g, any plane.}$ Vibration

> 5g's Halfsine, 10 ms duration, any plane. Suitable for office, industrial, and large vessel operation.

|  |  | • |  |  |

|--|--|---|--|--|

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

|  |  |   |  |  |

# CHAPTER 2 INSTALLATION AND OPERATION

#### 2.1 UNPACKING AND INSPECTION

The RS64 Disk File can be shipped in a cabinet as an integral part of a system or separately in its own container for mounting in an existing cabinet. If a unit is shipped as a separate item, the power supply and the drive chassis will be shipped separately. Remove the items from the container, remove packing materials (Figure 2-1), and inspect for shipping damage. Report any damage to the carrier. Retain packing materials for possible reshipment.

The RS64 is shipped with a motor lock installed to prevent rotation of the disk during shipment. In addition, four corosote shock mount yokes, Figure 2-1, prevent bottoming of the shocks during impact. These items *must not* be removed until the disk is correctly installed in a cabinet.

#### **CAUTION**

Exercise care in unpacking the unit. Do not drop unit or subject it to unreasonable impact.

If the RS64 Disk File is shipped in a cabinet, the unit is retained in place by shipping brackets located at the rear of the chassis. These brackets must be removed to extend the unit from the cabinet. Remove the shipping brackets and any packing materials and inspect the unit for shipping damage. Report any damage to the carrier.

#### **CAUTION**

Do not remove motor lock or shock mount shipping yokes until cabinet is in final installation location. Disk heads can be damaged if unit is moved without these items in place.

#### 2.2 MECHANICAL INSTALLATION

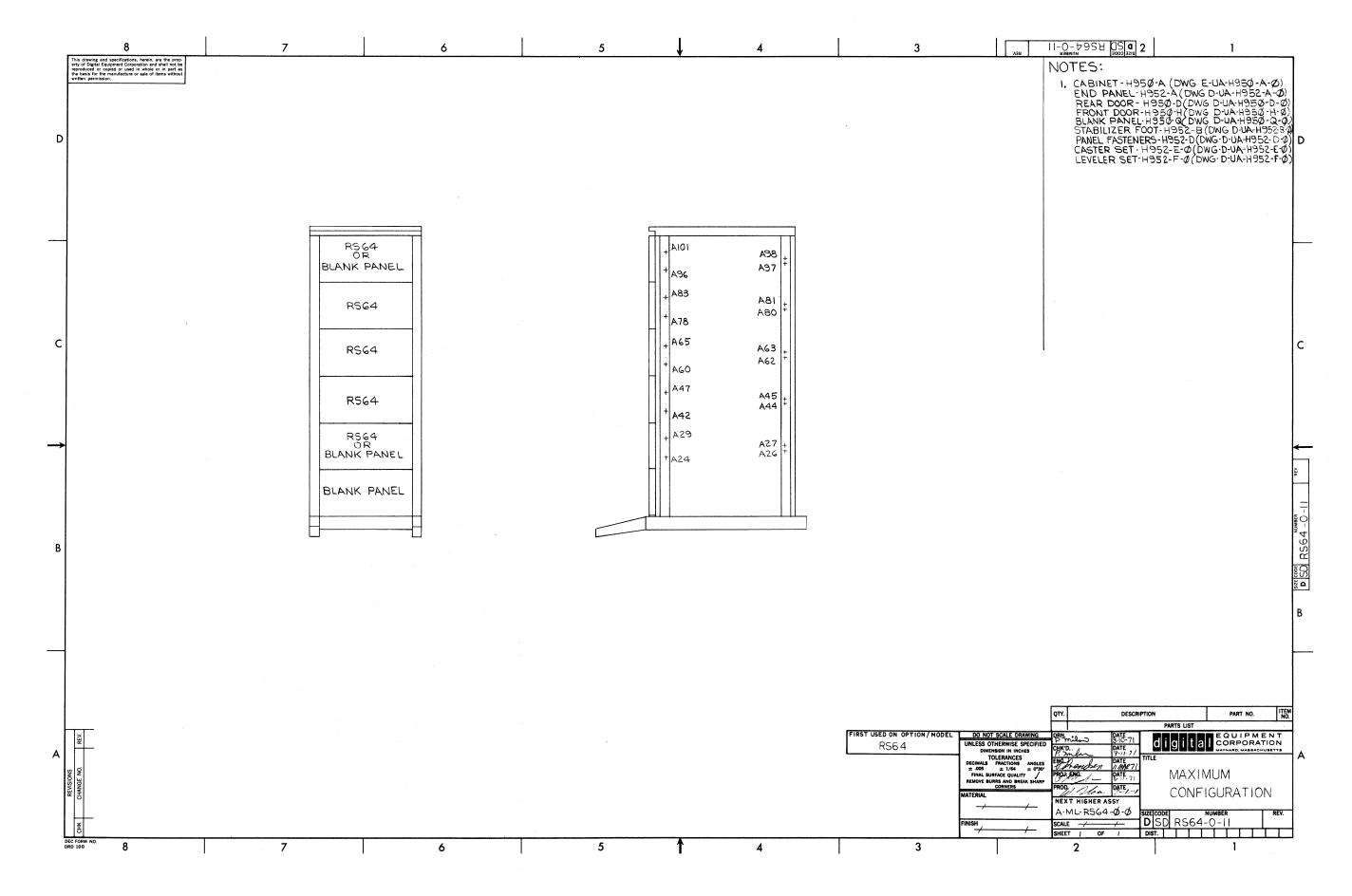

The RS64 Disk File is designed for 19-in. equipment rack mounting and requires 10-1/2 in. of front panel height. Up to four disk files can be installed in an H950 cabinet as shown in D-SD-RS64-0-11 (see Chapter 6).

If the RS64 is to be installed in an existing cabinet, it may be necessary to install the cabinet portion of the track slide assembly. Cabinet hardware ( $10-32 \times 3/4$  screws and 10-32 clip nuts) shipped with the file should be used to attach the track slide assembly to the cabinet.

Once the RS64 drive chassis is correctly mounted on track slides, extend the assembly and remove the four shock mount yokes used for shipping. Next, remove the motor lock on the bottom of the motor shaft. Retain these items and the shipping brackets (and the shipping container) for possible reshipment of disk.

The H737 Power Supply is mounted on the rear of the cabinet. To mount the power supply proceed as follows.

| Step | Procedure                                                                                                                                                                                                   |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | Attach mounting panel 5310507 to the rear of the cabinet with four mounting screws and speed nuts. Position the panel so the top edge is even with the lower edge of the drive unit chassis (Figure 2-4).   |  |

| 2    | Attach the H737 Power Supply to the panel with four mounting screws. The adjustments should be on top (Figure 2-5).                                                                                         |  |

|      | NOTE  If there is to be a second power supply mounted in this cabinet, or if this is the second supply, it should be attached to its mounting plate upside down so that the adjustments will be accessible. |  |

| 3    | Connect the power supply extender cable (7009380) between the power supply and the drive chassis.                                                                                                           |  |

| 4    | Attach the two Deklasp clamps (9008340), to the extender cable. Attach one clamp 3 inches and the other 11 inches from rear of drive chassis.                                                               |  |

#### 2.3 POWER REQUIREMENTS

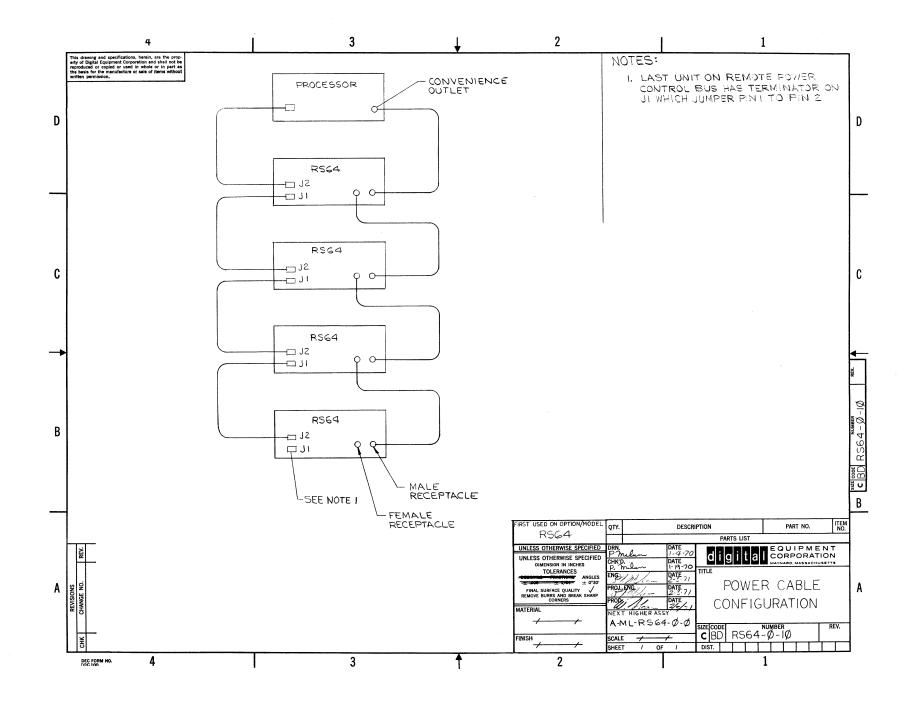

Model RS64A operates from a 95-135V, 47-63 Hz single-phase source and model RS64B operates from a 190-260V, 47-63 Hz single-phase source. The power control panel of each model provides the facilities for connecting primary power. Each panel contains a male receptacle for input power and a female outlet for extending primary power to other units. Drawing C-BD-RS64-0-10 illustrates a typical arrangement for primary power. A mating connector rated at 15 Amperes is recommended for power input-output connections.

The power control panel also provides the receptacle for remote control for primary power and extending remote control to other units. Drawing C-BD-RS64-0-10 also illustrates a typical arrangement for remote control of power; Figure 2-2 illustrates the circuits used for remote control.

#### 2.4 SIGNAL CONNECTIONS

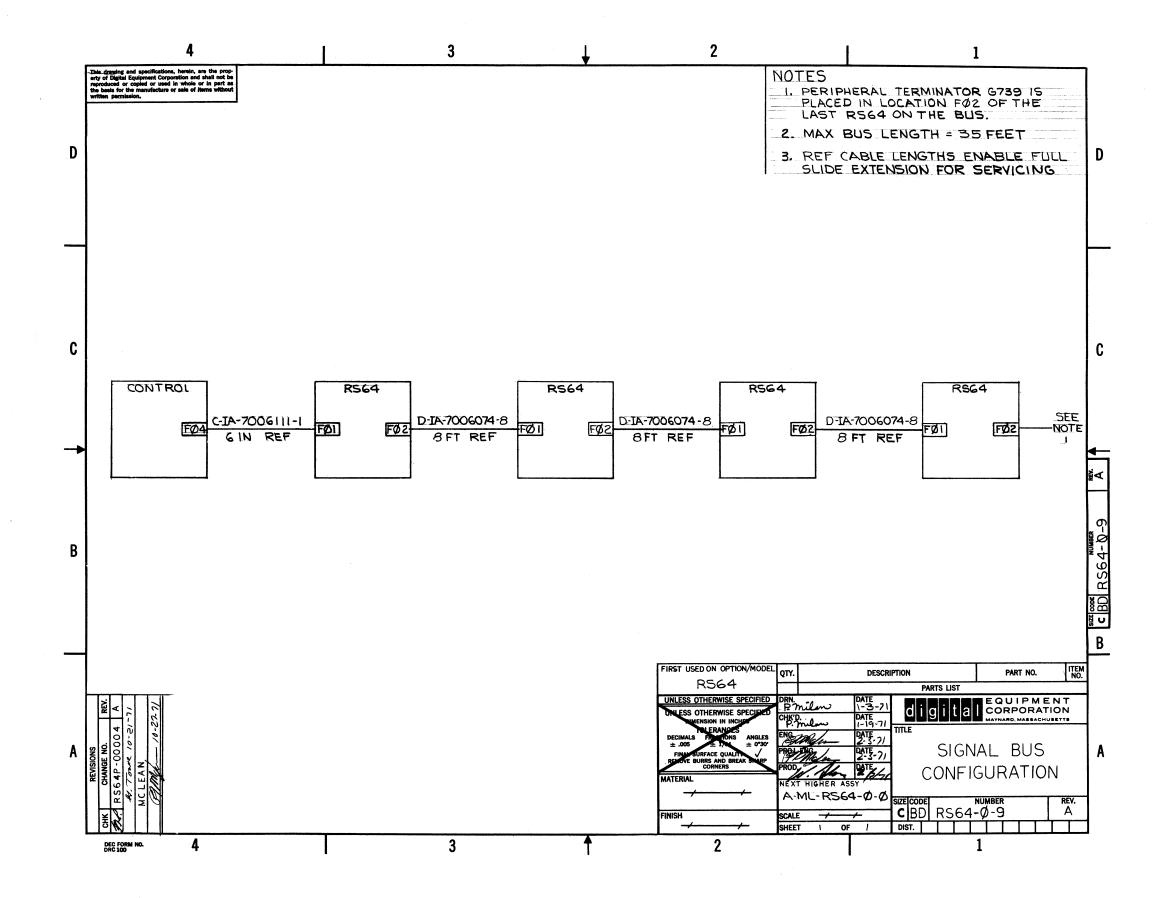

Drawing C-DB-RS64-0-9 shows a typical arrangement for connecting up to four RS64 Disk Files on a controller bus. This drawing also defines the cable types. Bus length should be 35 ft or less and a G739 terminator card should be used in the last RS64 unit on the bus.

Figure 2-1 RS64 Disk File Packaging

#### 2.5 INSTALLATION CHECKOUT

The RS64 Disk File is thoroughly checked at the factory. However, complete diagnostics should be run after the unit is installed. Information for running the diagnostics is included with the controller.

#### 2.6 PREPARATION FOR MOVING AND SHIPPING DISK FILE

If the unit is to be moved or shipped in a cabinet, install motor lock and shock mount yokes. Lock the assembly in place using shipping brackets.

If the unit is to be shipped in a separate container, use the original shipping container where possible. Items used for shipping are depicted in Figure 2-1.

#### 2.7 OPERATION

#### 2.7.1 Power Control Panel Controls and Indicators

The power control panel, Figure 2-3, contains an input power indicator, a 15A circuit breaker, and a LOCAL/OFF/REMOTE switch. The input power indicator is lit whenever primary power is applied to input receptacle P1. Circuit breaker CB1 controls the application of primary power to the disk drive motor, the fan, the power supply relay, and the local/remote control circuits.

The LOCAL/OFF/REMOTE switch controls the application of primary power to the power supply. In the LOCAL position, it energizes the power supply relay to complete the primary power path. In the OFF position, this switch interrupts the control path for the power supply relay to remove primary power.

Figure 2-2 Remote Control and Interlock Connections

The REMOTE position permits power supply turn-on by a remote switch closure. When used in a remote turn-on chain with other units, the LOCAL and OFF positions complete the remote turn-on chain for other units. This feature permits any device to be controlled locally yet still maintain the remote turn-on control for other units.

#### 2.7.2 Disk Select and WLO Panel Controls

This panel, Figure 2-3, provides the controls for establishing a disk drive unit number and for selecting tracks that are to be write protected (write lockout).

- a. UNIT SELECT This 5-position rotary switch establishes a unit number (0 through 3) for a drive or places it logically off-line (OFF position) with respect to a controller or program.

With this switch in other than OFF, the drive is selected by a corresponding unit number from a controller. This feature permits up to four disk units to be operated from one controller.

- b. WRITE LOCKOUT This rocker switch, when placed to the ENABLE position, permits the tracks designated by the TRK ADD switches to be write protected. When placed to the DISABLE position, this switch negates any write lockout function.

- c. TRK ADD  $2^0 2^4$  These binary-weighted rocker switches select the tracks that are to have write lockout or write protection. The write lockout function is provided for tracks selected by the binary combination of the switches plus any lower-number tracks. For example, with the  $2^0$  switch in the logical 1 position and all others in the logical 0 position, tracks 1 and 0 have write lockout. Similarly, with the  $2^0$  and  $2^1$  switches in the logical 1 position, tracks 0 through 3 inclusive are write locked.

Figure 2-3 Power Control and WLO Panel

#### 2.7.3 Operating Instructions

In general, the RS64 disk is an automatic device that does not require operator intervention. To operate the device, simply select a unit number (0 through 3) corresponding to program assignment and apply primary power.

To set up write lockout for tracks:

Procedure

1 Press WRITE LOCKOUT switch to ENABLE.

2 Set up TRK ADD switches to binary equivalent of the highest track number that is to have write lockout. For example, to provide write lockout for tracks 0 through 16, press the 2<sup>4</sup> switch and leave 2<sup>0</sup> through 2<sup>3</sup> in 0 position. To provide write lockout for track 0 only, set all switches to 0.

To discontinue write lockout for previously selected tracks, simply return WRITE LOCKOUT switch to DISABLE position.

Figure 2-4 Power Supply Mounting Panel

Figure 2-5 Placement of Power Supply

Figure 2-6 Extender Cabling Diagram

# CHAPTER 3 THEORY OF OPERATION

#### 3.1 SYSTEM RELATIONSHIPS

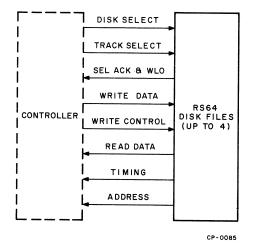

Figure 3-1 shows the general relationships of an RS64 Disk File with a controller. Up to four disk files can be operated with one controller. Each disk file is assigned a unit number and is selected by one of four lines from the controller. Only that disk file having the unit number designated by the controller responds to a selection. When a disk is selected, it acknowledges the selection and provides the controller with timing and address information recovered from the disk. Five binary-weighted lines from the controller select one of 32 data tracks. If the data track specified in the selection is write locked, the disk file also notifies the controller.

Figure 3-1 RS64 System Relationships

When the controller synchronizes with disk timing information and recognizes the address specified by the program, it begins writing or reading information at that address. For a write operation, the controller enables the disk write electronics and provides the disk with serial data. A read operation is implemented whenever a write operation is not specified. A synchronizing preamble is included with the address and data so that recovery synchronization can be independent of inherent skew between timing, address and data tracks.

#### 3.2 DISK SURFACE AND TRACK ARRANGEMENT

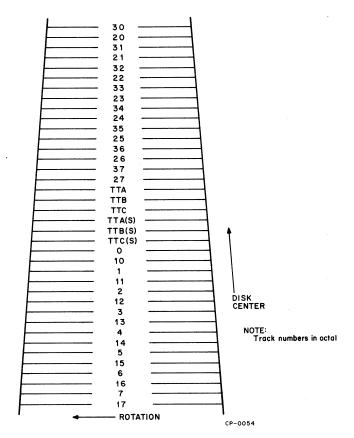

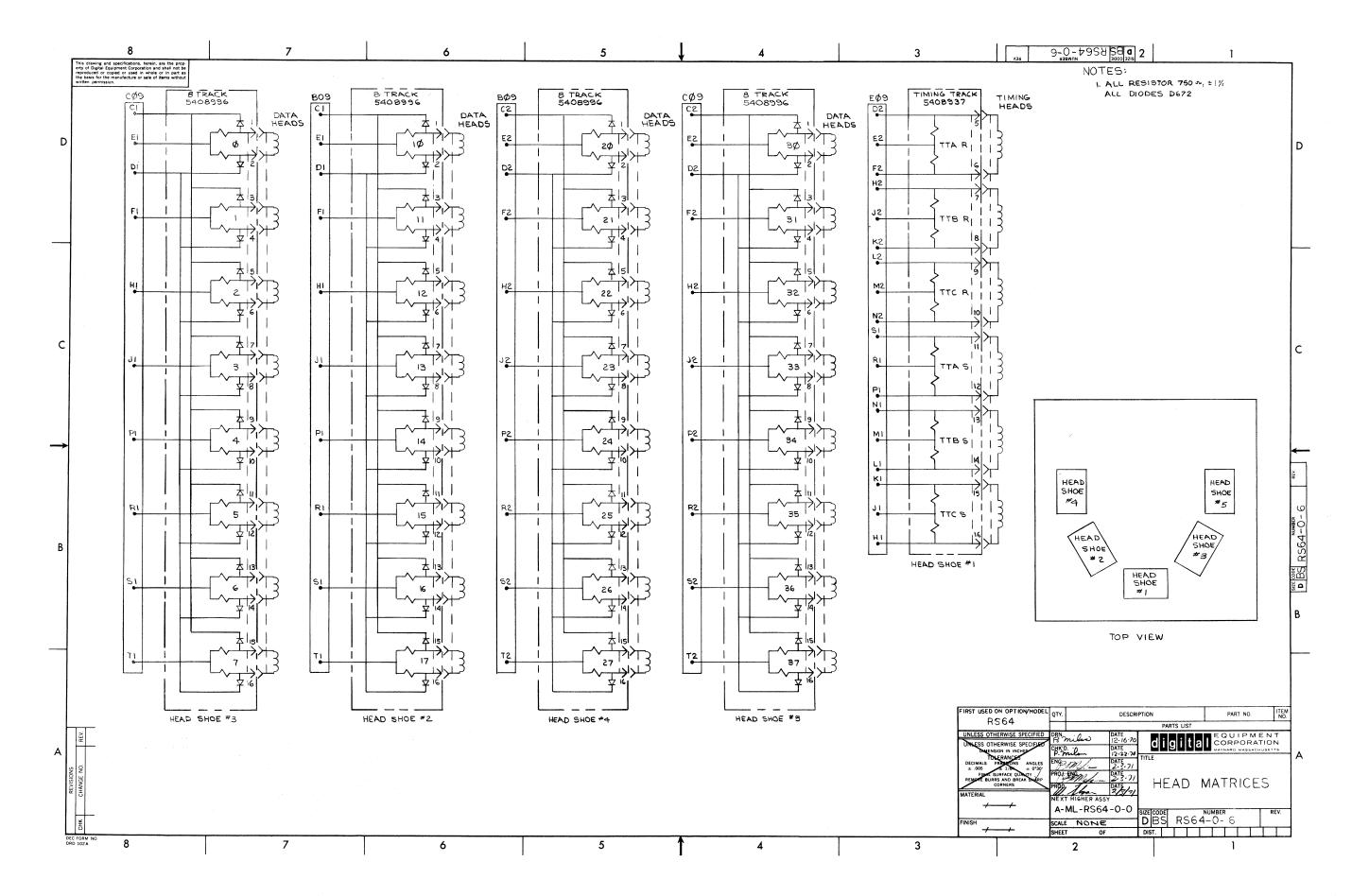

Information is recorded on the lower side of the disk plate, Figure 3-2, at a perimeter beginning approximately 3/4 in. from the outer edge of the disk. Four head shoe assemblies, each containing eight read/write heads, store and retrieve data. One head shoe assembly, containing six read/write heads, is used for writing and recovery of timing and address information, i.e., timing tracks A, B, and C and three spares. These head shoe assemblies are located in the disk base plate as shown in Figure 3-3. Figure 3-4 depicts the arrangement of tracks.

Figure 3-2 Disk Assembly with Cover Removed

#### 3.3 FUNCTIONAL DESCRIPTION

#### 3.3.1 Functional Block Description

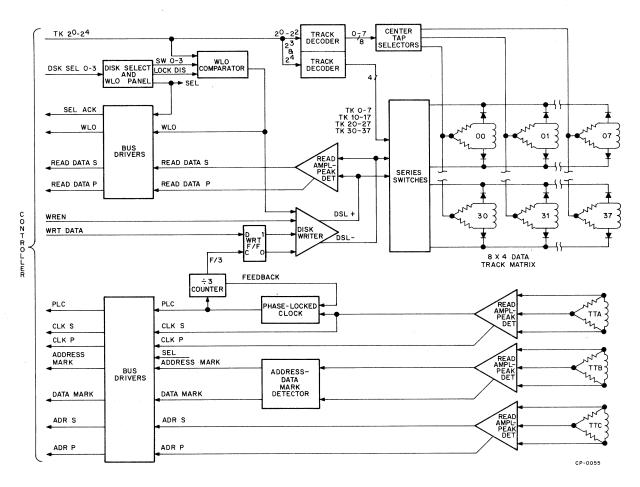

Figure 3-5 illustrates the functional circuits that comprise the RS64 Disk File. The upper part of this diagram depicts the disk and track selection circuits and the read and write data paths. The lower part of the diagram depicts the circuits associated with the timing and address tracks.

Figure 3-3 Disk Assembly with Head Shoes Exposed

The disk utilizes three pre-recorded timing tracks (plus three spares) and 32 data tracks for recording and recovery of data. Bit timing (and bit cell width) is established by timing track A (TTA). With the exception of an origin gap, this track contains a continuous stream of logical 1's. Timing from this track is supplied to a self-synchronizing phase-locked clock. The phase-locked clock is used as a three times frequency multiplier; it synchronizes its output to the phase of the TTA timing stream to enable separation of sync pulses, data ones, and data zeros recovered from the other tracks.

Timing track B conveys address and data markers. The address marker denotes the beginning of an address sector on timing track C; it occurs at least six bit times before the address preamble. Similarly, the data marker signifies the beginning of a data sector of a track.

Timing track C conveys the information for addressing portions of a data track, i.e., block addresses. A synchronizing preamble and an odd parity bit are included with each block address. The number of primary divisions or blocks assigned to the data tracks determines the number of address bits. For RC11 usage, for example, data is stored in 64 blocks; thus, a 6-bit address is required. The synchronizing preamble provided with the address permits a controller to correctly synchronize with TTC information without having to compensate for skew between the clock timing track and the address track.

Information is continuously read from timing tracks A, B and C; however, this information is not gated to the controller until the disk file is selected. For selection of a disk file, the controller enables one of four input lines

Figure 3-4 Track Arrangement

(DISK SEL 0-3) to the Disk Select/WLO panel. If the disk file is assigned a unit number corresponding to the controller selection, the Disk Select/WLO panel provides an SEL output. This output enables the gating of timing, address, and read data to the controller. Selection of a disk file also causes the selected unit to return a SEL ACK signal to the controller. This signal informs the controller the disk file is operable and has recognized the selection.

Concurrent with selection of the disk file, the controller specifies which track is to be used. This information is provided as a 5-bit track address (TK  $2^0 - 2^4$ ) to the track decoder circuits and a write lockout (WLO) comparator. If the track designated by the controller is one of a group selected to be write-protected (no rewriting of the track), the WLO comparator disables the disk write circuits. Thus, only a read operation can be performed for the track. Since the write lockout disables the write driver, no combination of control signals can enter information on the write locked tracks.

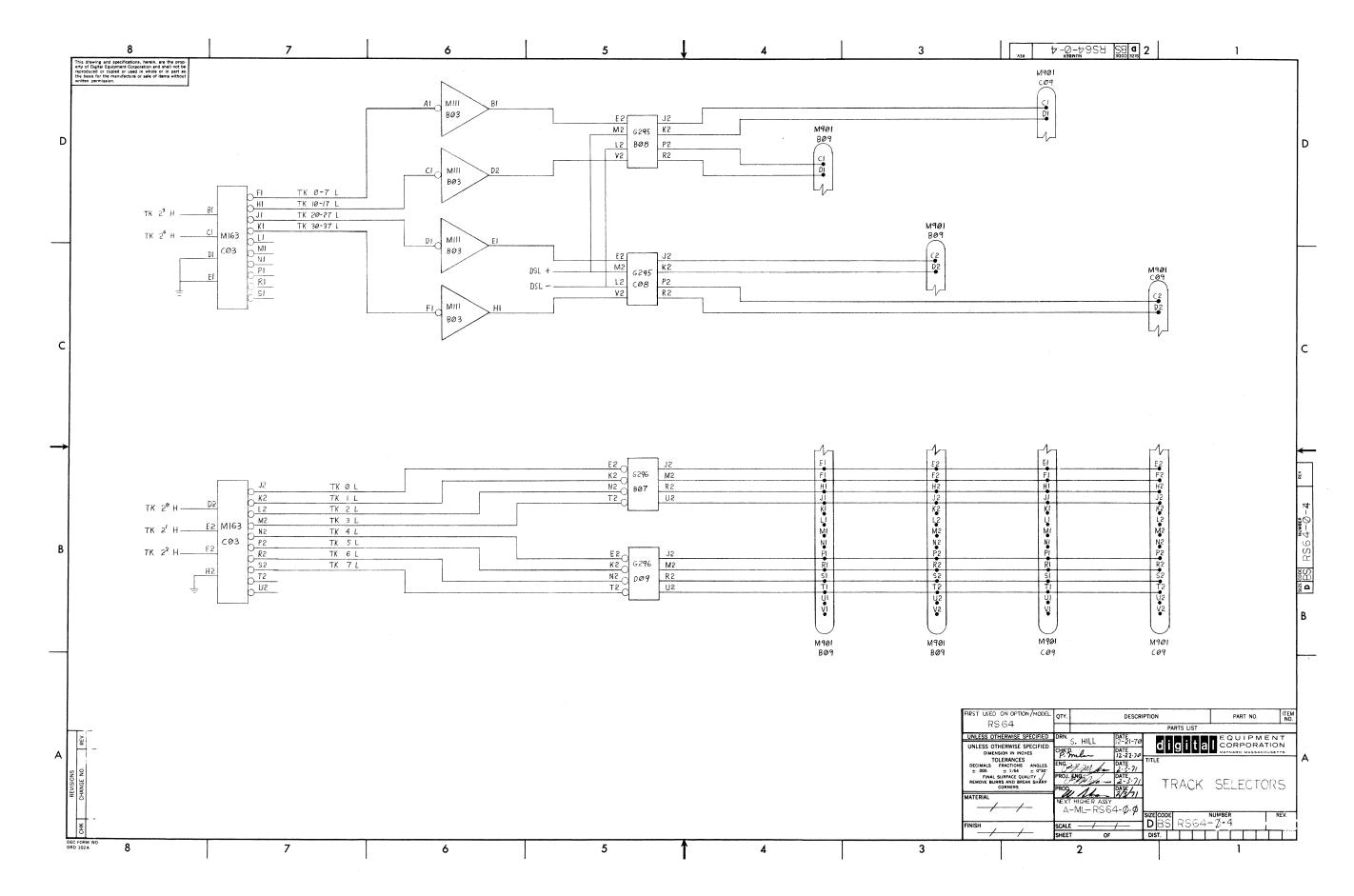

The track address is decoded in two parts. One decoder circuit decodes the three LSB's  $(2^0 - 2^2)$  and enables one of eight center tap selector circuits to select one of eight matrix lines (0-7). Similarly, a second decoder circuit decodes the two MSB's of the track address and enables the corresponding series switch circuits to select one of four pairs of matrix lines (octal group 0-7, 10-17, 20-27, or 30-37). The combination provided by the center tap selector and the series switch selects the track for an ensuing read or write operation.

A read operation is specified by the negation of a write enable (WREN) input. This input disables the disk writer circuits to allow a read operation. When the controller recognizes the address for the desired block of the selected track, it begins accepting the serial read data.

For a write operation, the controller compares the address from timing track C with the address specified by the program. Upon recognizing the correct address, the controller asserts the WREN input and provides serial NRZ data to the disk write flip-flop. This flip-flop, clocked at mid-bit time with respect to the input serial NRZ data,

R8m 18- JUL-75

Figure 3-5 RS64 Functional Block Diagram

toggles on each binary 1 in the input. This action reverses the record head current each time a binary 1 is present and results in the recording of a binary 1 by reversing the flux saturation.

#### 3.3.2 Timing Path Logic

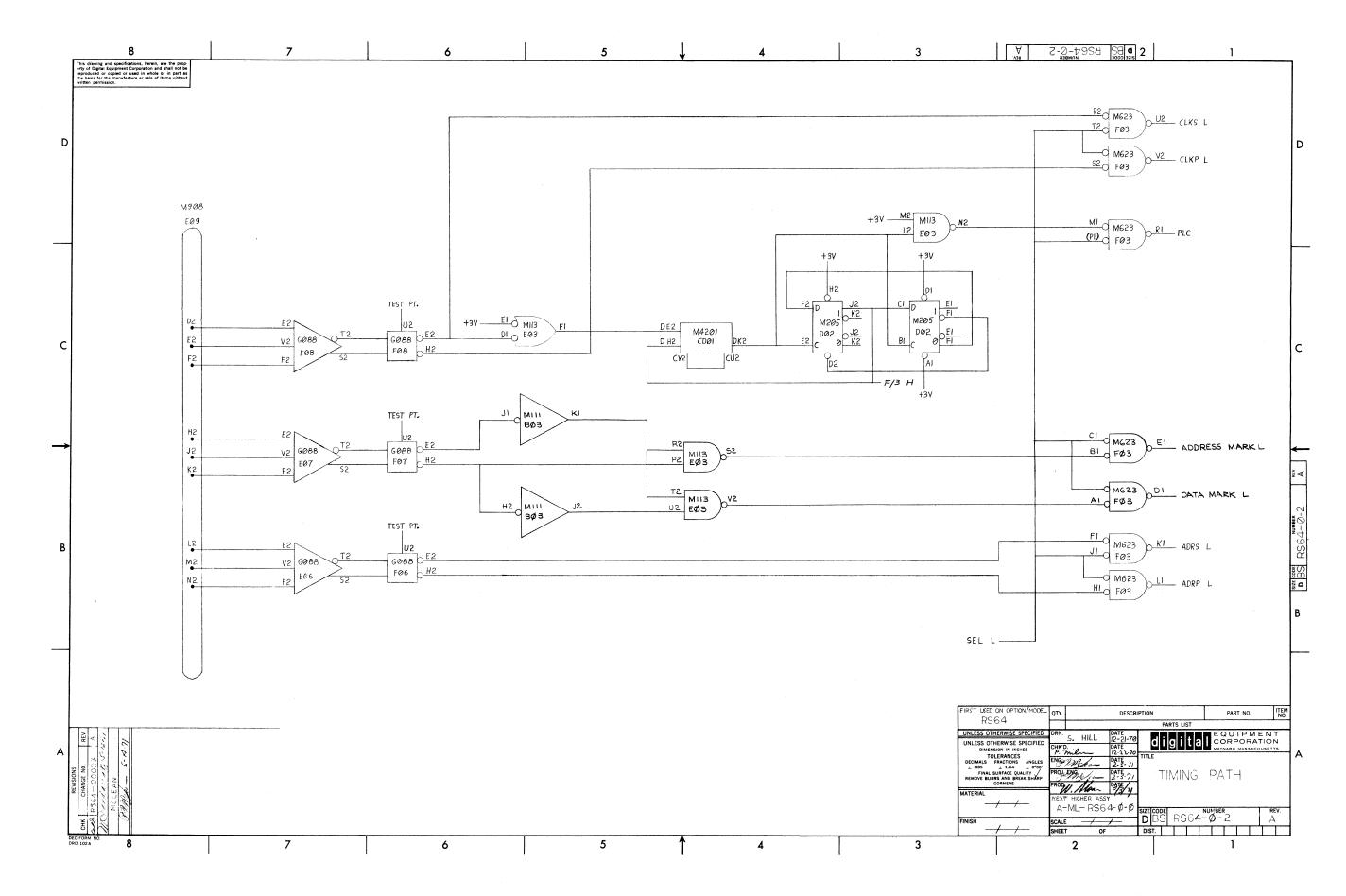

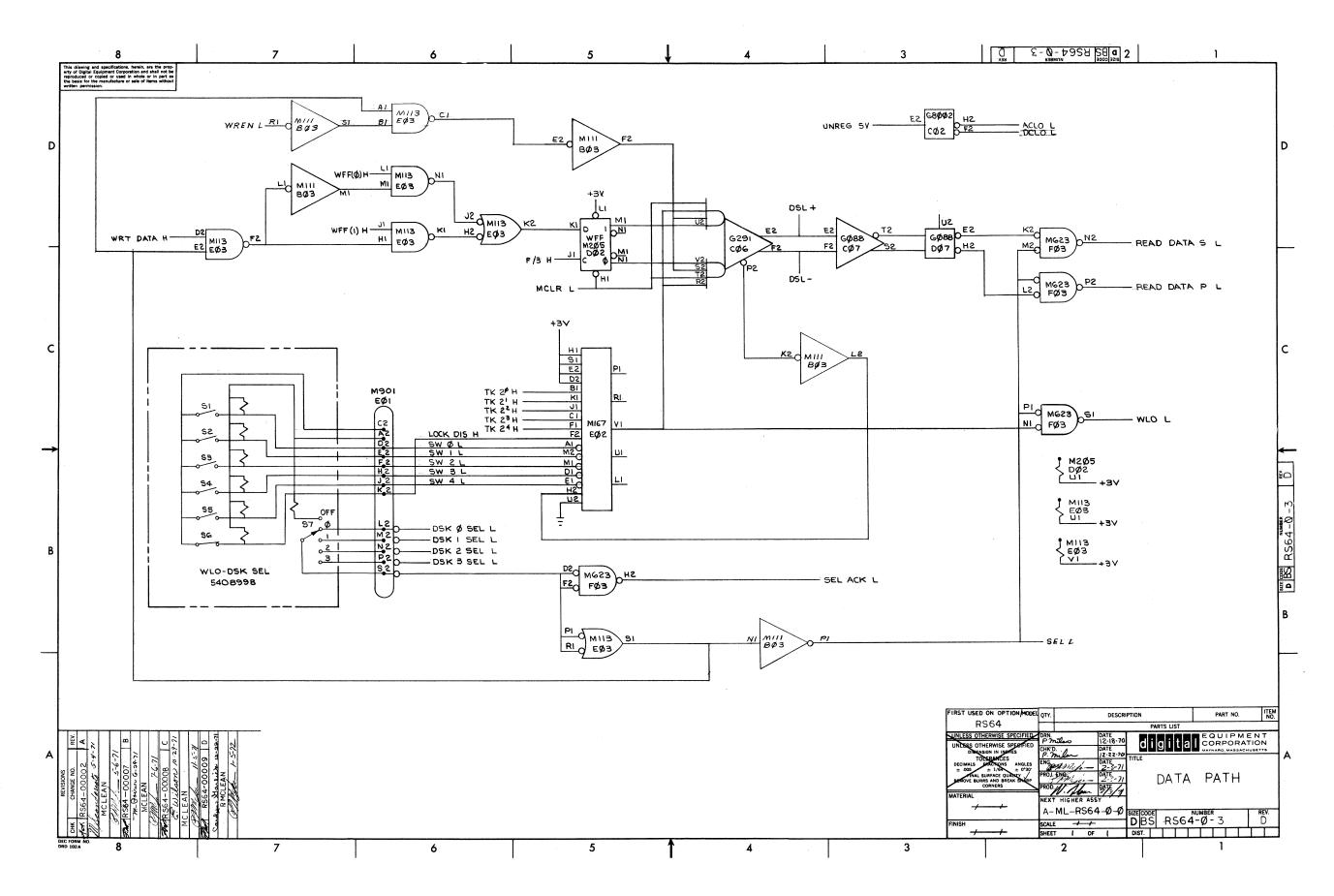

Drawing D-BS-RS64-0-2 shows the circuits associated with disk timing. In general, these circuits reconstruct the digital form of disk timing tracks, synchronize an internal clock with the disk bit timing track (TTA), and provide timing information to a controller when the disk is selected by the controller. Bit timing is also provided to the write data path.

Differential inputs from timing track heads TTA, TTB, and TTC are applied to read amplifier-peak detector modules E-F08, E-F07, and E-F06, respectively. These modules convert the differential bipolar input pulses (representing logical 1's) into negative-true (0V) 300-ns strobe pulses at output pin E2. The leading edge of a strobe pulse occurs at approximately the peak of the input pulse. The read amplifier-peak detector modules also produce an output at pin H2 that signifies the polarity of the input pulse. This signal is negative-true (0V) for a positive-input pulse and has a pulse width corresponding to the duration of the input pulse. The strobe and polarity outputs of TTA and TTC are gated to the controller whenever the disk is selected. The strobe output (CLK S or ADR S) is used as a timing reference while the polarity output (CLK P or ADR P) is used for error checking functions.

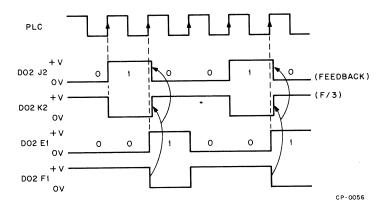

The TTA read amplifier-peak detector also provides strobe pulses to a self-synchronizing phase-locked loop consisting of an M4201 phase-locked clock and two M205 D-type flip-flops connected as a divide-by-3 counter.

This loop synchronizes the output phase with the strobe pulses recovered from TTA. For this function, the M4201 phase-locked clock compares the time occurrence of the counter output (feedback) with the TTA strobe pulses and uses the result of these comparisons to correct the frequency of a VCO. Since this VCO drives the divide-by-3 counter, the self-correcting loop phase-locks the output phase to the TTA strobes. Counter timing relationships are provided in Figure 3-6. Additional information on the phase-locked clock is provided in the module descriptions (Paragraph 3.4.16).

Figure 3-6 Counter Timing Relationships

As mentioned previously, TTB conveys the address and data markers signifying the beginning of address or data. The address marker is identified by a negative polarity pulse recovered from TTB and a data marker is identified by a positive polarity pulse recovered from TTB. For the detection of the markers, the strobe output of the TTB read amplifier-peak detector is ANDed with its polarity output. If the polarity output at F07–H2 is positive and a strobe pulse is present, the timing logic provides a 300-ns, negative-true address marker pulse to the controller. Similarly, if the polarity output at F07–H2 is at 0V and a strobe pulse is present, the timing logic provides a 300-ns, negative-true (0V) data marker pulse to the controller.

#### 3.3.3 Data Path Logic

Drawing D-BS-RS64-0-3 shows the circuits for disk selection, write lockout, and the write and read data paths. For selection of a disk file, the controller ground-asserts one of four select lines (DSK 0-3). If the UNIT SELECT switch on the Disk Select/WLO panel is in a corresponding position, the ground-asserted input generates a SEL L gating level; a SEL ACK output is also returned to the controller. The SEL L signal gates disk timing, read data, and other signals to the controller bus. The SEL ACK output informs the controller the disk file is not in a power-down or off-line state so that the ensuing operation can proceed.

A write lockout function is implemented with an M167 comparator module. This module compares the controller track address (TK  $2^0 - 2^4$ ) with inputs from the binary-weighted TRK ADD switches. If the track address specified by the controller is equal to or less than the address selected by the TRK ADD switches, the M167 comparator output is a ground level. This output prevents turn-on of the G291 disk writer; thus, information on the track cannot be erased or changed. The ground level from the M167 comparator also generates a WLO L signal to the controller. In contrast, if the track address specified by the controller is greater than the switch selection, the M167 comparator provides an enable level to the G291 disk writer.

The upper part of D-BS-RS64-0-3 shows the circuit elements comprising the write and read data paths up to the data sense lines (+DSL and -DSL). From a logic viewpoint, these paths are straight-forward and, therefore, are not discussed in detail. However, the read/write electronics are described in subsequent paragraphs.

#### 3.3.4 Read/Write Electronics

3-4

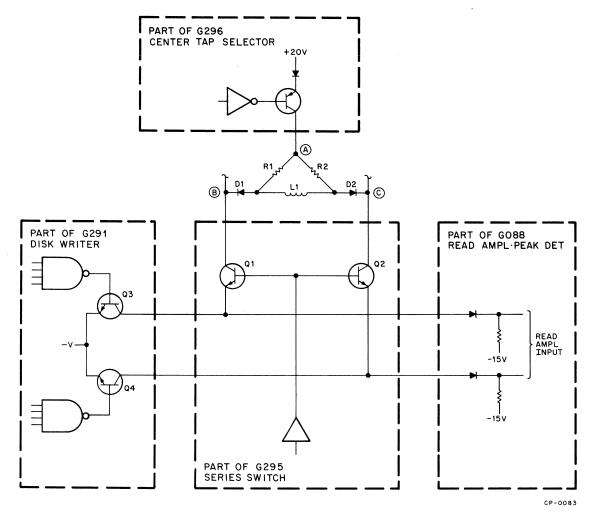

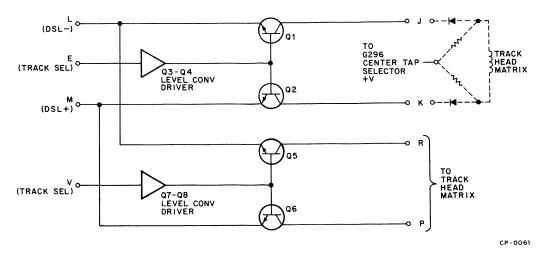

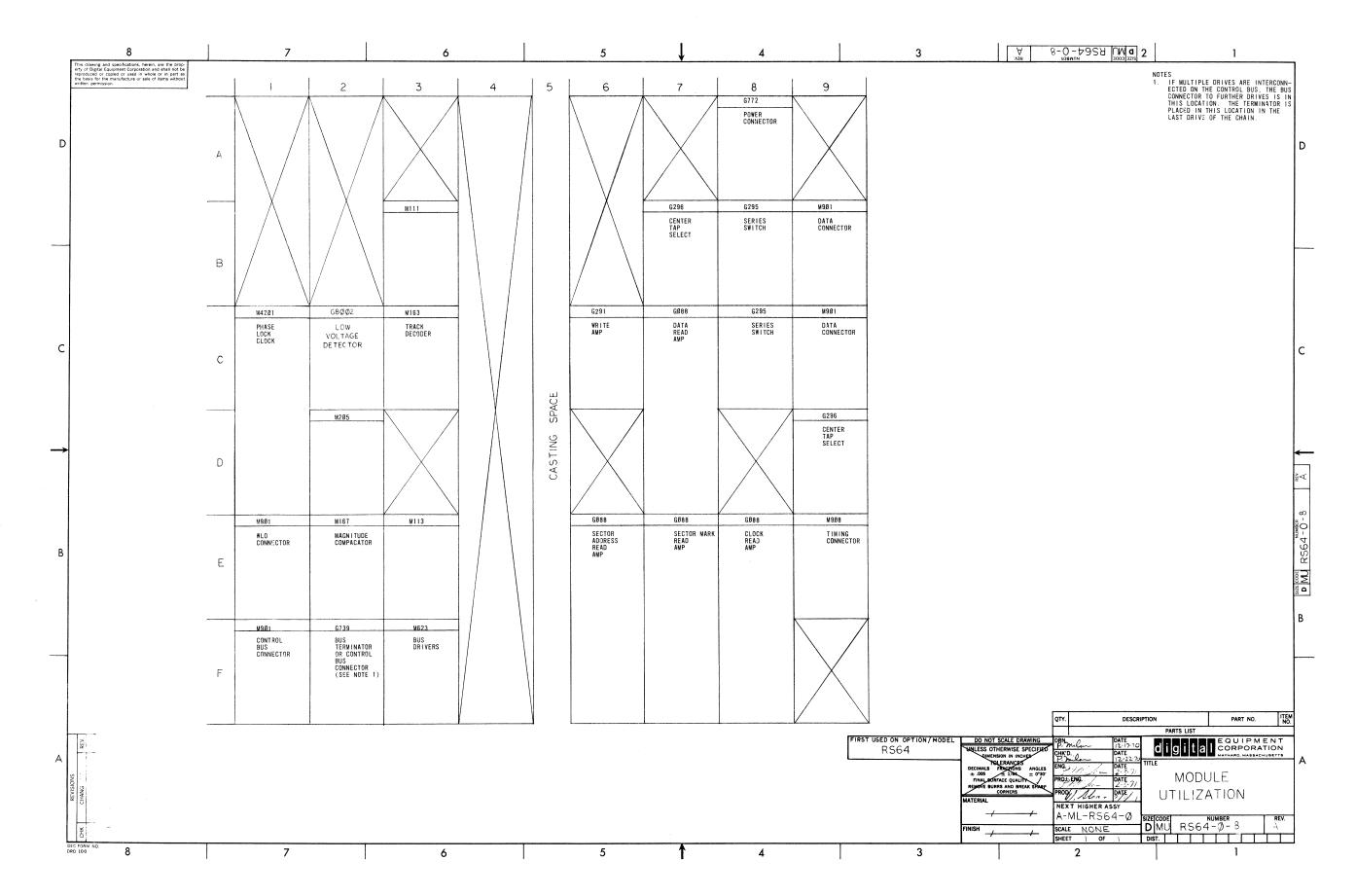

As mentioned previously, data is stored serially around the disk surface by 32 fixed data heads. The controller selects the active data read/write head with five binary-weighted lines. Drawing D-BS-RS64-0-4 shows the circuit elements for track selection. Note that the track address is decoded in two parts. One octal group (0-7, 10-17, 20-27, or 30-37) enables a related G295 series switch while decoding the lower order track address bits enables one G296 center tap selector. Once selected, the head reads or writes according to inputs from the controller.

The RS64 disk uses the Non-Return-To-Zero Inverted (NRZI) recording technique. In this technique, a change in the direction of the magnetic flux along the disk track represents a binary 1 and no change in the magnetic flux represents a binary 0. A binary 1 is written by reversing the direction of the write current in the recording head.

Figure 3-7 illustrates in simplified form the circuits used for writing and reading of data. A head winding is represented by coil L1. This coil forms the center leg of a bridge circuit consisting of resistors R1 and R2, isolation diodes D1 and D2, and switching transistors Q1 and Q2 in the G295 series switch module.

Figure 3-7 Read/Write Electronics

When the controller reads using this head, it does so by activating the appropriate G296 center tap selector module (to select one of eight matrix lines) and the appropriate G295 series switch module (to select one of four groups). This combination connects node A to +20V, switches transistors Q1 and Q2 on, forward biases diodes D1 and D2,

This combination connects node A to +20V, switches transistors Q1 and Q2 on, forward biases diodes D1 and D2,

and completes a 5 mA (approximate) current path through each leg of the bridge and the differential input of the read amplifier. With equal current in the legs, no current flows in the read/write head. When data is read, the changing magnetic field from the disk surface induces a voltage in the head that appears across the differential input of the G088 read amplifier-peak detector. This voltage is subsequently amplified and converted to a digital strobe. The polarity of the voltage across the coil is a function of the direction of flux change; thus, bipolar analog pulses are provided to the read amplifier.

For a write operation, the recording head is selected the same as for a read operation, but the bridge is unbalanced by switching the emitter of Q1 or Q2 to -15V via one of the transistors in the G291 disk writer module. This action forces approximately 45 mA through the head coil. The direction of current flow through the head is determined by which G291 transistor is active; this transistor switching, in turn, is controlled by the state of the write flip-flop.

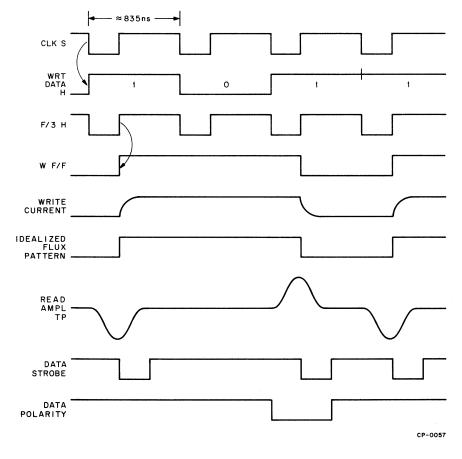

Figure 3-8 shows the relationships of the read and write waveforms. For a write operation, the serial NRZ write (WRT) data is clocked by the positive transition in the bit rate (F/3) timing. Each binary 1 in the NRZ input complements the flip-flop which, in turn, switches one of the transistors in the G291 disk writer module on and its counterpart off. As a result, head current is reversed and the magnetic field is reversed on the disk surface.

Figure 3-8 also shows the corresponding analog and digital waveforms for a read operation. Note that the read voltage consists of bell-shaped pulses that peak at the maximum change in the flux pattern. Note also that the NRZI format results in bipolar pulses having alternate polarities, i.e., no two successive pulses have the same polarity. This characteristic, through the use of the DATA P output, can be used to detect errors.

Figure 3-8 Write and Read Waveforms

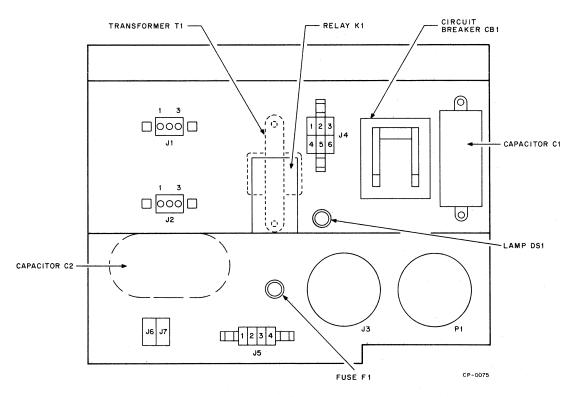

#### 3.3.5 Power Control Panel

Drawing D-AD-7006868-0-0 is a schematic of the 115V and 230V power control panels. These panels are functionally identical; they differ primarily in the wiring for the primary of the local/remote power transformer (parallel connections for 115V and series for 230V) drive motor connections and rating of various components. Each control panel contains:

- a. a male receptacle for primary power,

- b. a female utility receptacle,

- c. an RFI filter (L1, L2, and C1),

- d. a power input indicator,

- e. 15-A circuit breaker CB1,

- f. step-down transformer T1,

- g. local/remote switch assembly S1 and

- h. power supply relay K1.

Transformer T1 provides an 18 Vrms potential that is rectified by diodes on local/remote switch assembly S1. The resulting potential is used as a supply voltage to energize K1. The LOCAL/OFF/REMOTE switch completes the energizing path for K1 by providing a ground input to K1. This input can be supplied as a result of positioning the switch to LOCAL or by a remote switch closure when the switch is in the REMOTE position.

#### 3.3.6 Power Supply

Refer to Appendix B for power supply coverage.

#### 3.4 MODULE DESCRIPTIONS

#### 3.4.1 G088 Read Amplifier-Peak Detector

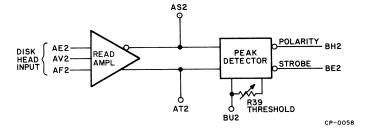

The read amplifier-peak detector reconstructs the digital form of bipolar analog pulses read from disk timing and data tracks. Disk head inputs are provided in differential form and all outputs are TTL compatible.

Functionally, the G088 module consists of a differential amplifier and a peak detector as shown in Figure 3-9, Drawing DS-C-G088-0-1 is a schematic of the G088 module.

Figure 3-9 G088 Read Amplifier-Peak Detector Simplified Diagram

The read amplifier portion is a 3-stage, discrete-component differential amplifier (Q1 through Q6) with a 3 dB bandwidth from 60 kHz to 700 kHz. The amplifier has linear gain characteristics (up to a maximum gain of 1000) for low-level inputs (up to 10 mV) and nonlinear gain characteristics (gain compression) to prevent peak distortion at higher level inputs. Diodes D5, D6, D10, and D11 provide the gain compression features.

The differential output of the amplifier is ac-coupled to the peak detector. Figure 3-10 depicts the amplifier output and the waveforms for the peak detector. The peak detector portion detects the peaks of the bipolar pulses provided by the read amplifier and generates a 300-ns, negative-true strobe pulse for each peak. It also generates a polarity output denoting the polarity of the peak; a negative pulse denotes a positive polarity input pulse. Two test points (AS2 and AT2) permit monitoring of the amplified output.

Figure 3-10 G088 Read Amplifier-Peak Detector Waveforms

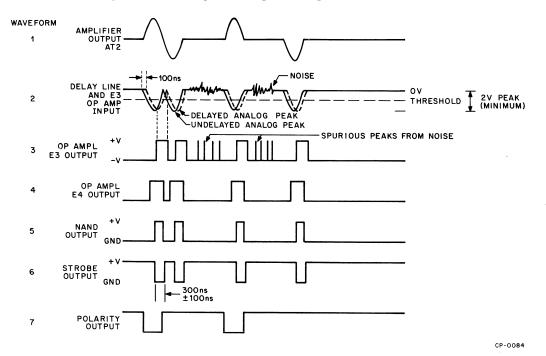

Transistor stages Q8 and Q9 (with diodes D12 and D13) rectify the bipolar pulse input and provide a single-ended signal to the 100-ns delay line and amplifier E3. Peak detection is accomplished by delaying the analog input by 100 ns then comparing the magnitude of the delayed signal with the undelayed signal. Stage E3 functions as an analog voltage comparator that is operated open-loop. Its output saturates positive whenever the delayed analog signal is more negative than the undelayed analog signal (Figure 3-10). Conversely, its output is negative whenever the difference in the analog inputs is zero or the undelayed input is more negative than the delayed input. Thus, its output approximates a digital form and is positive for each analog peak.

When both the delayed and undelayed analog inputs are at zero (no peaks), any noise that exceeds the input threshold of E3 causes spurious peaks in its output. To eliminate this aspect, the delayed analog signal is compared with a voltage reference (provided by R39 and R42) at operational amplifier E4 and the output of E4 remains negative unless the analog input exceeds the threshold reference. This threshold is set such that noise peaks cannot drive the output of E4 positive yet data peaks can. Since the output of E4 is ANDed with the output of E3, the net effect cancels noise peaks in the output of NAND gate E1 (Waveform 5, Figure 3-10). Test point BU2 is provided for adjusting the threshold. This reference is set to the midpoint between maximum noise peaks and minimum data peaks. Nominally, this reference is -1.2V.

The pulsewidth of the strobe output is standardized by one-shot E2. This circuit, triggered by a negative transition, produces a nominal 300-ns strobe pulse. The leading edge of this pulse denotes the data peak position. This pulse is inverted for a negative-true strobe output (Waveform 6, Figure 3-10).

Transistor stage Q7 produces a polarity pulse for each positive pulse in the disk head input. The output of Q7 is inverted for a negative-true pulse. This pulse has a duration corresponding to the width of the input pulse.

#### INPUTS:

| Pin      | Use                     | Drive or Load |

|----------|-------------------------|---------------|

| AE2, AF2 | Head Differential Input | 5 to 10 mV    |

| AV2      | Head Center Tap         | -             |

#### **OUTPUTS**:

| Pin      | Use                                | Drive or Load |

|----------|------------------------------------|---------------|

| BE2      | Strobe (300 ±100 ns)               | 10 TTL loads* |

| BH2      | Polarity                           | 10 TTL loads  |

| AS2, AT2 | Read Amplifier Output Test Points  | <del></del>   |

| BU2      | Peak Detector Threshold Test Point | <del></del>   |

#### POWER:

| Pin      | Use           |

|----------|---------------|

| BA2      | 25 mA at +5V  |

| AB2, BB2 | 60 mA at -15V |

| AC2, BC2 | GND           |

| AA2, BD2 | 60 mA at +20V |

<sup>\*</sup>One TTL unit load is 1.6 mA (maximum).

#### 3.4.2 G291 Disk Writer

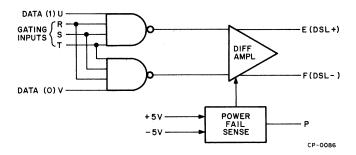

The disk writer records information on a disk. Functionally, it consists of an 80-mA differential-current amplifier with two 4-input AND gates for accepting complementary TTL data inputs (and gating signals) as shown in Figure 3-11. The module also contains a power-fail sensor that holds the writer off during power-up or power-down sequencing.

Figure 3-11 G291 Disk Writer Simplified Diagram

Transistor stages Q1 through Q4 (Drawing CS-G291-0-1) comprise the differential-current amplifier. Stages Q1 and Q4 are the differential input pair. Stages Q2 and Q3 function as the current sinks for writing. These stages complete the write current path between -15V and the data sense lines (DSL). With the data input to pin U a logical 1 (and gating inputs at +3V), Q3 completes the current path for the DSL (-) line. Similarly, with the data complement at pin V a logical 1, Q2 connects -15V to the DSL (-) line.

Transistors Q5 and Q6 (with breakdown diodes D3 and D17) monitor the +5V and -15V for a power fail condition. When the sum of these potentials drops below 16.4V, Q2 and Q3 are clamped off. This feature prevents the disk writer from recording extraneous information on the disk during power-up or power-down sequencing. A power fail output is also made available at pin P. This output is low (0V) whenever power is below the power-fail threshold

#### **INPUTS:**

| Pin        | Use                      | Drive or Load    |

|------------|--------------------------|------------------|

| U2         | Data Input               | 1 TTL load       |

| V2         | Complementary Data Input | 1 TTL load       |

| R2, S2, T2 | Write Enable             | 2 TTL loads each |

#### **OUTPUTS**:

| Pin | Use                        | Drive or Load   |

|-----|----------------------------|-----------------|

| F2  | Write Output               | 80 mA (nominal) |

| E2  | Complementary Write Output | 80 mA (nominal) |

| P2  | Power Fail                 | 10 TTL loads    |

#### POWER:

| Pin | Use           |

|-----|---------------|

| A2  | 30 mA at +5V  |

| B2  | 85 mA at -15V |

| C2  | GND           |

| D2  | 1 mA at +20V  |

#### 3.4.3 G295 Series Switch

The G295 module is a single-height module containing two series switch circuits. It is used with the G296 center tap selector module to select disk track read/write heads. Functionally, each series switch circuit consists of an input level converter and a driver and two NPN current switches as shown in Figure 3-12.

Figure 3-12 G295 Series Switch Simplified Diagram

Pin E (or V) accepts a TTL track select input. When this input is a logical 1 (+3V), the level converter-driver provides base drive for current switch pair Q1 and Q2. One of these switches, in turn, provides a current path between a Data Sense Line (DSL- or DSL+) and a track head selection matrix and passes either the 80-mA write current or the 5 to 10-mV read signal. This current path is completed by a G296 center tape selector module.

|         | (                                                          |                          |

|---------|------------------------------------------------------------|--------------------------|

| Pin     | Use                                                        | Drive or Load            |

| E and V | Track Select Enabling                                      | 1 TTL load               |

| L and M | Complementary Data Sense Line outputs of Disk Write Module | Capable of sinking 80 mA |

| : Volta | ge levels of 0V or -15V. Each series switch                | pole can drive up to     |

**OUTPUTS:**

INPUTS:

Voltage levels of 0V or -15V. Each series switch pole can drive up to 150 mA. At a load current of 100 mA, the internal voltage drop is

TTL levels (0V and +3V) to pins E and V;-15V and 0V to pins L and M.

approximately 1V.

#### INPUT/OUTPUT DELAY: $1 \mu s$

#### POWER:

| Pin | Use           |

|-----|---------------|

| B2  | 81 mA at -15V |

| D2  | 2 mA at +20V  |

| A2  | 20 mA at +5V  |

| C2  | GND           |

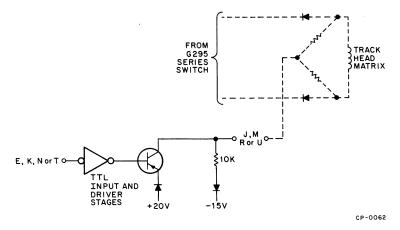

#### 3.4.4 G296 Center Tap Selector

The G296 is a single-height module that is used with a G295 series switch module to select a disk read/write head. The G296 module selects the center tap axis of this matrix, while the G295 module selects the other axis of the matrix. The module consists of four identical circuits. Each circuit uses a TTL input stage and driver and a PNP transistor switch as shown in Figure 3-13.

Figure 3-13 G296 Center Tap Selector Simplified Diagram

With the TTL input at pin E, K, N, or T at 0V, the circuit connects the respective output (pin J, M, R, or U) to the +20V source. This action, with that of the G295 series switch, provides a current path for reading or writing.

Conversely, when the TTL input is at +3V, this circuit provides a -15V potential to the head selection matrix.

| INPUTS: | TTL levels (0V and +3V) to pins E and V; -15V and 0V to pins L and M |

|---------|----------------------------------------------------------------------|

|         |                                                                      |

| Pin           | Use                             | Drive or Load   |

|---------------|---------------------------------|-----------------|

| E, K, N and T | Digital Input<br>(Track Select) | 1 TTL load each |

**OUTPUTS**: Each output provides 150 mA (maximum) at +10V when

respective input is 0V.

respective input

POWER:

| Pin | Use           |

|-----|---------------|

| A2  | 11 mA at +5V  |

| B2  | 22 mA at -15V |

| D2  | 81 mA at +20V |

| C2  | GND           |

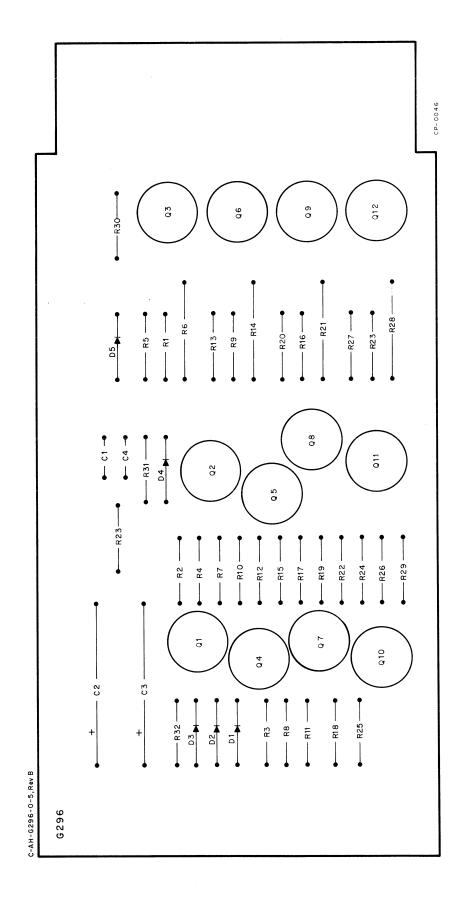

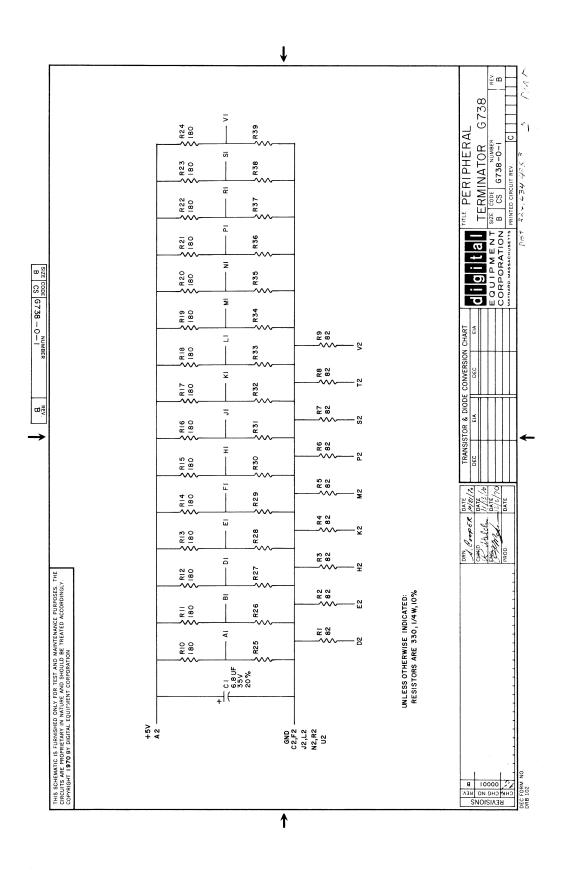

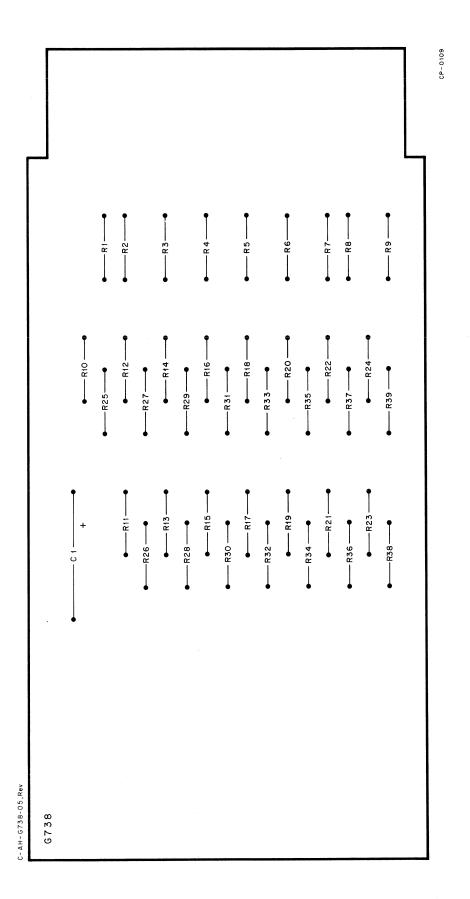

#### 3.4.5 G738 Terminator

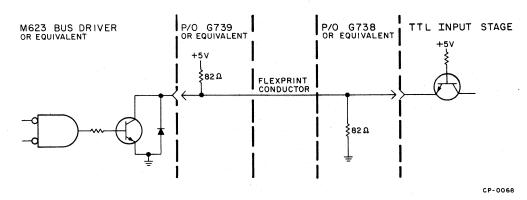

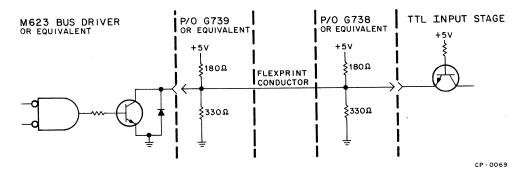

The G738 is a single-height module used as a cable bus terminator at the controller end of an RS64 Disk File interface. Ten pins terminate the "fast" signal bus lines, i.e., lines that convey information by signal transition or signals having a duration less than 100 ns. These pins provide an 82-ohm termination to ground. Fifteen pins provide termination for the "slow" signal bus lines (signals strobed by fast signals). These pins provide a termination of 180-ohms to +5V and 330 ohms to ground, yielding a Thevinin termination of 117 ohms and 3.25V.

#### **INPUTS:**

| Pin                                                                  | Use                                    |

|----------------------------------------------------------------------|----------------------------------------|

| D2, E2, H2<br>K2, M2, P2<br>S2, T2 and V2                            | 82 ohms pulldown to ground             |

| D1, E1, F1, H1, J1<br>K1, L1, M1, N1<br>P1, R1, S1, A1, B1<br>and V1 | 180 ohms to +5V and 330 ohms to ground |

| F2, J2, L2, N2<br>R2 and U2                                          | GND                                    |

#### POWER:

| Pin | Use          |

|-----|--------------|

| A2  | 20 mA at +5V |

| C2  | GND          |

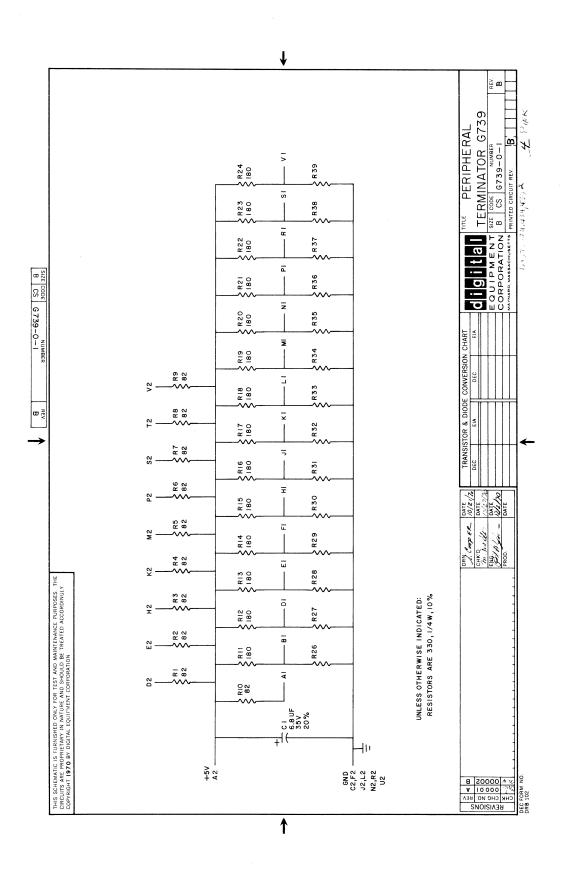

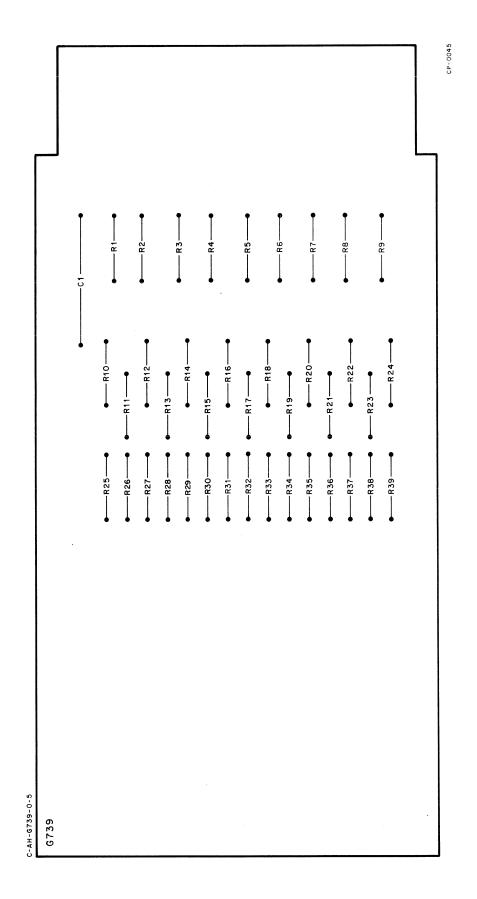

#### 3.4.6 G739 Peripheral Terminator

The G739 is a single-height module used as a cable terminator for the last drive on the bus. Ten pins terminate the "fast" signal bus lines. These pins provide an 82-ohm pullup to +5V. Fifteen pins provide termination for the "slow"

signal bus lines. These pins provide a termination of 180 ohms to +5V and 330 ohms to ground, yielding Thevinin termination of 117 ohms and 3.25 volts.

#### INPUTS:

| Pin                                                              | Use                                    |

|------------------------------------------------------------------|----------------------------------------|

| A1, D2, E2, H2<br>K2, M2, P2<br>S2, T2 and V2                    | 82 ohms pullup to +5V                  |

| D1, E1, F1, H1, J1<br>K1, L1, M1, N1<br>P1, R1, S1, B1<br>and V1 | 180 ohms to +5V and 330 ohms to ground |

| F2, J2, L2, N2<br>R2 and U2                                      | GND                                    |

#### POWER:

| Pin | Use          |

|-----|--------------|

| A2  | 20 mA at +5V |

| C2  | GND          |

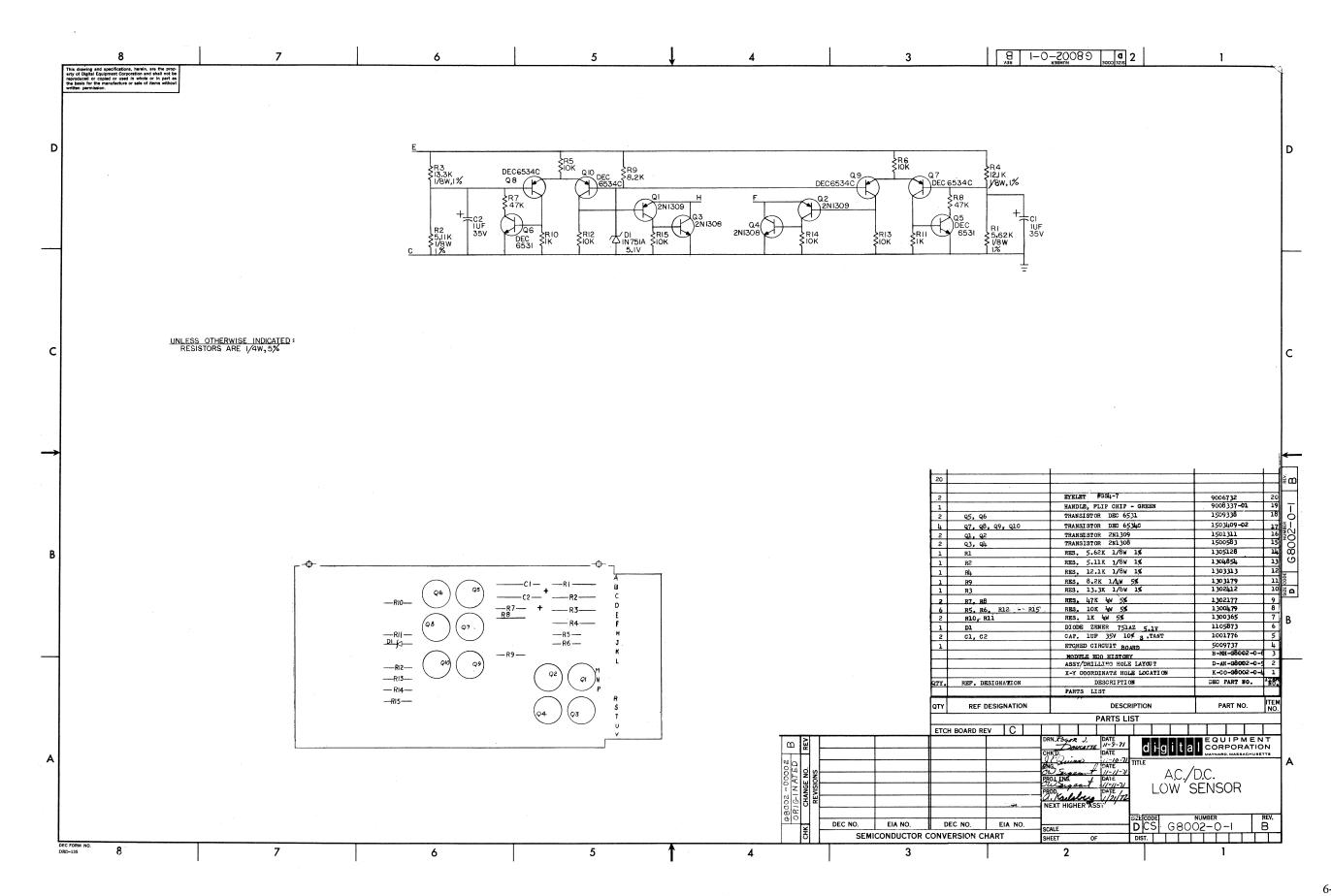

#### 3.4.7 G8002 Ac/Dc Low Voltage Detector

This module monitors the rectified and filtered, but unregulated voltage from the positive winding of the power supply transformer. The AC LO signal is generated 7 ms or more before the +5V output drops to approximately 65 percent of its nominal value. The DC LO signal is then asserted. For power up, the above sequence is reversed.

This module drives the Unibus directly, and may therefore be used for the processor to initiate a power restore routine.

#### INPUT:

|         | Pin | Use                                 | Load                                              |

|---------|-----|-------------------------------------|---------------------------------------------------|

|         | E2  | Unregulated positive supply voltage | 7 m <b>A</b>                                      |

|         | C2  | Ground                              |                                                   |

| OUTPUT: |     |                                     |                                                   |

|         | Pin | Use                                 | Load                                              |

|         | H2  | AC LO                               | Low: Sink 20 mA<br>≤ 0.3V<br>High: Open collector |

|         | F2  | DC LO                               | Low: Sink 20 mA<br>≤ 0.3V<br>High: Open collector |

#### 3.4.8 M111 Inverter

The M111 contains sixteen independent inverters.

**INPUTS:** Voltage levels of OV and +3V (typical). Each input presents one TTL

unit load.

**OUTPUTS:** Voltage levels of 0V and +3V (typical). Each output can drive 10

TTL unit loads.

**POWER:** 87 mA (max) at +5V.

#### **3.4.9 M113 2-Input NAND Gate**

The M113 contains ten 2-input NAND gates used for general-purpose gating functions. The module also contains a divider network so that any unused inputs of a gate can be connected to +3V for maximum noise immunity. Pins U1 and V1 are provided for this function; each can supply up to 40 TTL unit loads.

**INPUTS:** Voltage levels of OV and +3V (typical). Each input presents 1 TTL

unit load.

**OUTPUTS:** Voltage levels of 0V and +3V (typical). Each output can drive 10

TTL unit loads.

**Propagation Delay:** 15 ns (typical)

**POWER:** 71 mA (max) at +5V

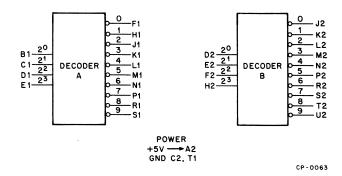

#### 3.4.10 M163 Dual Binary-To-Decimal Decoder

The M163 consists of two independent binary-to-decimal decoding structures on a single-height module (see Figure 3-14). Each decoder produces a negative-true (0V) output for the decimal equivalent of the binary input.

Figure 3-14 M163 Decoder Simplified Diagram

Each decoder can also be used for octal or quad decoding by grounding the most significant bit (MSB) line or MSB and next MSB input lines. Each decoder has a propagation delay of 40  $\mu$ s (maximum) for input-to-output turn-on or turn-off.

**INPUTS:** Voltage levels of 0V and +3V (typical). All inputs present 1 TTL unit

load each.

**OUTPUTS:** Voltage levels of OV and +3V (typical). All outputs are capable of

driving 10 TTL unit loads.

POWER: 58:

58 mA (typical) at +5V.

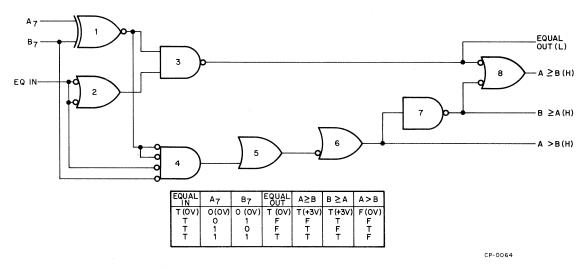

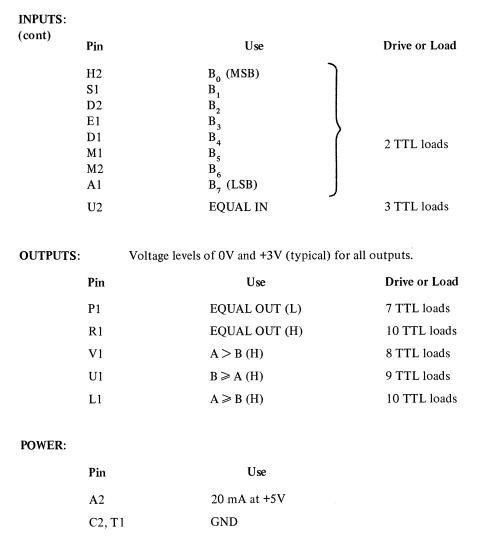

#### 3.4.11 M167 Magnitude Comparator

The M167 module compares the magnitude of two 8-bit binary numbers and provides four outputs defining the relationships of these numbers. For example, for two numbers designated A and B, the comparator defines whether A = B, A > B, or  $B \ge A$ . In addition, an EQUAL IN input enables cascading of modules so that comparison can be performed for greater than 8-bit numbers. For the comparison of less than 8-bit numbers, unused comparison inputs are connected to +3V and the EQUAL IN input is connected to ground.

The basic logic structure for a binary stage consists of an EXCLUSIVE OR, two 2-input NAND/NOR gates (one used as an inverter) and one 4-input NAND/NOR as shown in Figure 3-15. The remaining logic elements in Figure 3-15 are common to all stages. A truth table is provided for the stage; it assumes all higher order inputs are equal (EQUAL IN in 0V).

Figure 3-15 M167 Comparator Simplified Diagram

A principle use of this module is to compare track addresses for a write lockout function. For this application, a track address is connected to the "A" input, write lockout switch levels are connected to the "B" inputs, and the A > B output controls the write operation. With this arrangement, a write operation is disabled whenever the track address is equal to or less than the write lockout switch setting. In addition, the write lockout function can be disabled entirely by simulating a track address-greater-than-switch input to the MSB stage. For this function, the MSB "B" input is connected to ground and the MSB "A" input is switched to +3V. Conversely, to enable the write lockout function, the MSB "A" input need only be switched to 0V.

**INPUTS:** Voltage levels of 0V and +3V (typical) for all TTL inputs.

| Pin                                          | Use                                                                                                                                 | Drive or Load |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|

| F2<br>H1<br>E2<br>F1<br>C1<br>J1<br>K1<br>B1 | A <sub>0</sub> (MSB) A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> A <sub>5</sub> A <sub>6</sub> A <sub>7</sub> (LSB) | 1 TTL load    |

|                                              | •                                                                                                                                   |               |

#### 3.4.12 M205 D-Type Flip-Flop

The M205 module contains five D-type flip-flops. Each flip-flop has independent DATA, CLOCK, SET, and CLEAR inputs. Information must be present on the DATA input 20 ns (maximum) before the CLOCK pulse and the information should remain at the input at least 5 ns (maximum) after the CLOCK pulse has passed the threshold voltage. Data transferred into the flip-flop by the previous CLOCK pulse will be present on the 1 output of the flip-flop. Typical time duration of the CLOCK pulse preset and reset pulses is 30 ns each. Maximum delay through the flip-flop is 50 ns.

INPUTS: D inputs present 1 TTL unit load each.

C inputs present 2 TTL unit loads each.

SET inputs present 2 TTL unit loads each.

CLEAR inputs present 3 TTL unit loads each.

OUTPUTS: Each output (0 and 1) is capable of driving 10 TTL unit loads. Two +3V supplies (U1 and V1), capable of 25 unit loads, are available.

**POWER:** 100 mA (maximum) at +5V.

#### 3.4.13 M623 Bus Driver

The M623 module contains twelve 2-input bus drivers capable of driving the positive input bus of a computer. Drivers are arranged in six pairs, with each pair having a common gating line and two data bit inputs. For simultaneous gating of data bits, the common gating lines of each pair are connected to a single gating source. For direct output (without gating), the common gating lines are connected to signal ground. The driver output is then at ground when both inputs are at ground. Output rise and fall times are 30 ns (maximum) for a 100-mA resistive load.

INPUTS: Pins C1, J1, P1, F2, M2, and T2 present two unit loads, when used for

pair gating. Pin C1 presents 12 unit loads when connected to all other common gating lines. Pins A1, B1, F1, H1, M1, N1, D2, E2, K2, L2,

R2 and S2 each present one unit load.

**OUTPUTS:** All outputs can sink 100 mA to ground. An open-collector NPN trans-

istor is used as an output stage, and all output lines are protected from negative voltage of -0.3V or greater. A maximum collector voltage of

+20V can be used.

**POWER:** 71 mA at +5V (max) plus external load.

#### 3.4.14 M901 Flat Mylar Cable Connector

This connector module allows 36 lines to be used for signals and grounds. The 100-ohm resistors connected in series with pins A2, B2, U1, and V1 provide some measure of protection if these pins are inadvertently connected to a source voltage.

**INPUTS:** Recommended current per line is 100 mA maximum.

#### 3.4.15 M908 Ribbon Connector

The M908 cable connector consists of a single-height, double-sided board that contains 36 split pins for the connection of 36 separate wires. All connections are made on the component side of the module.

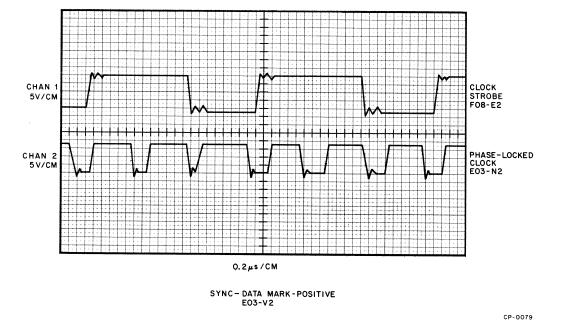

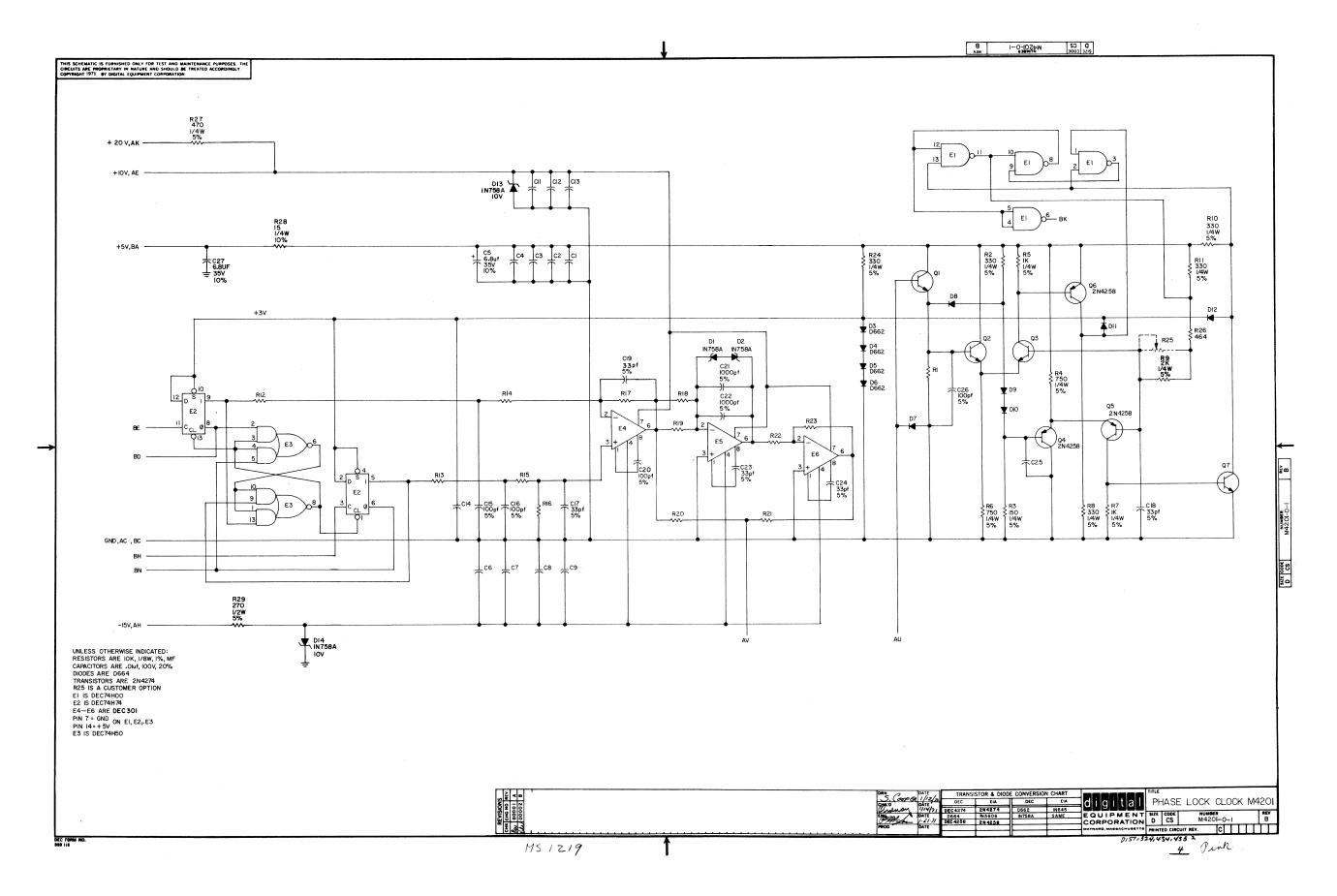

#### 3.4.16 M4201 Phase-Locked Clock

3-10

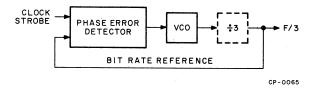

The M4201 clock synchronizes disk read/write operations with the bit timing strobes recovered from a disk timing track. Basically, it consists of a phase error detector and a VCO operated in a self-synchronizing phase-lock loop as shown in Figure 3-16.

Figure 3-16 M4201 Phase-Locked Clock Simplified Diagram

The VCO has a natural (or center) frequency of approximately 3.6 MHz; it drives an external divide-by-3 counter that provides a bit rate reference for the phase-lock loop. A phase error detector compares the time occurrence of the clock strobes from a disk with the bit rate reference. Errors resulting from the comparison are then integrated and converted to an analog voltage that adjusts the VCO frequency accordingly. This loop synchronizes the VCO with the clock strobes within a nominal  $300 \mu s$ .

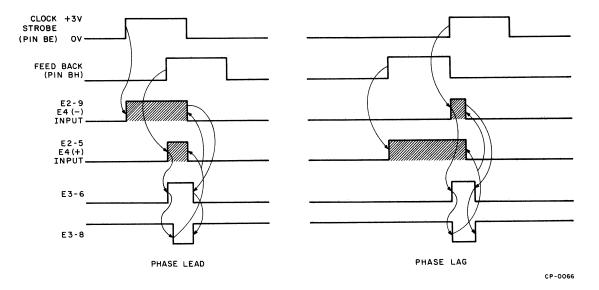

The phase error detector consists of a digital comparator stage, fast-integrator E4, long-term integrator E5, and linear amplifier E6, as shown in Drawing D-CS-M4201-0-1. The digital comparator stage consists of two D-type flip-flops in IC E2 and a NAND latch in IC E3. These logic elements accept the clock strobe input (pin BE) and bit rate reference input (pin BH) and generate pulse outputs that drive the differential inputs of E4. Figure 3-17 shows the waveforms produced by these logic elements for both a phase lead and a phase lag. The shaded areas depict the error inputs applied to the differential inputs of E4. The output of E4 is proportional to the difference between the two inputs and thus represents the bit-by-bit phase error. Integrator E5, in turn, averages the bit-by-bit phase error for long-term stability. The outputs of E4 and E5 are added. The output at AV2 thus contains a component from E4 that corrects phase errors and a component from E5 that provides frequency lock. Amplifier E6 functions as a unity-gain inverting amplifier to provide the correct drive to VCO. Its output at pin AV2 is negative for a phase lead and positive for phase lag.

Figure 3-17 M4201 Phase-Locked Clock Waveforms

The VCO is a discrete-component RC oscillator consisting of transistor stages Q1 through Q7. It has a natural frequency of approximately 3.6 MHz (determined primarily by the network comprised of C18, R9, R26, and R11). Integrated circuit E1 buffers the VCO output and provides the necessary output drive. The clock output at pin BK is a square wave with a near 50 percent duty cycle.

| INPUTS: | Voltage levels of 0V and +3V (typical) |                                  |               |

|---------|----------------------------------------|----------------------------------|---------------|

| Pin U   |                                        | Use                              | Drive or Load |

|         | BE2                                    | Clock Strobe                     | 1 TTL load    |

|         | BH2                                    | Feedback (Bit Rate<br>Reference) | 1 TTL load    |

**OUTPUTS**: Voltage levels of 0V and +3V (typical) for all digital outputs.

Pin Use

BK2 Phase Lock Clock

BD2 Digital Comparator Test Point

OUTPUTS:

(cont) Pin Use

BN2 Digital Comparator Test Point

AV2 Phase Detector Analog Output

AU2 VCO Control Input

**CLOCK STABILITY:** Phase jitter between clock strobe and phase-lock clock is less

than 100 ns.

**SYNCHRONIZING TIME:** 300  $\mu$ s or less

#### POWER:

| Pin    | Use           |

|--------|---------------|

| AK2    | 15 mA at +20\ |

| BA     | 100 mA at +5\ |

| AH     | 10 mA at -15V |

| AC, BC | GND           |

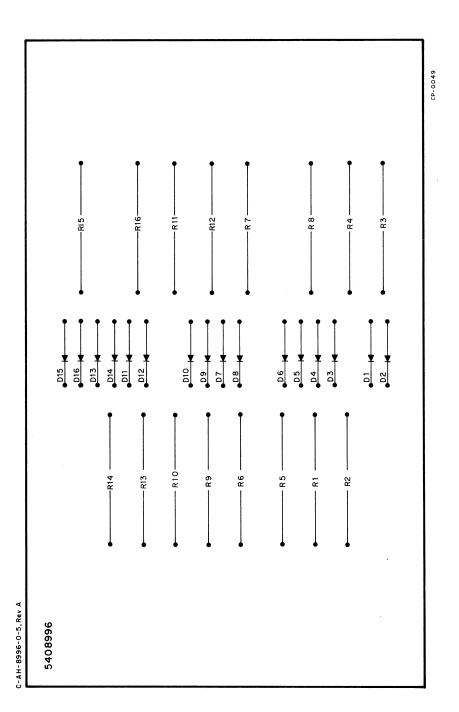

#### 3.4.17 8-Track Matrix 5408996

This module is part of a data cable assembly that connects the track selection logic to the data track read/write heads. It contains current-limiting resistors and isolation diodes for an 8-track data matrix.

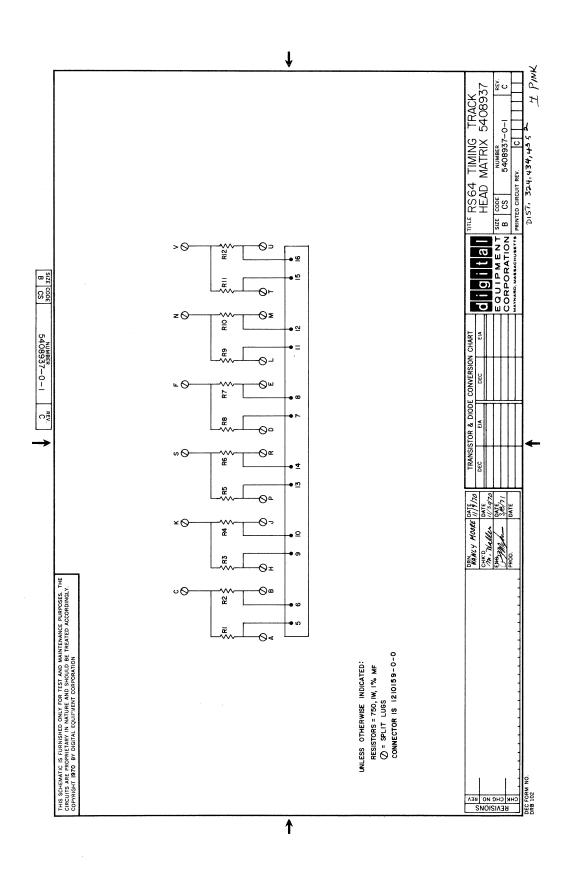

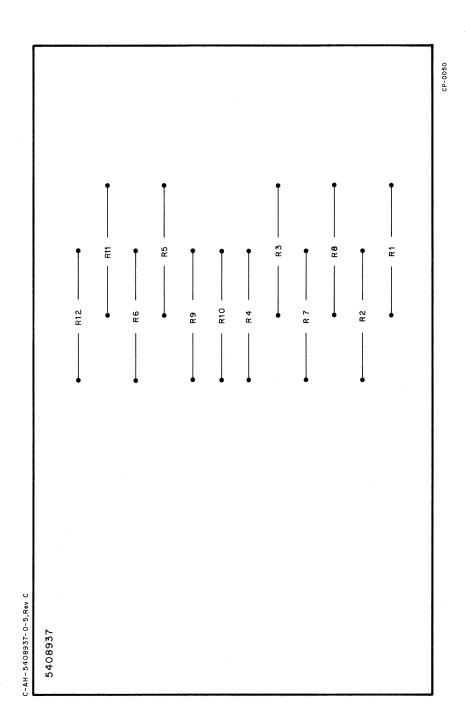

#### 3.4.18 Timing Head Matrix 5408937

This connector module is part of a timing cable assembly that connects the timing head shoe to the read amplifier-peak detector modules. It contains current-limiting resistors and connections for six timing heads.

### CHAPTER 4 INTERFACING

#### 4.1 BUS VOLTAGE SPECTRUM

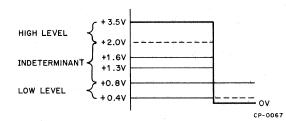

The recommended voltage spectrum for an RS64 controller interface is shown in Figure 4-1.

Figure 4-1 Voltage Spectrum for Controller Bus

#### 4.2 BUS PHILOSOPHY

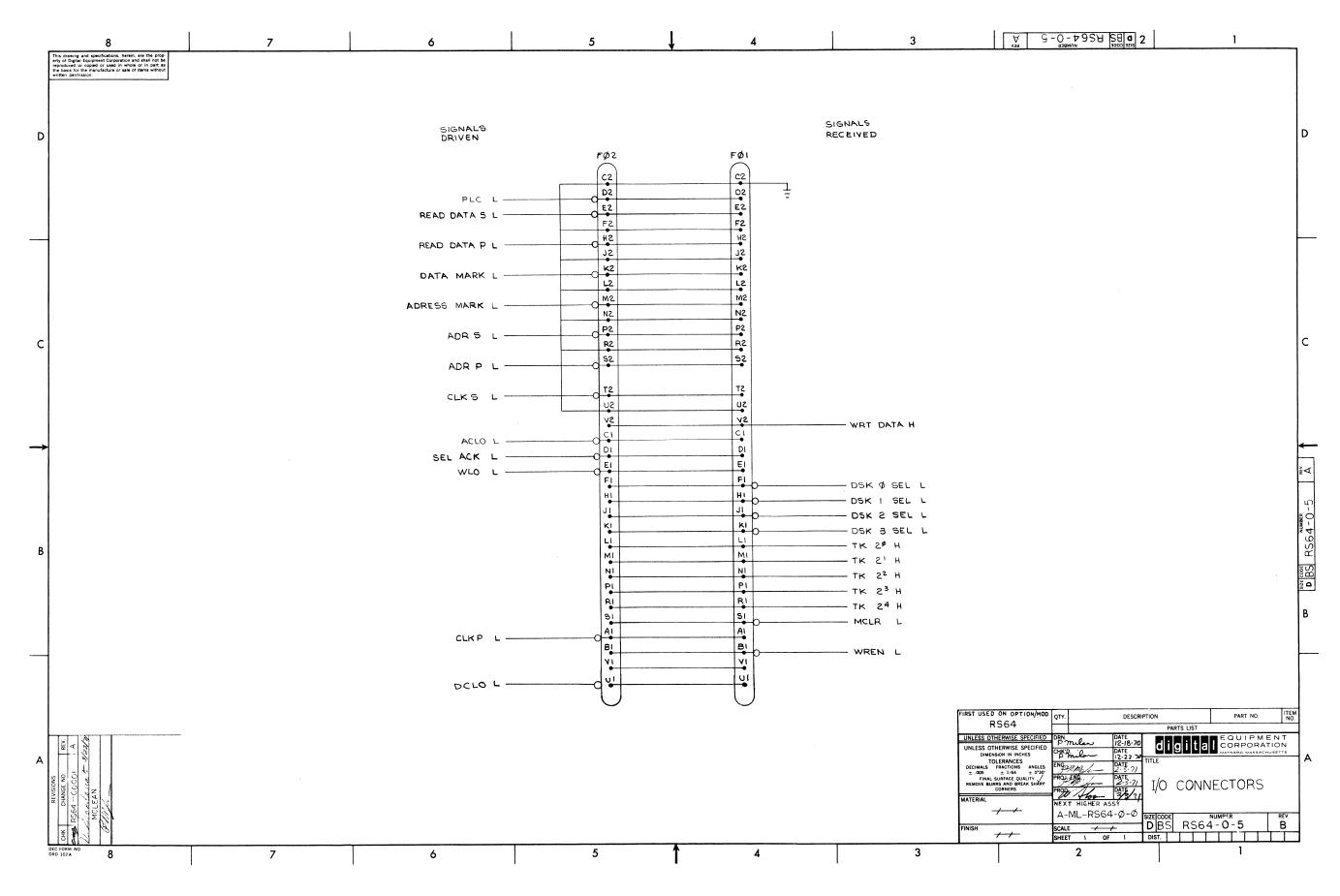

A cable assembly consisting of two 19-conductor flat Mylar cables is used for the RS64 controller bus. One cable should be used to convey 10 "fast" bus signals, i.e., signals that convey information via a signal transition or that can be 100 ns or less in duration. This cable should have alternate signal and ground conductors and be terminated with 82 ohms to +5V at the RS64 and 82 ohms to ground at the controller as shown in Figure 4-2.

Figure 4-2 "Fast" Bus Configuration

The second 19-conductor cable should be used to convey 16 "slow" bus signals, i.e., signals that are strobed by the "fast" signals or used only as a level. These signals should be terminated by 180 ohms to +5V and 330 ohms to ground at each end of the cable as shown in Figure 4-3.

Figure 4-3 "Slow" Bus Configuration

The two cables should be separated by a solid Mylar shield and attached to one M901 connector at one end to form an assembly capable of handling at least 24 signals. Signal polarity is chosen to minimize logic and to make the bus fail-safe for a power failure or unplugging of the bus cable.

#### 4.3 INTERFACE SIGNALS

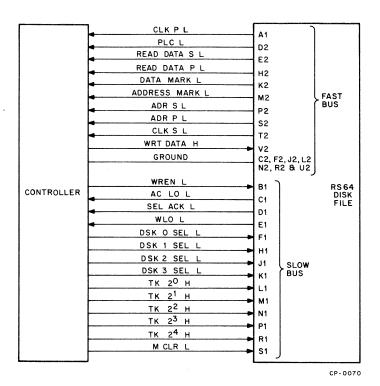

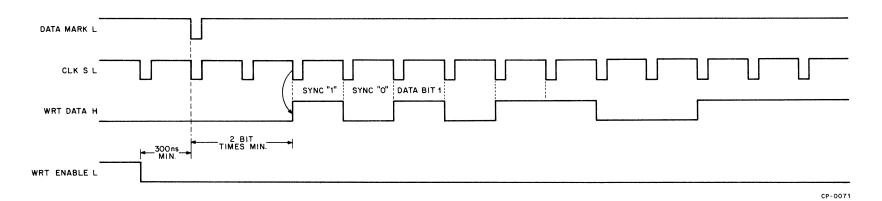

Figure 4-4 defines: (a) the signals for an RS64-controller interface, (b) the signal assertion level, (c) the source of the signal and (d) the pin usage at the RS64 Disk File end. Each interface signal is described in subsequent paragraphs.

#### 4.3.1 Disk Select (DSK SEL) 0-3

Up to four disk files can be used with one controller, thus each file must be assigned a unit number. Each RS64 has a 5-position rotary switch (0-3 and OFF) for assigning a unit number or placing the unit off-line. The four DSK SEL lines are wired to corresponding positions on this switch. To select a disk for a read or write operation, the controller ground-asserts the select line corresponding to the disk unit number. No interlocks are provided to prevent multiple disk files from being assigned the same unit number.

#### 4.3.2 Select Acknowledge (SEL ACK)

This signal indicates that a disk file (or files) has been selected and that the selected unit does not have a power-fail condition. This line is negative-true (0V) for a select acknowledge condition.

Figure 4-4 RS64 Controller Interface

#### 4.3.3 Track Select (TK SEL) $2^0 - 2^4$

These five binary-weighted lines select one of  $32 (00_8 - 37_8)$  data tracks for a read or write operation. Each disk file decodes these lines regardless of the file selected. Positive-true inputs are used.

#### 4.3.4 Write Lockout (WLO)

This signal denotes that the write lockout feature is enabled for the selected track. This signal is negative-true (0V) for a write lockout condition.

#### 4.3.5 Clock Strobe (CLK S)

This signal line conveys the bit timing information recovered from the disk. The negative-going leading edge of each 300-ns pulse occurs at the peak of the recovered data (at each transition).

#### 4.3.6 Clock Polarity (CLK P)

This signal indicates the polarity of the peak for each clock strobe. A negative-true (0V) pulse denotes a positive peak and the absence of a pulse denotes a negative peak. The clock polarity pulse can be strobed by the leading edge of the clock strobe for error detection since two or more successive pulses of the same polarity indicate an error.

#### 4.3.7 Address Mark

This signal line conveys 300-ns pulses denoting the start of the address portion of a sector. The leading edge of each negative-true pulse corresponds to the peak of the address mark recovered from the disk.

#### 4-2

#### 4.3.8 Data Mark

This signal line conveys 300-ns pulses denoting the start of a data sector. The leading edge of each negative-true pulse corresponds to the peak of the data mark recovered from the disk.

#### 4.3.9 Address Strobe (ADR S)