# DEC STD 032 VAX Architecture Standard

# INTEROFFICE MEMORANDUM

DATE: 15-Jan-1990

**DEPT: Standards & Methods**

EXT: 287-3724

LOC/MS: CTS1-2/D4 ENET: JOKUR::SMC

To: Holders of A-DS-EL00032-00

Holders of Complete Sets of DEC Standards

Subj: Document Revision

Enclosed is a new update to DEC STD 032, A-DS-EL00032-00-0. This document has been completely revised, so please remove the text and tabs from your current manual and replace with the new enclosed material.

If you require more information or wish to be removed from distribution please contact Standards & Methods control at DTN 287-3724 or JOKUR::SMC.

If you no longer require the enclosed information, please return it along with your name, badge number and location so that we may remove your name from our distribution list.

DOCUMENT IDENTIFIER

A-DS-EL00032-00-0 REV J

DOCUMENT TITLE

DEC STD 032 VAX ARCHITECTURE STANDARD

ECO No: EL00032-00-CTS08 EEEEEE CCCC 0000 Ε C 0 0 TM EEEE C 0 0 d i i 1 g t a C C 0 0 EEEEEE CCCC 0000 ENGINEERING CHANGE ORDER Orig.: Richard Brunner Sheet: 1 of 2 Phone: 293-5364 Date Received: 15-Dec-1989 Loc.: **BXB1-1** MS: E11 Cost Center No.: 31L Final Issue: 15-Dec-1989 Unit(s) to be changed: EL-00032-00 Prod. Families Affected: N/A ECO Type Code: Category: Standard FCC Req.: No F/S Affected: No FCO Req.: No LOU Code: N/A Where Used: A-DS-EL00032-00-0 Documentation Affected: A-DS-EL00032-00-0, DEC STD 032-0 VAX ARCHITECTURE **STANDARD PROBLEM** Material needed updating. CORRECTION Update the standard per sheet 2 of this ECO. **BREAK-IN/EFFECTIVITY** Immediately. **APPROVAL** Phone No. Date **NAMES** C/C DTN-Ext. dd-mmm-yyyy Richard Brunner 31L 293-5364 15-Dec-1989 Standards Process Manager: Eric Williams 396 287-3696 15-Dec-1989

287-3674

15-Dec-1989

Charge Number: 098-08511 W.O. No: 192947

Coordinator:

| EBEEEE         | cc | cc   |             | 000 | ECO | No:  | ELO( | 0032 | -00- | CTSO | В | m  |

|----------------|----|------|-------------|-----|-----|------|------|------|------|------|---|----|

| E<br>EEEE<br>E | C  | C    | 0<br>0<br>0 | 0   | d   | i    | g    | i    | t    | a    | 1 | TM |

| EEEEEE         | CC | cc c | 00          | 000 | ENG | INEE | RING | СНА  | NGE  | ORDE | R |    |

#### **CONTINUATION SHEET**

Sheet: 2 of 2

| ITEM<br>NO. | PART NUMBER | DOCUMENT NUMBER   | OLD<br> REV | • |

|-------------|-------------|-------------------|-------------|---|

| 1           | EL-00032-00 | A-DS-EL00032-00-0 | H           | J |

## **DESCRIPTION:**

- Removed the SPTEP register and the ability to have system page tables in virtual memory

- Significantly clarified the sharing of memory across multiple processors and I/O devices

- Expanded the discussion of instruction-stream coherency

- Added the description of the VAX Vector processor

- Added Address Space Numbers

- Clarified the possible physical address modes and what processor features each mode allows

## DEC STD 032-0 VAX ARCHITECTURE STANDARD

DOCUMENT IDENTIFIER: A-DS-EL00032-00-0 Rev J, December 15, 1989

ABSTRACT: The VAX Architecture Standard is the definition of the

VAX architecture. It specifies the operations provided by all VAX processors, and specifies constraints on software intended to run on VAX

processors.

APPLICABILITY: This standard applies to all software written to run

VAX processors, all VAX processors, and all

"closely coupled" VAX peripherals.

STATUS: Approved 15-Dec-1989; use VTX SMC for current status.

This document is confidential and proprietary. It is an unpublished work protected under the Federal copyright laws.

Copyright (c) Digital Equipment Corporation. 1989. All rights reserved

Digital Internal Use Only

EL-00032-00 Digital Internal Use Only 15-Dec-1989

TITLE: DEC STD 032-0 VAX ARCHITECTURE STANDARD

A-DS-EL00032-00-0 Rev J, December 15, 1989 DOCUMENT IDENTIFIER:

REVISION HISTORY: Rev A, 10-Jul-1980

Rev B, 01-Sep-1982 Rev C, 15-Nov-1983

Rev D, 26-Mar-1985

Rev D1, 15-May-1986 ECO# LJ004 Rev E, 20-Oct-1986 ECO# LJ005 Rev F, 21-Nov-1986 ECO# LJ006 Rev H,

19-Jun-1987 ECO# LJ007 15-Dec-1989 ECO# CTS08 Rev J,

Document Management Group: VAX System Architecture and Interconnect (SHV)

Responsible Department: Systems Architecture Group

Responsible Person: Richard A. Brunner

APPROVAL: This document has been reviewed and approved by the VAX

architect and by the manager of the Systems Architecture

Group.

Richard A. Brunner, VAX Architect

Audrey Rerth, Systems Architecture Manager

Eric Williams, Standards Process Manager

Questions about the VAX architecture can be answered in the EAGLE1:: VAX notes conference or by contacting:

> Rich Brunner BXB1-1/E11 EAGLE1::SRM

Use VTX SMC to order copies of this document from Standards and Methods Control. Send distribution questions to JOKUR:: SMC or call DTN: 287-3724.

A variant of this document is available to customers:

VAX Architecture Reference Manual Order number EY-3459E-DP Digital Press Digital Equipment Corporation 12 Crosby Drive Bedford MA 12730

## CONTENTS

**PREFACE**

| CHAPTER | 1                                                                                   | BASIC ARCHITECTURE                          |

|---------|-------------------------------------------------------------------------------------|---------------------------------------------|

|         | 1.1<br>1.2<br>1.3                                                                   | ADDRESSING                                  |

| CHAPTER | 2                                                                                   | INSTRUCTION FORMATS AND ADDRESSING MODES    |

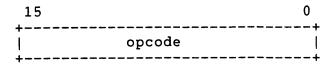

|         | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                              | OPCODE FORMATS                              |

| CHAPTER | 3                                                                                   | INSTRUCTIONS                                |

|         | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12 | NOTATION                                    |

|         | 3.13                                                                                | DECIMAL-STRING INSTRUCTIONS                 |

|         | 4.1<br>4.2<br>4.3                                                                   | WEMORY MANAGEMENT  VIRTUAL ADDRESS SPACE    |

| CHAPTER | 5<br>5.1<br>5.2<br>5.3<br>5.4                                                       | INTERRUPTS AND EXCEPTIONS  PROCESSOR STATUS |

|         | 5.5<br>5.6<br>5.7<br>5.8<br>5.9                 | SYSTEM CONTROL BLOCK                                                 |

|---------|-------------------------------------------------|----------------------------------------------------------------------|

| CHAPTER | 6                                               | PROCESS STRUCTURE                                                    |

|         | 6.2                                             | PROCESS CONTEXT                                                      |

| CHAPTER | 7                                               | MEMORY AND I/O                                                       |

|         | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                 | MEMORY, MULTIPROCESSING, AND INTERPROCESSOR COMMUNICATION            |

| CHAPTER | 8                                               | PRIVILEGED REGISTERS                                                 |

|         | 8.2                                             | PER-PROCESS REGISTERS AND CONTEXT SWITCHING 8-1 STACK-POINTER IMAGES |

| CHAPTER | 9                                               | PDP-11 COMPATIBILITY MODE                                            |

|         | 9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11 |                                                                      |

| CHAPTER | 10                                              | SYSTEM BOOTSTRAPPING AND CONSOLE                                     |

|         | 10.5                                            | SYSTEM RESTART                                                       |

| CHAPTER | 11                                                   | IMPLEMENTATION OPTIONS                                                                                                                                                                                                                                                                             |

|---------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11.2                                                 | INSTRUCTION-SET OPTIONS                                                                                                                                                                                                                                                                            |

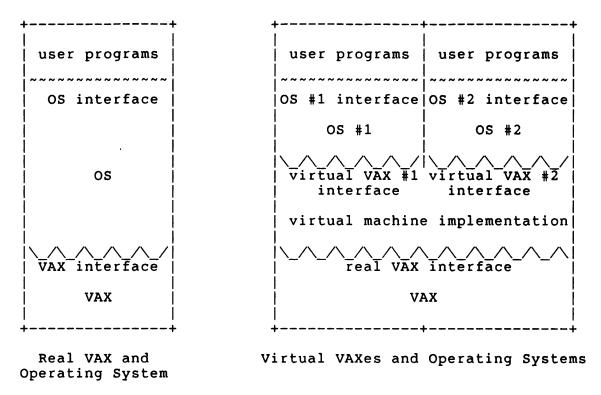

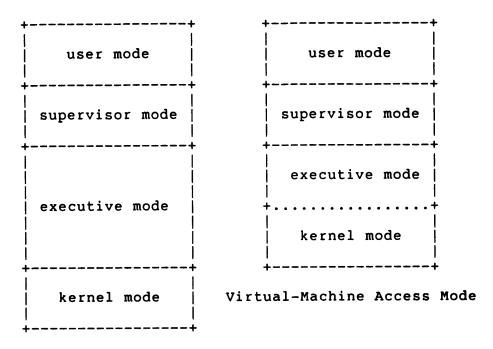

| CHAPTER | 12                                                   | VIRTUAL MACHINES                                                                                                                                                                                                                                                                                   |

|         | 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7 | VIRTUAL-MACHINE STATE                                                                                                                                                                                                                                                                              |

| CHAPTER | 13                                                   | VAX VECTOR REGISTERS AND INSTRUCTIONS                                                                                                                                                                                                                                                              |

|         | 13.10                                                | INTRODUCTION                                                                                                                                                                                                                                                                                       |

| CHAPTER | 14                                                   | VAX VECTOR EXECUTION MODEL AND EXCEPTION REPORTING                                                                                                                                                                                                                                                 |

|         | 14.1<br>14.2<br>14.3<br>14.4<br>14.5                 | EXECUTION MODEL                                                                                                                                                                                                                                                                                    |

| APPENDI | X A                                                  | OPCODE ASSIGNMENTS                                                                                                                                                                                                                                                                                 |

| APPENDI | х в                                                  | IMPLEMENTATION DEPENDENCIES                                                                                                                                                                                                                                                                        |

|         | B.5<br>B.6<br>B.7<br>B.8<br>B.9<br>B.10              | IMPLEMENTATION OPTIONS       B-1         MICROVAX I       B-1         MICROVAX II       B-1         VAX-11/725       B-1         VAX-11/730       B-1         VAX-11/750       B-2         VAX-11/780       B-3         VAX-11/782       B-4         VAX 8200       B-3         VAY 9300       B-3 |

| в.12       | VAX 8500                                  | B-9 |

|------------|-------------------------------------------|-----|

| B.13       | VAX 8600                                  | B-9 |

| B.14       | VAX 8650                                  | B-9 |

| B.15       | VAX 8700                                  | -10 |

| B.16       | VAX 8800                                  | -10 |

| B.17       | VVAX                                      | -10 |

| APPENDIX C | ARCHITECTURE MANAGEMENT                   |     |

| c.1        | RESPONSIBILITIES                          | C-1 |

| C.2        | SPECIFICATION DISTRIBUTION                |     |

| ′ C.3      | CONFORMANCE AND WAIVERS                   | C-4 |

| C.4        | ECO PROCESS                               | C-5 |

| C.5        | SYSTEMS-ARCHITECTURE-GROUP SPECIFICATIONS | Z-8 |

|            |                                           |     |

INDEX

# FIGURES

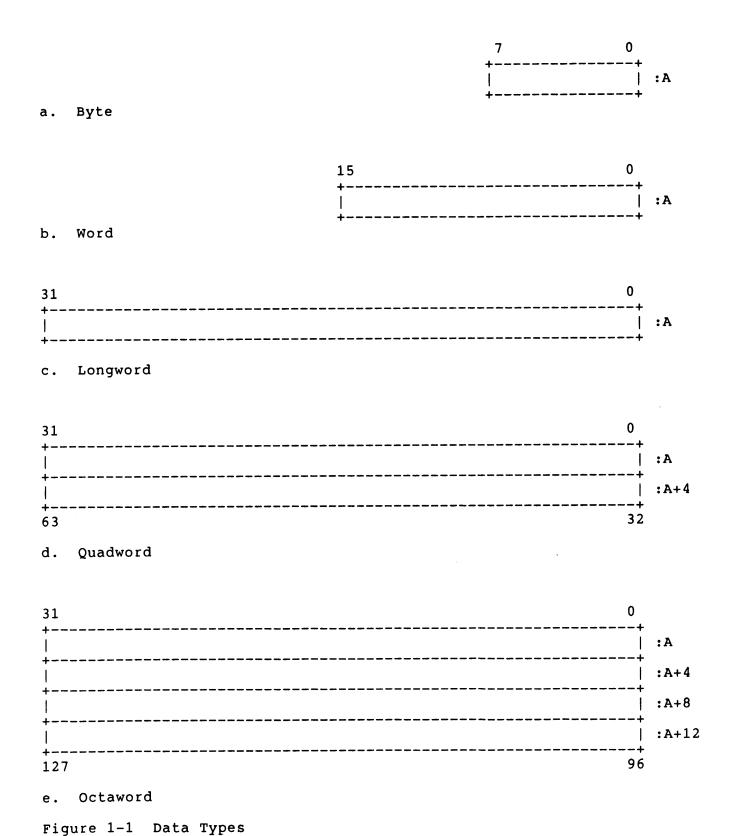

| 1-1   | Data Types                                      | . 1-5 |

|-------|-------------------------------------------------|-------|

| 1-2   | Floating-Point Data Types                       | . 1-8 |

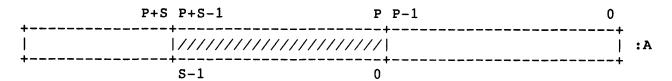

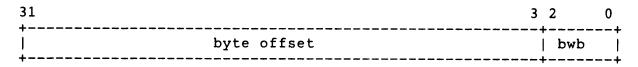

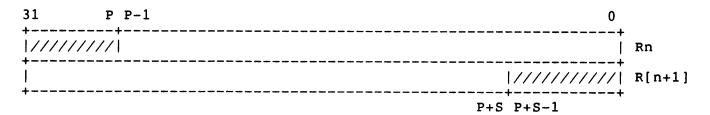

| 1-3   | Variable-Length Bit Fields                      | 1-11  |

| 1 – 4 | Absolute Queues                                 | T-T3  |

| 1-5   | Self-Relative Oueues                            | 1-15  |

| 1-6   | Character-String Data Type                      | 1-19  |

| 1 7   | Docimal Strings                                 | 1-21  |

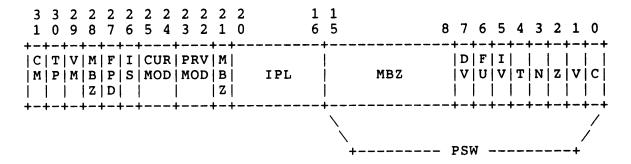

| 1-8   | Processor State                                 | 1-25  |

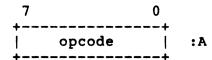

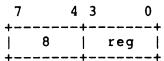

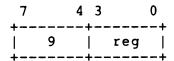

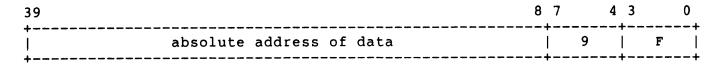

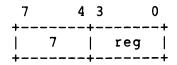

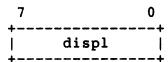

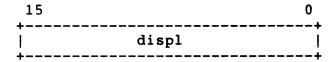

| 2-1   | Opcodes and Operand Specifiers                  | . 2-2 |

| 2-2   | Addressing-Mode Specifiers                      | . 2-5 |

| 2-3   | Processor State                                 | 2-11  |

| 2-4   | interpretation of a biteral                     | 2-12  |

| 2-5   | Indexed Specifier and Extension                 | 2-16  |

| 2-6   | Branch-Mode Specifiers                          | 2-16  |

| 3-1   | Procedure Entry Mask                            | 3-72  |

| 3-2   | Procedure-Call Stack Frame                      | 3-72  |

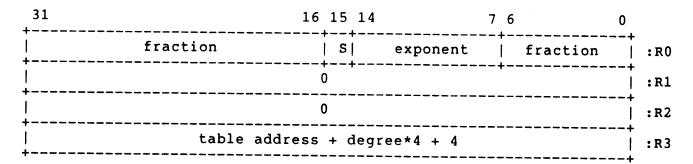

| 3-3   | Pagult Pagisters After POLVE                    | 3-140 |

| 3-4   | Result Registers After POLYD                    | 3-140 |

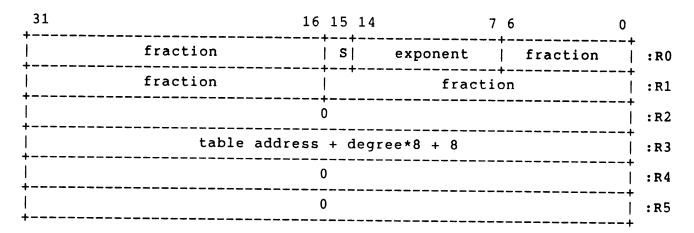

| 3-5   | Result Registers After POLYD                    | 3-140 |

| 3-6   | Result Registers After POLYH                    | 3-141 |

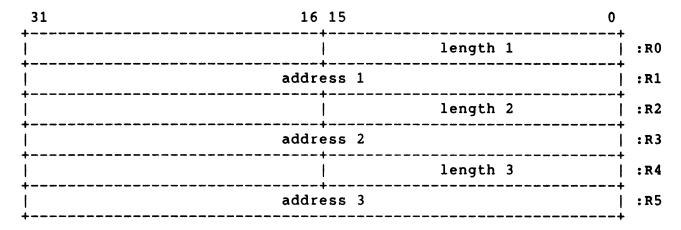

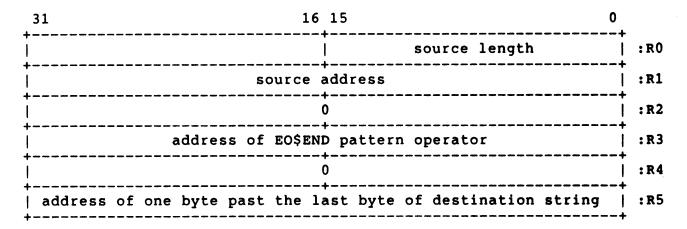

| 3-7   | Character-String-Instruction Control Block      | 3-152 |

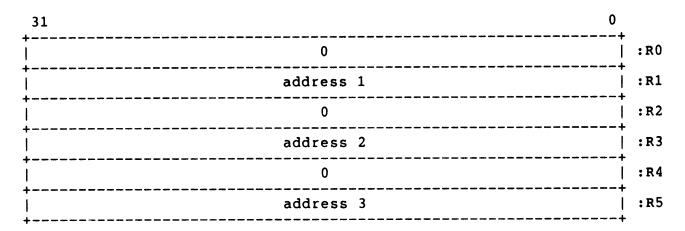

| 3-8   | Decimal-String-Instruction Control Block        | 3-184 |

| 3-9   | EDITPC Control Block                            | 3-220 |

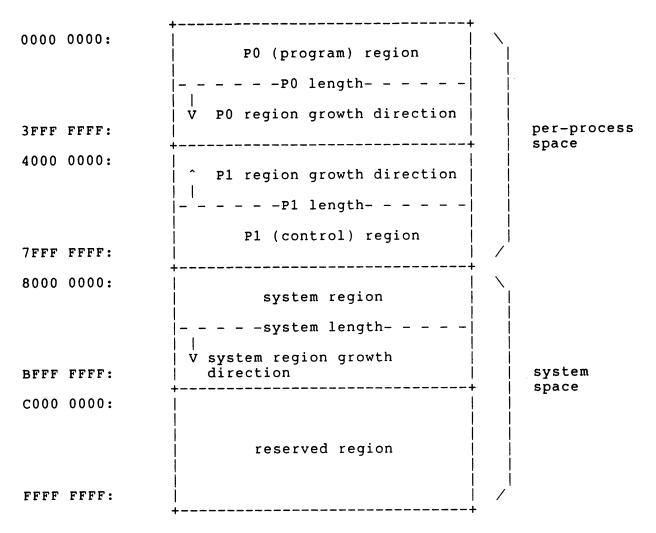

| 4-1   | Virtual-Address Space                           | . 4-3 |

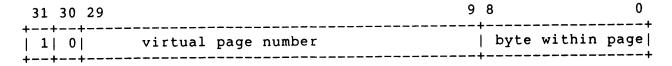

| 4-2   | Virtual-Address Format                          | . 4-3 |

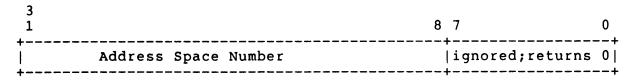

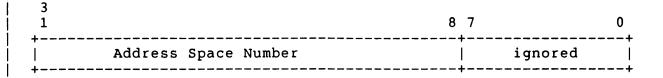

| 4-3   | Address Space Number Register (ASN)             | . 4-5 |

| 4 – 4 | Man Enable Bogistor (MADEN)                     | 4_10  |

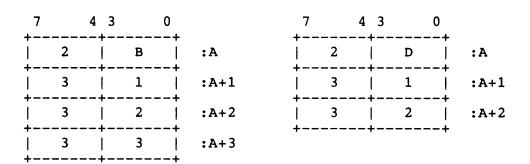

| 4-5   | Page Table Entry (25-Bit Page Frame Number)     | 4-10  |

| 4-6   | Page Table Entry (25-Bit Page Frame Number)     | 4-11  |

| 4-7   | System Virtual-Address Format                   | 4-15  |

| 4-8   | System Page-Table Mapping Registers             | 4-10  |

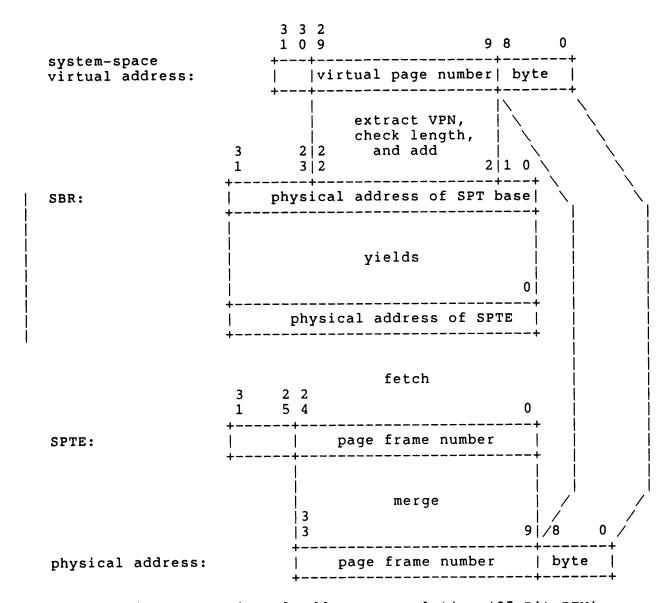

| 4-9   | System Virtual-Address Translation (25-Bit PFN) | 4-19  |

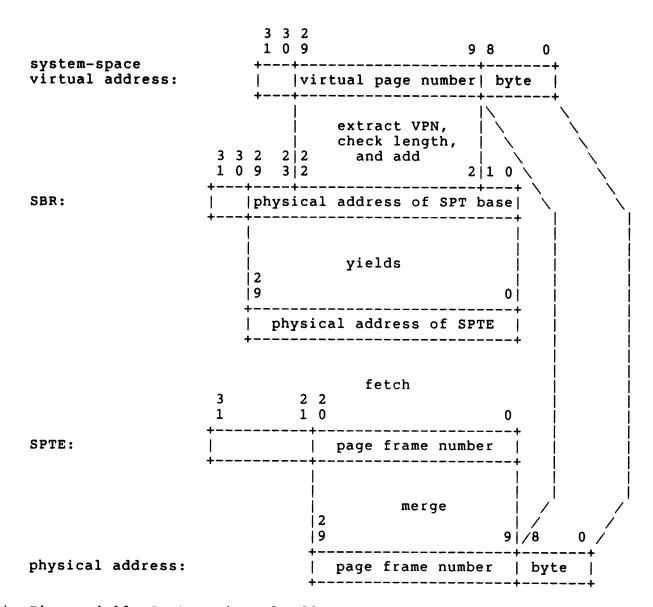

| 4-10  | System Virtual-Address Translation (21-Bit PFN) | 4-20  |

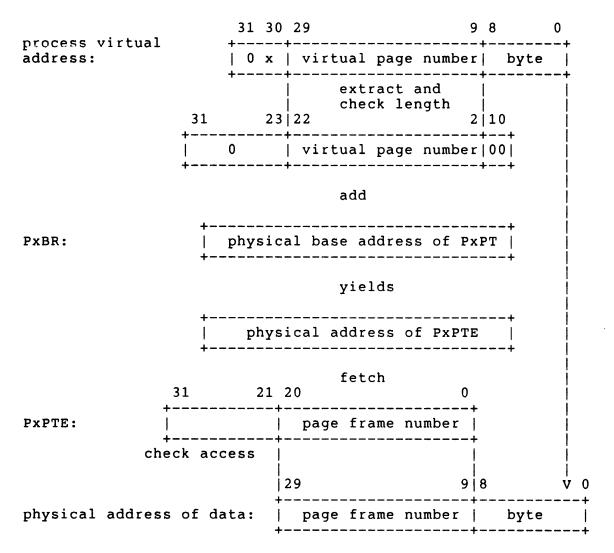

| 4-11  | Process Virtual-Address Format                  |       |

| 4-12  | Process-Space Mapping Registers                 | 4-23  |

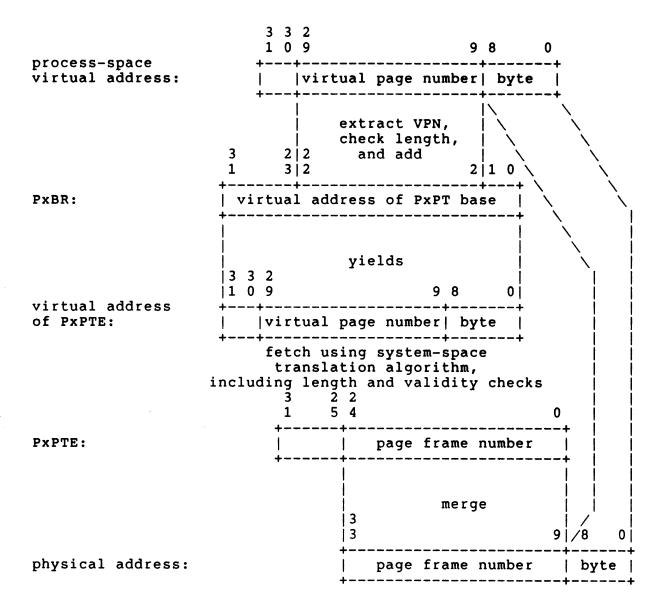

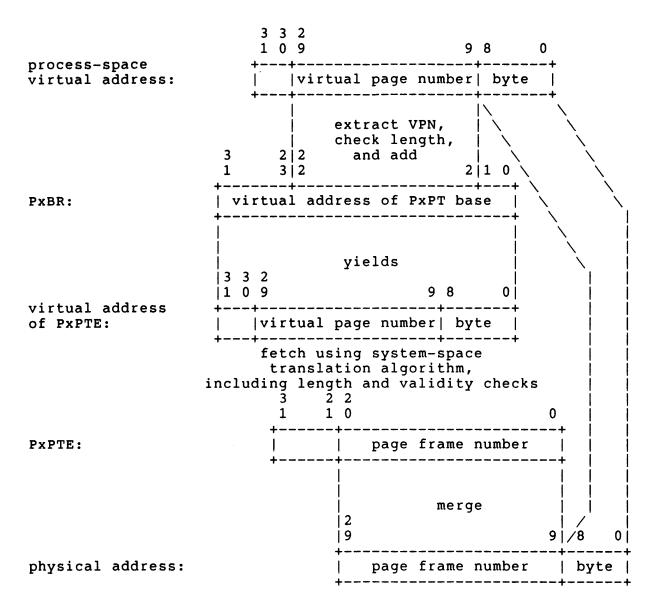

| 4-13  | Process Virtual-Address Translation             | 4-24  |

| 4-14  | TB Invalidate (based on) Address Space Number   |       |

|       | (TBIASN)                                        | 4-29  |

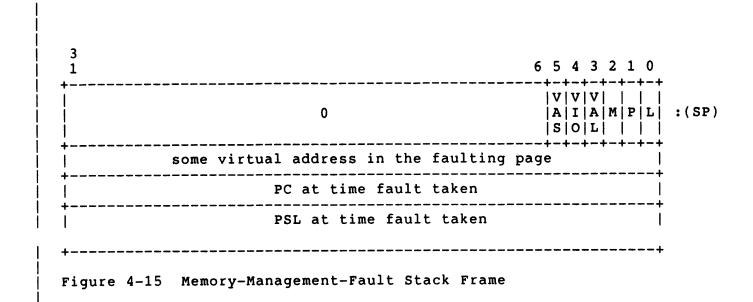

| 4-15  | Memory-Management-Fault Stack Frame             | 4-31  |

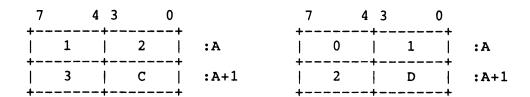

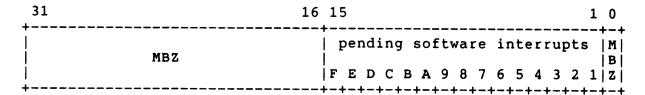

| 5-1   | Software-Interrupt Summary Register             | . 5-8 |

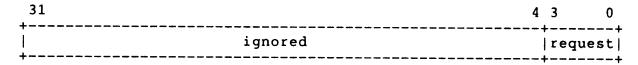

| 5-2   | Software-Interrupt Request Register             | . 5-8 |

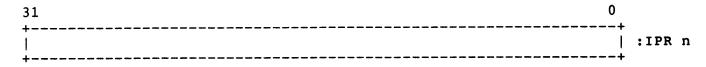

| 5-3   | Interrupt-Priority-Level Register               | . 5-8 |

| 5-4   | Arithmetic-Exception Stack Frame                | 5-10  |

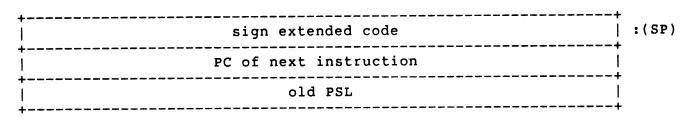

| 5-5   | CHMx Stack Frame                                | 5-20  |

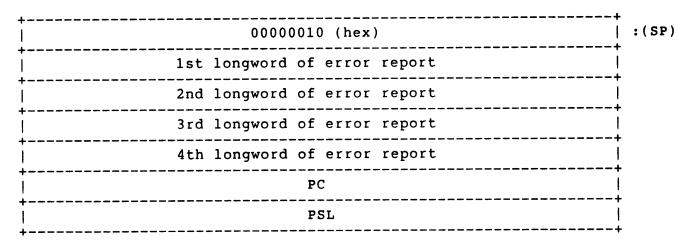

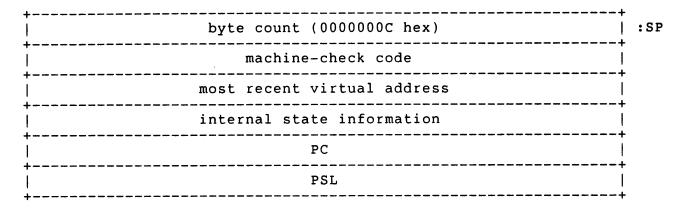

| 5-6   | An Example Machine-Check Stack Frame            | 5-20  |

| 5-7   | System Control-Block Base                       |       |

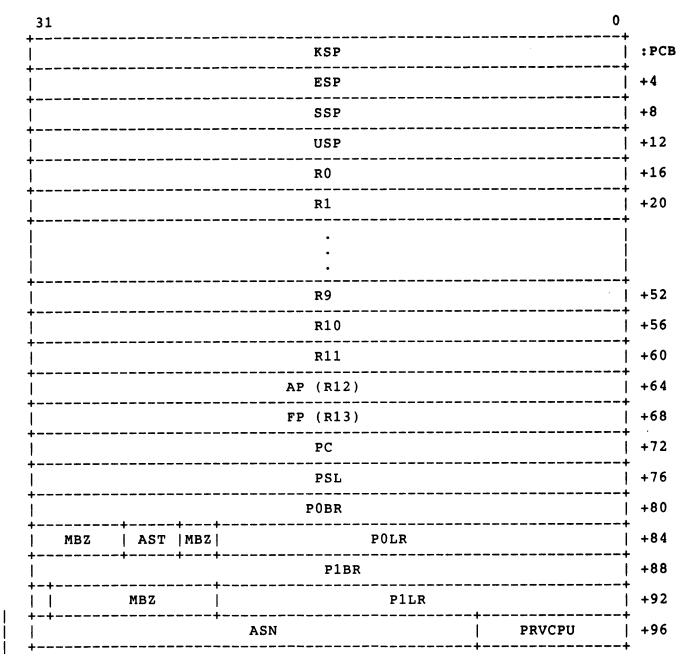

| 6-1   | Process Control Block (PCB)                     |       |

| 6-2   | Process Control-Block Base Register (PCBB)      | . 6-4 |

| 6-3   | Performance-Monitor-Enable Register (PME)       | . 6-4 |

| 6-4   | AST-Level Register (ASTLVL)                     | . 6-4 |

| 7-1   | PTEs For Use By I/O Devices                     | 7-21  |

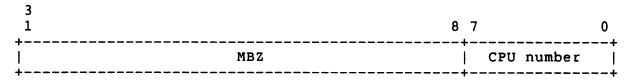

| 8-1   | CPU Identification Register (CPUID)             | 0-1/  |

| 8-2   | System Identification Register (SID)            | 8-21  |

| 8-3   | System-Type Register (SYS TYPE)                 | 8-21  |

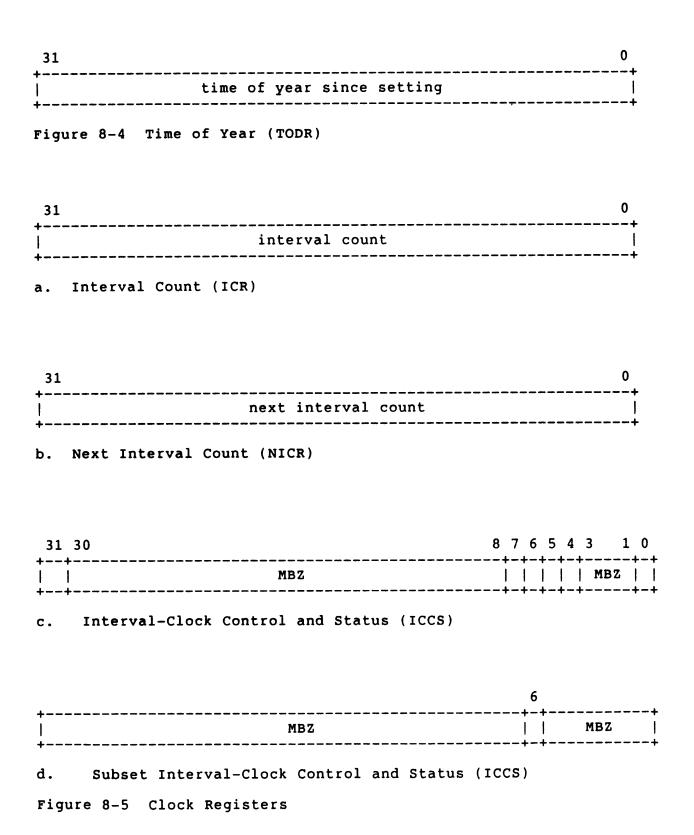

| 8-4   | Time of Year (TODR)                             | 8-24  |

| 8-5   | Clock Registers                                 | 8-24  |

| 9-1          | Compatibility-Mode Operand Specifiers                                                | . 9-5  |

|--------------|--------------------------------------------------------------------------------------|--------|

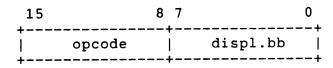

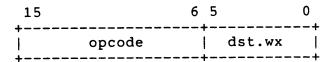

| 9-2          | Compatibility-Mode Instruction Formats                                               | . 9-8  |

| 10-1         | Restart Parameter Block (RPB)                                                        | 10-6   |

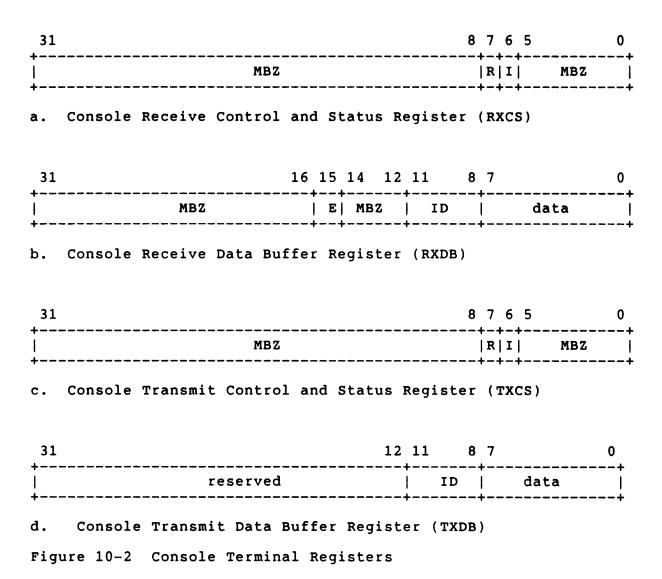

| 10-2         | Console Terminal Registers                                                           | 10-34  |

| 11-1         | rtVAX Process-Space Mapping Registers                                                | 11-7   |

| 11-2         | rtVAX Process-Space Address Translation                                              |        |

| 11-3         | Instruction-Emulation Trap Frame                                                     |        |

| 12-1         | Real VAXes and Virtual VAXes                                                         | 12-3   |

| 12-2         | Virtual-Machine PSL Register (VMPSL)                                                 | 12-4   |

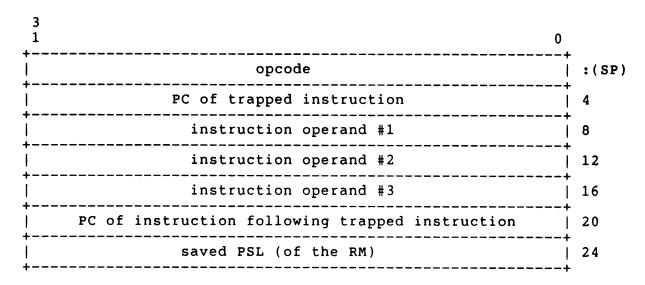

| 12-3         | VM-Emulation-Trap Stack Frame                                                        | 12-14  |

| 12-4         | VM-Emulation-Trap Stack Frame                                                        | 12-17  |

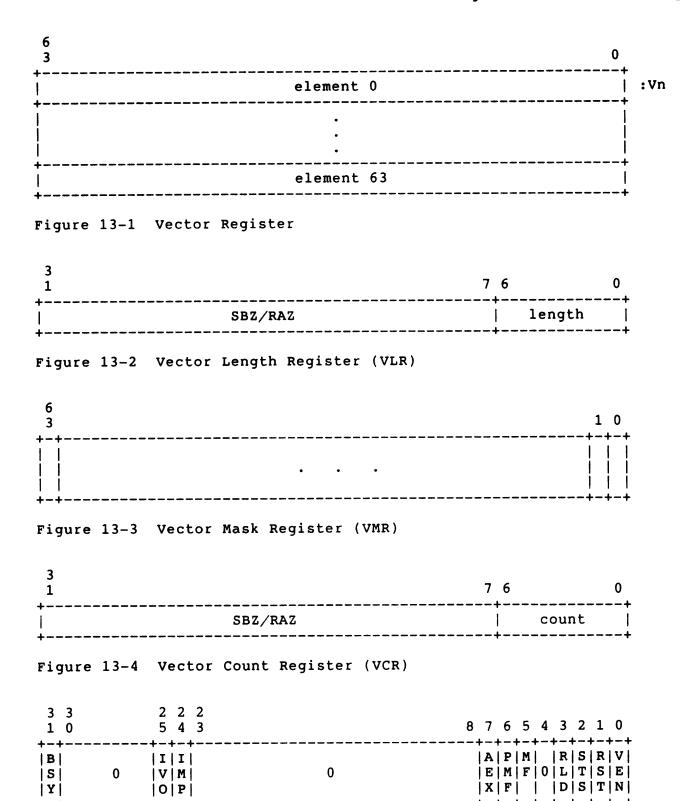

| 13-1         | Vector Register                                                                      | 13-6   |

| 13-2         | Vector Register                                                                      | 13-6   |

| 13-3         | Vector Mask Register (VMR)                                                           | 13-6   |

| 13-4         | Vector Count Register (VCR)                                                          | 13-6   |

| 13-5         | Vector Processor Status Register (VPSR)                                              | 13-6   |

| 13-6         | Vector Arithmetic Exception Register (VAER)                                          | 13-10  |

| 13-7         | Vector Memory Activity Check Register (VMAC)                                         | 13-10  |

| 13-8         | Vector Translation Buffer Invalidate All                                             | 13-10  |

| -5 0         | Register (VTBIA)                                                                     | 13_10  |

| 13-9         | Vector State Address Register (VSAR)                                                 | 13_11  |

| 13-10        | Vector Control Word Operand (cntrl)                                                  | 13_19  |

| 13-11        | Vector Control Word Format                                                           |        |

| 13-12        | Encoding of the Reserved Operand                                                     |        |

| 14-1         | Memory Management Fault Stack Frame                                                  | 1 / 10 |

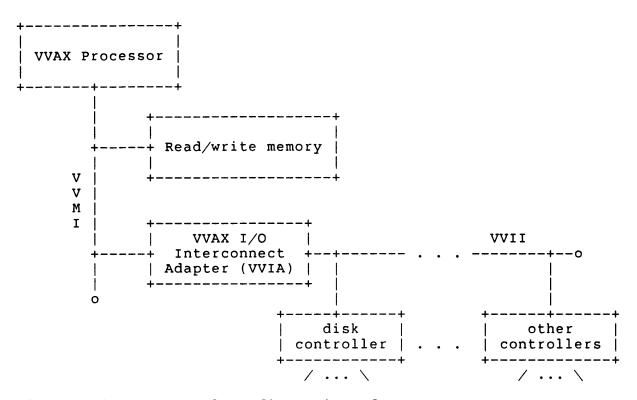

| B-1          | Conceptual Configuration of a VVAX System                                            |        |

| B-2          | MicroVAX I Physical Address Space                                                    | D 1 4  |

| B-3          | MicroVAX I System Identification Register (SID)                                      | D-14   |

| B-4          | MicroVAX I Machine-Check Stack Frame                                                 | B-16   |

| B-5          | MicroVAX II Physical Address Space                                                   | B-17   |

| B-6          |                                                                                      | B-19   |

| B-7          | MicroVAX II Machine-Check Stack Frame                                                | B-19   |

| B-8          | VAX-11/730 Physical Address Space                                                    | B-13   |

| B-9          | VAX-11/730 Physical Address Space                                                    |        |

| B-10         | VAX-11/730 System Identification Register (SID) VAX-11/730 Machine-Check Stack Frame | B-24   |

| B-10<br>B-11 | VAX-11/750 Machine-check Stack Frame                                                 |        |

| B-12         | VAX-11/750 Physical Address Space                                                    |        |

| B-13         | VAX-11/750 System Identification Register (SID) VAX-11/750 Machine-Check Stack Frame | B-28   |

| B-14         | VAX-11/780 Physical Address Space                                                    | B-29   |

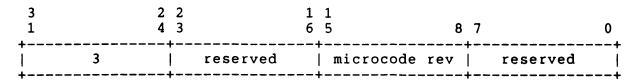

| B-15         | VAX-11/780 System Identification Register (SID)                                      | B-23   |

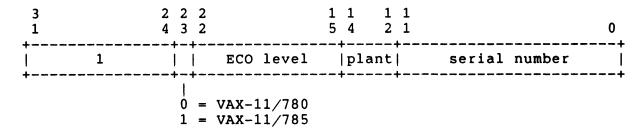

| B-16         | VAX-11/780 Machine-Check Stack Frame                                                 | B-31   |

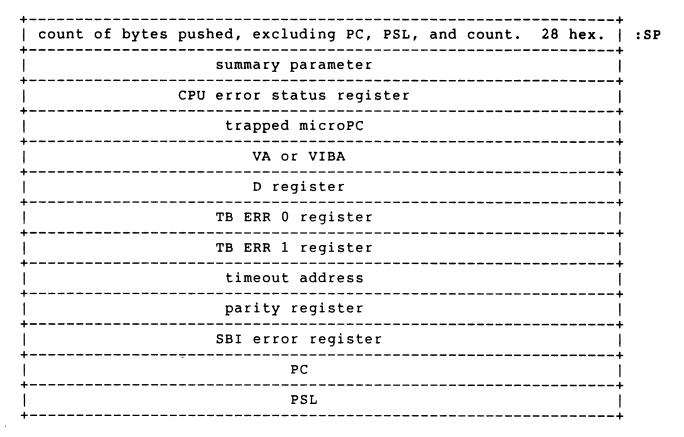

| B-17         | VAX-11/700 Machine-check Stack Frame                                                 | B-33   |

| B-18         | VAX 8200 System Identification Register (SID) .                                      |        |

| B-19         | VAX 8200 Machine-Check Stack Frame                                                   | B-35   |

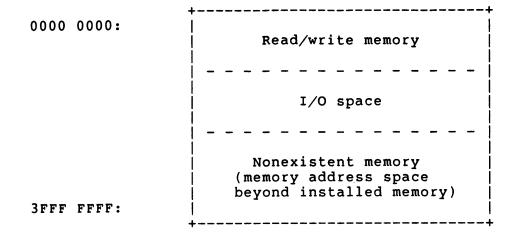

| B-20         | VAX-11/8600 Physical Address Space                                                   | B-36   |

| B-21         | VAX 8600 System Identification Register (SID) .                                      | B-37   |

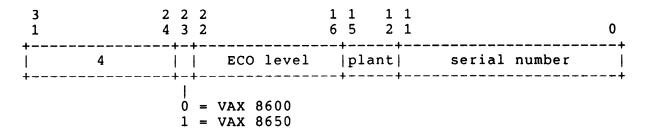

| B-21         | VAN 0000 System Identification Register (SID) .                                      | B-40   |

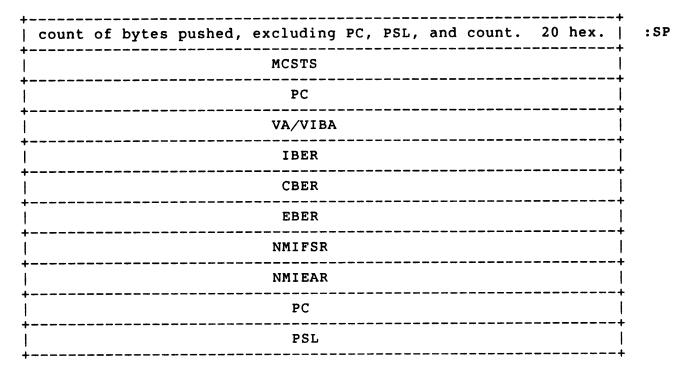

| B-23         | VAX 8600 Machine-Check Stack Frame                                                   | B-41   |

| B-23<br>B-24 | VAX-11/8800 Physical Address Space                                                   | B-43   |

| B-24<br>B-25 | VAX 8800 System Identification Register (SID) .                                      | B-45   |

|              | VAX 8800 Machine-Check Stack Frame                                                   | B-46   |

| B-26         | VVAX Physical Address Space                                                          | B-47   |

| B-27         | VVAX System Identification Register (SID)                                            | B-48   |

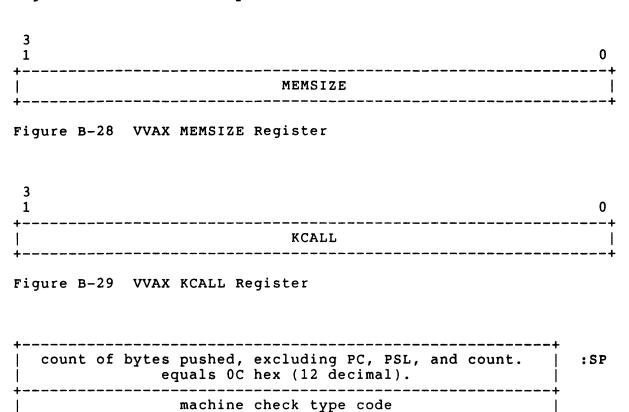

| B-28         | VVAX MEMSIZE Register                                                                | B-49   |

| B-29         | VVAA KUALL KEGISTEI                                                                  | B-49   |

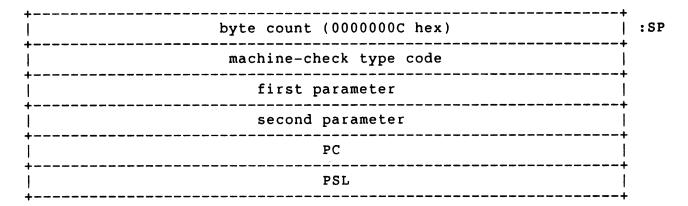

| B-30         | VVAX Machine-Check Stack Frame                                                       | B-49   |

## TABLES

| 1-2 Fields of the Processor Status Longword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1     | Sign and Digits in Decimal Strings               | 1-20  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------|-------|

| 2-1 Floating-Point Values Representable as Literals 2-2-2 Summary of General Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | Fields of the Processor Status Longword          | 1-26  |

| 2-2 Summary of General Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | Floating-Point Values Representable as Literals  | 2-11  |

| 3-2 CRC Shift Amounts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | Summary of General Register Addressing           | 2-17  |

| 3-2 CRC Shift Amounts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | Common CRC Polynomials                           | 3-180 |

| BDIT Pattern Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | CRC Shift Amounts                                | 2-100 |

| 3-4 EDIT Pattern-Operator Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | EDIT Dattern Operators                           | 3-220 |

| 4-1 Fields of the PTE (25-Bit Page Frame Number) . 4 4-2 Fields of the PTE (21-Bit Page Frame Number) . 4 4-3 PTE Protection Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | EDIT Pattern-Operator Encoding                   | 3-221 |

| 4-2 Fields of the PTE (21-Bit Page Frame Number) . 4 4-3 PTE Protection Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | Fields of the DTF (25-Bit Page Frame Number)     | 4-10  |

| 4-3 PTE Protection Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | middle of the DMF (21-Bit Page Frame Number)     | 4-11  |

| Fields of the Memory-Management-Fault Parameter An Example of Interrupt Processing Arithmetic-Exception Type Codes Compatibility-Mode Exception Type Codes State Changes During Tracing System-Control-Block Vectors Indication of Current Stack Pointer Contents of the Process Control Block Contents of the Process Control Block Contents of the Process Control Block Instruction Stream Instruction Stream Required Internal Processor Registers All Internal Processor Registers SID<31:24> and SYS_TYPE<31:24> Assignments All Internal Processor Registers SID<31:24> and SYS_TYPE<31:24> Assignments Compatibility-Mode Instructions Compatibility-Mode Trap Instructions Compatibility-Mode Trap Instructions Compatibility-Mode Trap Instructions Compatibility-Mode Reserved Instructions Compatibility-Mode Reserved Instructions Additional Effects of Power-Up Initialization Fields of the RXCS Register Contents of the RXDB Register Contents of the Virtual Machine's PSL Contents of the Exception Condition Type (ETYPE) Fields of the Exception Condition Type (ETYPE) Fields of the Exception Condition Type (ETYPE) Fields Passembler Notation for Vector Instructions Instructions Lencoding of the Exception Condition Type (ETYPE) Fields Passembler Notation for Vector Instructions Lependences for Vector Store and Scatter Instructions Lencoding Instructions Lencoding Instructions Lencoding Instructions Lencoding I |         | PRE Backetien Codes                              | 4-15  |

| An Example of Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | PTE Protection codes                             | 4-32  |

| S-2 Arithmetic-Exception Type Codes 5-3 Compatibility-Mode Exception Type Codes 5-4 State Changes During Tracing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | Fields of the memory-management-radic ratameter  | 5_8   |

| State Changes During Tracing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | An Example of Interrupt Processing               | 5_10  |

| For Indication of Current Stack Pointer Processor State Transitions Contents of the Process Control Block PTE Resources that when changed can modify the Instruction Stream PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Required Internal Processor Register PTE Required Internal Processor Register PTE Required Internal Processor Internations PTE Required Internal Processor Internation Inter |         | Arithmetic-Exception Type Codes                  | 5-10  |

| For Indication of Current Stack Pointer Processor State Transitions Contents of the Process Control Block PTE Resources that when changed can modify the Instruction Stream PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Required Internal Processor Register PTE Required Internal Processor Register PTE Required Internal Processor Internations PTE Required Internal Processor Internation Inter |         | Compatibility-Mode Exception Type Codes          | 5-10  |

| For Indication of Current Stack Pointer Processor State Transitions Contents of the Process Control Block PTE Resources that when changed can modify the Instruction Stream PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Required Internal Processor Register PTE Required Internal Processor Register PTE Required Internal Processor Internations PTE Required Internal Processor Internation Inter |         | State Changes During Tracing                     | 2-1/  |

| For Indication of Current Stack Pointer Processor State Transitions Contents of the Process Control Block PTE Resources that when changed can modify the Instruction Stream PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Types For Use By I/O Required Internal Processor Registers PTE Required Internal Processor Register PTE Required Internal Processor Register PTE Required Internal Processor Internations PTE Required Internal Processor Internation Inter | 5-5     | System-Control-Block Vectors                     | 5-25  |

| 7-7 Processor State Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | Indication of Current Stack Pointer              | 3-20  |

| Resources that when changed can modify the Instruction Stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-7     | Processor State Transitions                      | 2-30  |

| Instruction Stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1     | Contents of the Process Control Block            | . 6-4 |

| Instruction Stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-1     | Resources that when changed can modify the       |       |

| Required Internal Processor Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | Instruction Stream                               | 7-13  |

| Required Internal Processor Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-2     | PTE Types For Use BV 1/O                         | 1-21  |

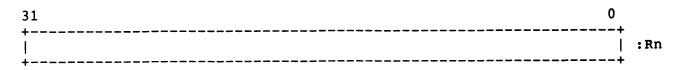

| 8-2 All Internal Processor Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | Required Internal Processor Registers            | . 8-/ |

| SID<31:24> and SYS_TYPE<31:24> Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | All Internal Processor Registers                 | . 8-9 |

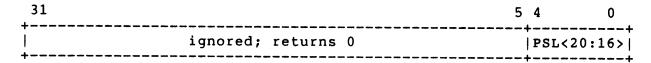

| Bit Assignments in the LICENSE_ID Subfield                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | ctb/21.24\ and GVG TVDE/31.24\ Assignments       | 8-19  |