#### Introduction

to the

### COMET Microarchitecture

Yale N. Patt

San Francisco State University San Francisco, CA 94132

and

Corporate Research Group Digital Equipment Corporation Maynard, Ma. 01754

25 March 1980

\*\* PCOMPANY CONFIDENCE AL

#### PREFACE

This report is an introduction to the microarchitecture of a particular host computer, COMET. It is not a general introduction to microprogramming; other books will have to do that. It is also not a hardware reference manual. No attempt has been made to delineate an encyclopedic taxonomy of COMET's features. Instead, topics are discussed in the order that I think they fit. My goal is that the reader should be able to make sense of COMET and its parts.

This report was written from the perspective of the microprogrammer; it describes the microarchitecture, i.e., the architecture visible to the microprogrammer. It should be useful to those who want to know how COMET implements VAX, and also to those who need to get started so they can write user microcode for COMET.

It is assumed that the reader has some understanding of computer architecture in general, and the VAX architecture in particular. Nevertheless, certain VAX features like memory management and interrupt handling are discussed first, before their COMET implementations.

The report was written because a lot of people outside of the COMET group wanted to know how COMET works. I have been able to complete it because Paul Gilbault and Charlie McDowell were willing to patiently answer a lot of questions, and because Bob Glorioso and Don Gaubatz either agreed or were willing to accept my judgment that it was something we ought to be doing.

I must also acknowledge, with thanks, the excellent critical reading of an earlier draft of this report by Fernando Colón Osorio, Charlie McDowell, and Martin Minow. Thanks are also due to Serena Shields for typing the manuscript. She has patiently endured my many changes to this report.

The report is organized in six chapters. Chapter 1 provides an overview of COMET, both from the standpoint of it being a host microprogrammable computer, and from the standpoint of its VAX emulation. The two major parts of a microprogrammable computer Chapter 2 treats the microsequencer and are covered next: Chapters 3 and 4 deal with the Data Path. Chapter 5 is specific to the VAX emulation. It describes the COMET mechanisms for implementing the VAX interrupt and exception handling and memory management functions. The report concludes with two examples of COMET microcode. One was taken directly from the VAX emulation. It is the execution flow for the INDEX instruction. The other is a new (unsupported, unasked for, and perhaps unwelcomed!) special purpose instruction for matching bit patterns. The intent was to show how to go about designing your own new instruction.

#### TABLE OF CONTENTS

| ŧ   | D | D | ø   | Ð | A | C | ø |

|-----|---|---|-----|---|---|---|---|

| 1 4 | • | к | 200 | æ | - | • | E |

- 1. INTRODUCTION

- 1.1 Overview of COMET

- 1.2 The VAX Emulation

- 1.3 User Microprogramming

- 2. THE MICROSEQUENCER

- 2.1 The Multi-way Branch

- 2.1.1 The Branching Mechanism

- 2.1.2 Sources of Signals to be ORed

- 2.2 The Microstack

- 2.2.1 The Push Mechanism

- 2.2.2 The Pop Mechanism

- 2.2.3 Subroutine Control

- 2.3 The VAX-specific ROMs

- 2.3.1 Organization of the ROMs

- 2.3.2 Processing of the BUT codes

- 2.3.3 An example

- 3. THE DATA PATH, PART I: THE ALU

- 3.1 Basic Functioning

- 3.2 The Single Bit Shift Operation

- 3.3 Special Functions The ALU Control (ALPCTL) field

- 4. THE DATA PATH, PART II: THE SUPER ROTATOR AND THE SCRATCH PAD REGISTERS

- 4.1 The Super Rotator

- 4.1.1 32 bit data output

- 4.1.2 Super Rotator Control (SRKSTA) status bits

- 4.2 The Scratch Pad Registers

- 4.2.1 Uses of the Registers

- 4.2.2 Address Control

- 4.2.3 Write Control

- 4.2.4 The Register Back Up Stack

- 4.2.5 Scratch Pad Address (SPASTA) status bits

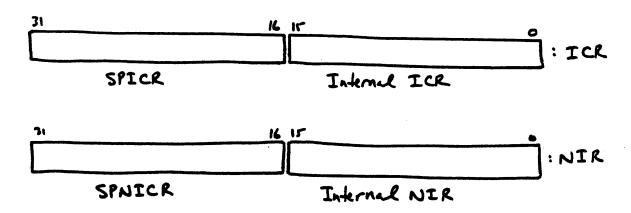

#### 5. COMET IMPLEMENTATION OF VAX'S SYSTEM ARCHITECTURE

- Interrupts and Exceptions

- 5.1.1 VAX Exceptions and Interrupts

- 5.1.2 VAX Exception and Interrupt Handling Mechanisms

- 5.1.3 COMET implementation

- 5.1.3.1 Detection and Branching 5.1.3.2 The "Initiate" Microcode

- 5.1.3.3 A Consistent Machine State

- 5.1.3.4 More Detail: Timer Service and Software Interrupts

- 5.1.3.5 Return from Exception or Interrupt (REI)

- 5.1.4 An Example

#### 5.2 Memory Management

- 5.2.1 VAX Memory Management

- 5.2.2 COMET Implementation

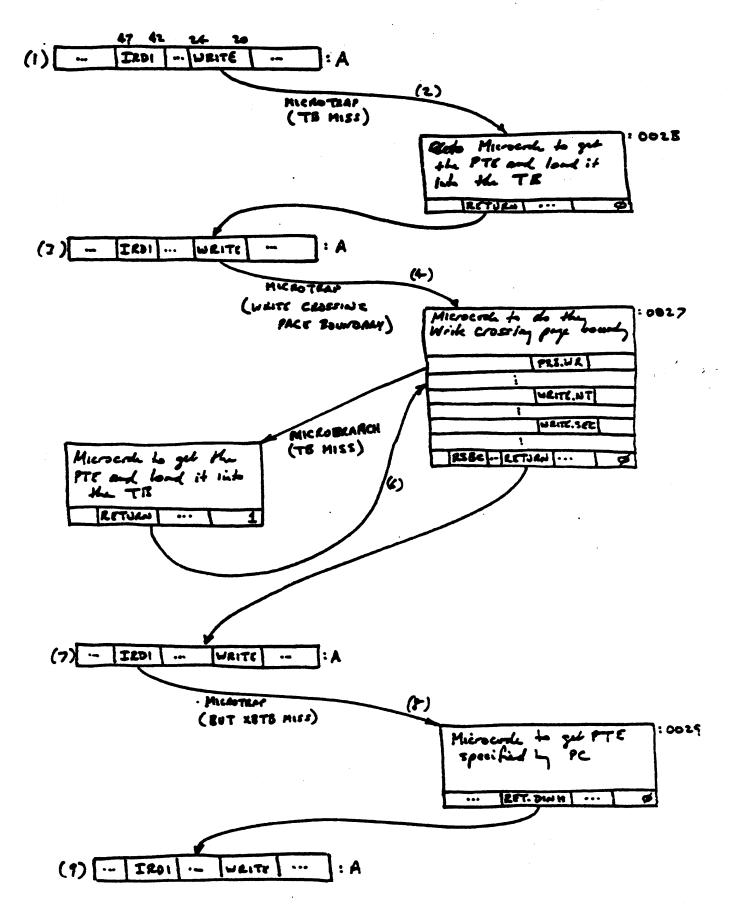

- 5.2.2.1 Memory Management Microtraps

- 5.2.2.2 Re-execution of a Faulting Microinstruction

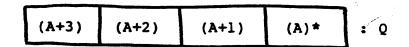

- 5.2.2.3 Unaligned memory access service routine

- 5.2.2.4 Translation Buffer (TB) miss service routines

#### 5.2.3 An Example

#### 6. MICROPROGRAMMING EXAMPLES

- 6.1 Example 1: The INDEX Instruction

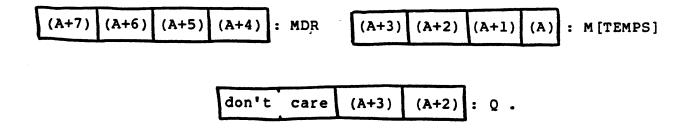

- 6.2 Example 2: A user-defined instruction

APPENDIX: A List of Acronyms and their Meanings

# CHAPTER 1. INTRODUCTION

# 1.1 Overview of COMET

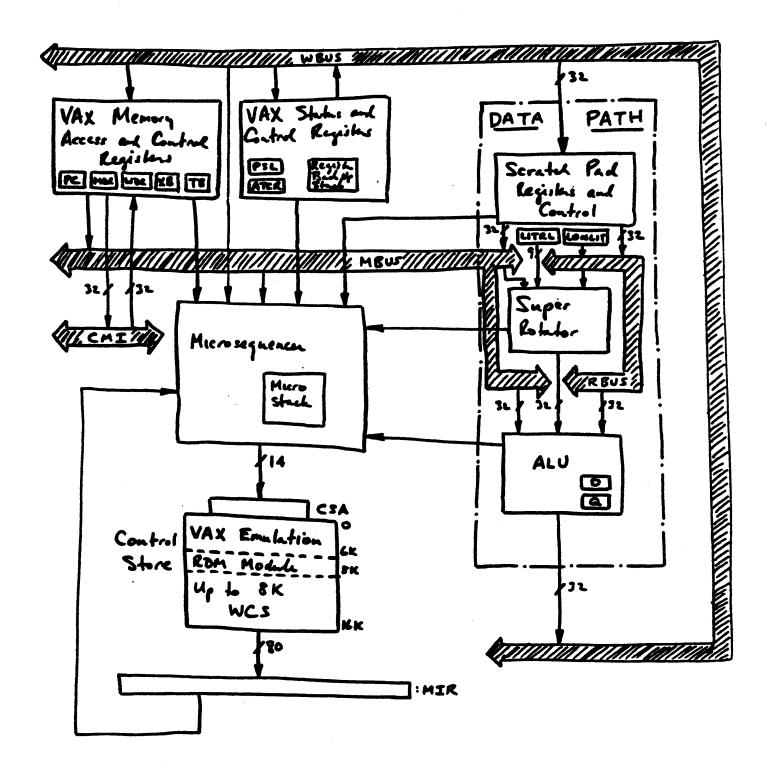

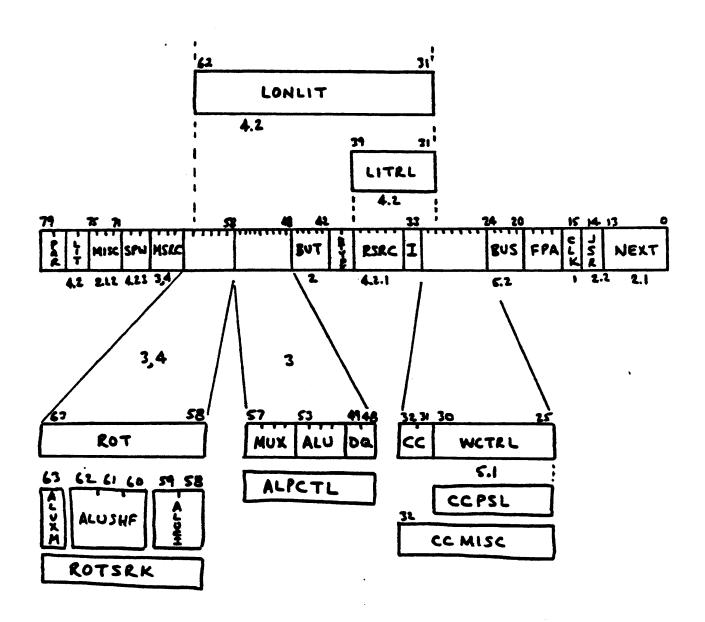

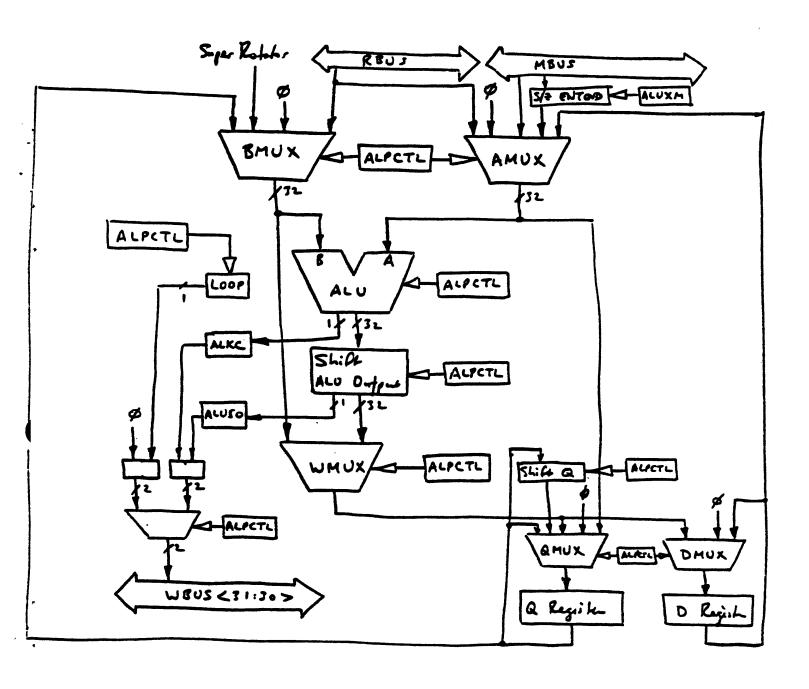

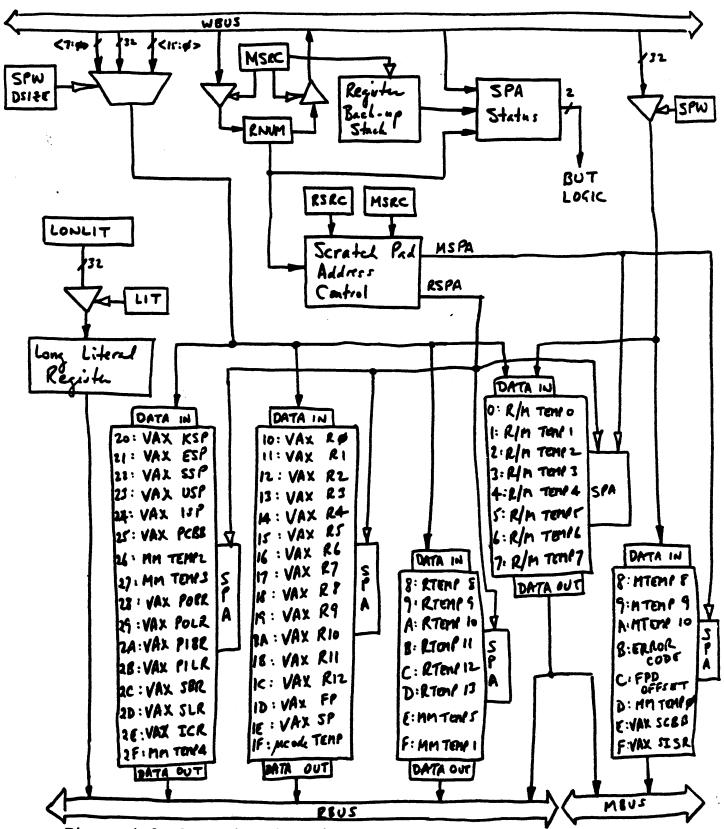

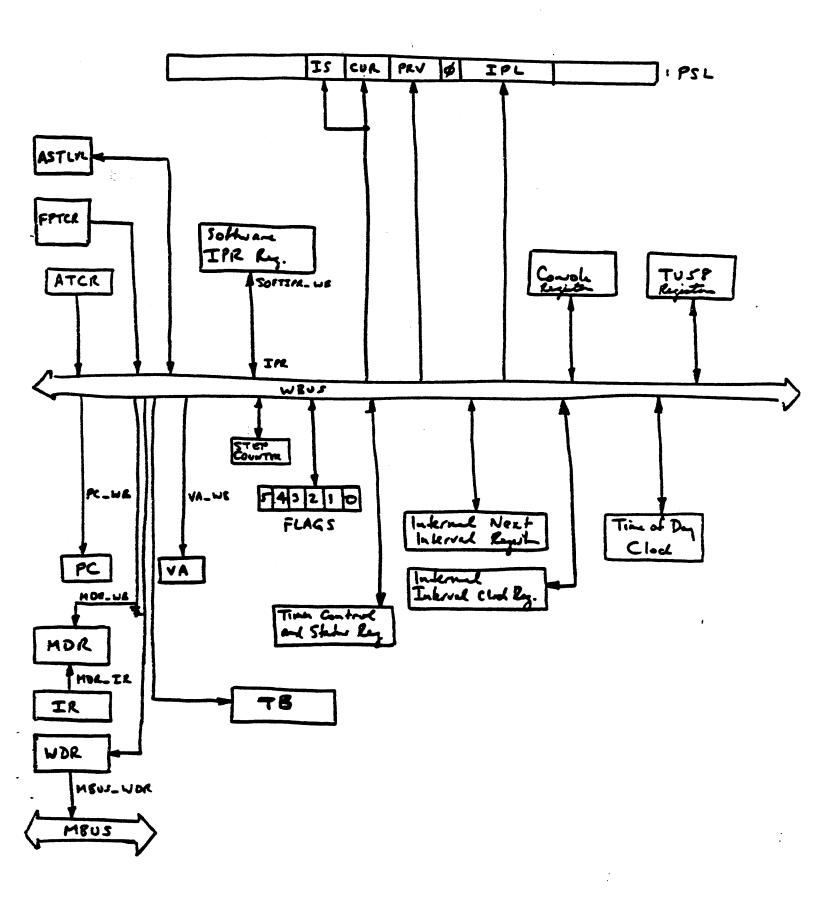

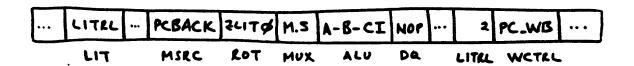

comet is a microprogrammable computer which was designed specifically to emulate the VAX-11 architecture. It consists of up to 16K words of control store, one 80 bit microinstruction per word, a microsequencer, a 32 bit Data Path, a number of registers which are needed to access COMET's main memory, and a number of status and control registers which are needed to emulate VAX. Figure 1.1 is an overall block diagram of the COMET microarchitecture. Figure 1.2 shows the fields of a COMET microinstruction. The number associated with each field is the section in this report where the use of that field is discussed in detail.

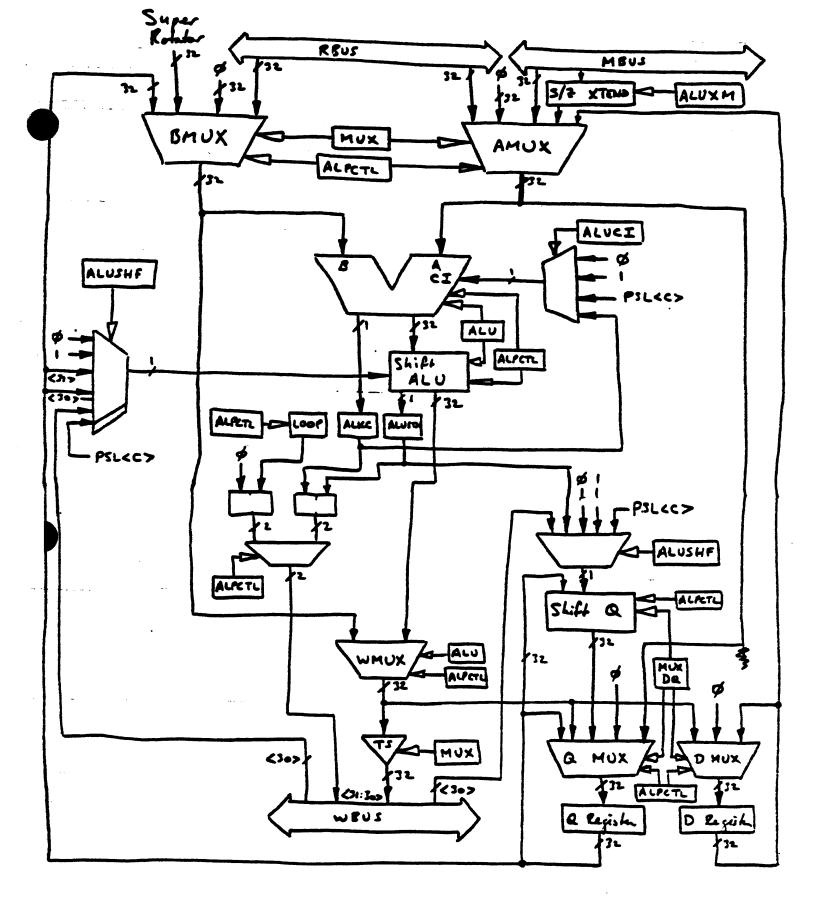

There are three major internal buses in COMET: the WBUS, the MBUS and the RBUS. The main bus is the WBUS. The output of the ALU, unless inhibited, goes on the WBUS. Data to be written into memory and data to be written into the Scratch Pad registers are taken from the WBUS. Status and control information are passed to and from their particular registers via the WBUS. The MBUS and RBUS provide sources for the Super Rotator and the ALU. Data on the MBUS is primarily taken from the VAX main memory interface registers and from the M scratch pad registers. Data on the RBUS is from the R scratch pad registers and the Long Literal Register.

The COMET Data Path consists of two sets of Scratch Pad registers, a LONLIT register, the Super Rotator, the ALU, and two special registers (D and Q). All are 32 bits wide. The ALU can perform 2's complement arithmetic, BCD arithmetic, and logical operations. There are two input ports to the ALU (A and B); both are multiplexed. The MUX field controls the sources of the ALU, the ALU field specifies the arithmetic or logical function to be performed, and the DQ field controls the destination of the ouput. The source of the carry input to the ALU is specified by the ALUCI field. Input to the ALU can come from the RBUS, the MBUS, the Super Rotator, and the D and Q registers. The output of the ALU can be shifted or rotated (by itself, or combined with the Q register); the type of shift is determined by the DQ and ALUSHF fields. The output of the ALU can go on the WBUS and it can go to the D or Q register. In addition, the ALU can perform certain special functions (for example, a FAST MULTIPLY) where the input and output are specified as part of the function. This

<sup>\*</sup>The Appendix contains a list of the acronyms used in this report, often with additional commentary.

is done by coding the MUX, ALU and DQ fields as a single unit. We call this the ALPCTL field.

There are 56 Scratch Pad registers. Eight have two ports (to the MBUS and the RBUS), eight can be accessed by the MBUS only, and 40 can be accessed by the RBUS only. The particular registers accessed during any microcycle are specified by the MSRC and RSRC fields. Writing to the Scratch Pad registers is controlled by the SPW field.

Figure 1.1 COMET Microarchitecture (Overview)

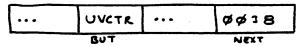

Figure 1.2 The COMET Microinstruction

The Super Rotator is a powerful combinational logic circuit. It can barrel shift a 64-bit data element, it can extract a desired field from a given piece of data, and it can construct a 32-bit data element according to a variety of specifications. This provides COMET with a very efficient bit manipulation capability. The Super Rotator is controlled by the ROT field.

Immediate data of 9 or 32 bits can be entered into the Data Path from the instruction stream under the control of the LIT field. The LIT/LONLIT\* micro-order causes the LONLIT register to be loaded with Bits<62:31> of the microinstruction. This data is then available in the next microinstruction; access to it is controlled by RSRC. The LIT/LITRL micro-order causes Bits<39:31> of the microinstruction to be made available as input to the Super Rotator during the same microcycle.

The basic microcycle of the COMET architecture is 320 nsec. This is sufficient to read from the Scratch Pad registers, pass through the Super Rotator, perform an ALU operation, and write back to a Scratch Pad register. Certain activities can cause a microinstruction to need more than 320 nsec. For example, suppose the address of the next microinstruction is to be computed partly from the resuts of the ALU operation. We will see that the microrder BUT/WX.EQ.O produces such a situation. When this happens, the CLK field can extend the microcycle to 480 nsec.

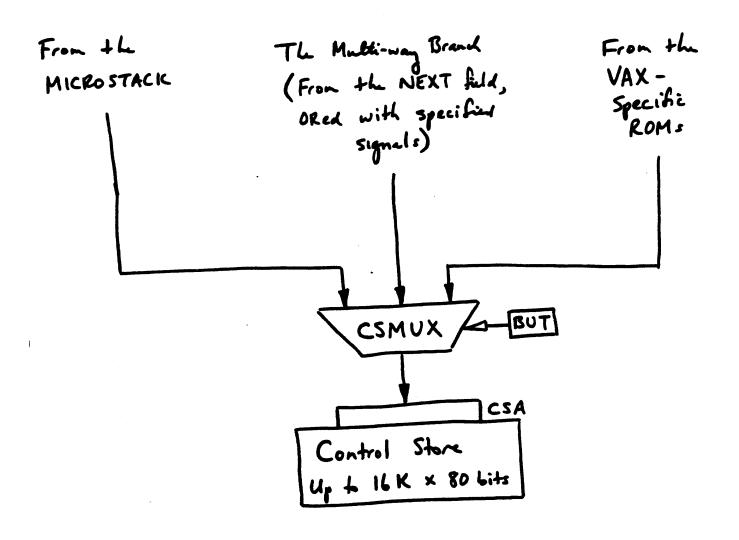

COMET has no microprogram counter. The address of the next microinstruction (CSA) is usually determined by the microsequencer in one of several ways. The microsequencer can generate a microbranch (up to 64-way conditional branch) based on the values of certain internal signals specified by the BUT field. The branch addresses are based on the contents of the NEXT field and the values of these specified signals. Or the CSA can be obtained by popping the microstack. Or the address can be obtained from the IRD1 or IRDX ROMs. The above schemes are all under the control of the BUT field. In addition, the COMET hardware can override these addressing schemes by forcing the CSA (by means of a microtrap) to a fixed address. This last technique is used for memory management and to initiate some of the VAX exceptions and interrupts.

Control store addressing supports up to 16K of control store. Actually, current hardware implementation contain only 9K of control store. The low order 6K is required to emulate VAX and the next 2K is dedicated to the Remote Diagnostic module (RDM). This leaves a possible 8K address space for WCS, of which 1K is actually implemented.

<sup>\*</sup> The notation <field>/<code> is used extensively throughout this report. LIT/LONLIT represents the micro-order in which the LIT field contains the LONLIT code.

Finally, COMET contains a number of features which are specifically included to aid in the emulation of VAX. MDR, WDR, Translation Buffer, and Execution Buffer are a few of the registers which are used to control access through the CMI, a 32 bit wide synchronous bus, to the cache and VAX main memory. The BUS field controls this access. The PSL, Software IPR, Status Flags, Console and TU58 registers, ASTLVL register, and the internal next interval register are a few of status and control registers which are used to control interrupt and exception processing. The WCTRL field controls these functions.

### 1.2 The VAX Emulation.

The purpose of this section is to provide an overview of how COMET emulates VAX. The details of each mechanism are covered more thoroughly in later chapters of this report.

The VAX registers are, for the most part, implemented in the M and R Scratch Pads. In particular, R0 through R12, FP, and SP are implemented by R[10] through R[1E] in the R Scratch Pad. stack pointers are R[20] through R[24], the memory management registers are R[28] through R[2D], the high order 16 bits of ICR and NICR is R[2E], the PCBB is R[25], and the SCBB and SISR are M[0E] and M[0F]. The rest of the VAX registers, including PC, PSL, and ASTLVL are implemented by COMET registers designed specifically for that purpose.

Emulation starts with the BUT/IRD1 micro-order. This is the signal to begin the emulation of the next VAX machine In the microcode which emulates each VAX instruction. instruction, this micro-order is present in the microinstruction.

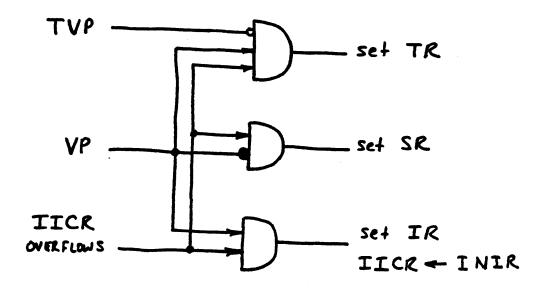

BUT/IRD1 causes two things to occur. It invokes a hardware routine DOSERVICE which checks for traps and interrupts. If any are pending, the processor will microtrap to the appropriate control store address to initiate the trap or interrupt. it causes two bytes to be fetched from the instruction stream (i.e., from the XB) and loaded into the IR and OSR. (The opcode of the next VAX instruction is loaded into the IR; the first operand specifier is loaded into the OSR). The XB (execution buffer) is an eight byte register. The instruction stream is prefetched automatically four bytes at a time and stored in the Each time the XB is accessed, the PC is automatically incremented.

The processor then begins the emulation of the VAX instruction. Usually it branches to common code to evaluate the address of the first operand. The branch address is obtained from a ROM (the IRD1 ROM) which is indexed by the opcode of the VAX instruction, by whether the current VAX instruction - 1-6 -

previously suspended (i.e., if the FPD bit is set), and by whether Floating Point Accelerator hardware is present. The common code terminates with a BUT/IRDX micro-order which causes the next control store address to be obtained from the IRDX ROM. The rest of the operand addresses are computed and the VAX instruction is emulated, terminating in a BUT/IRD1 micro-order, which starts the cycle again.

If the VAX instruction requires a memory access, a BUS read or write initiates the access. COMET maintains a TB (translation buffer) of PTE's, which are needed to map virtual addresses into physical addresses. If the PTE is not present in the TB or if the memory access is unaligned (VAX allows the user to disregard natural word and longword boundaries), COMET microtraps (forces the control store address) to a specific location to correct the problem. The executing microinstruction is not allowed to complete until the problem is corrected. If the problem is corrected, control returns to that microinstruction.

If the emulation of a VAX instruction requires a sufficiently long time that pending interrupts cannot be ignored, the VAX emulation tests for interrupts under microprogram control. If an interrupt is to be initiated, the processor is put into a consistent state by either undoing whatever processing has occurred, or if that is not possible, by setting FPD and following a prescribed procedure for "packing up" the relevant machine state so that the VAX instruction can be restarted at the point where it was suspended.

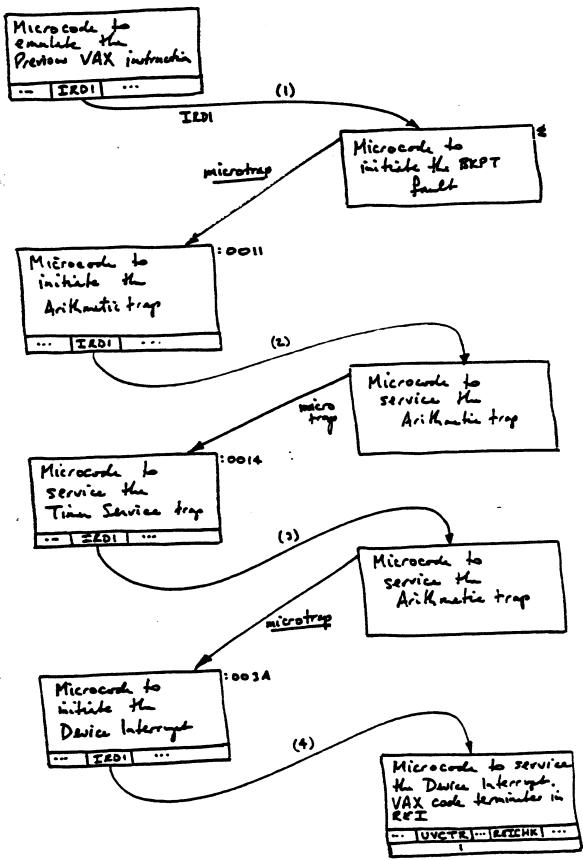

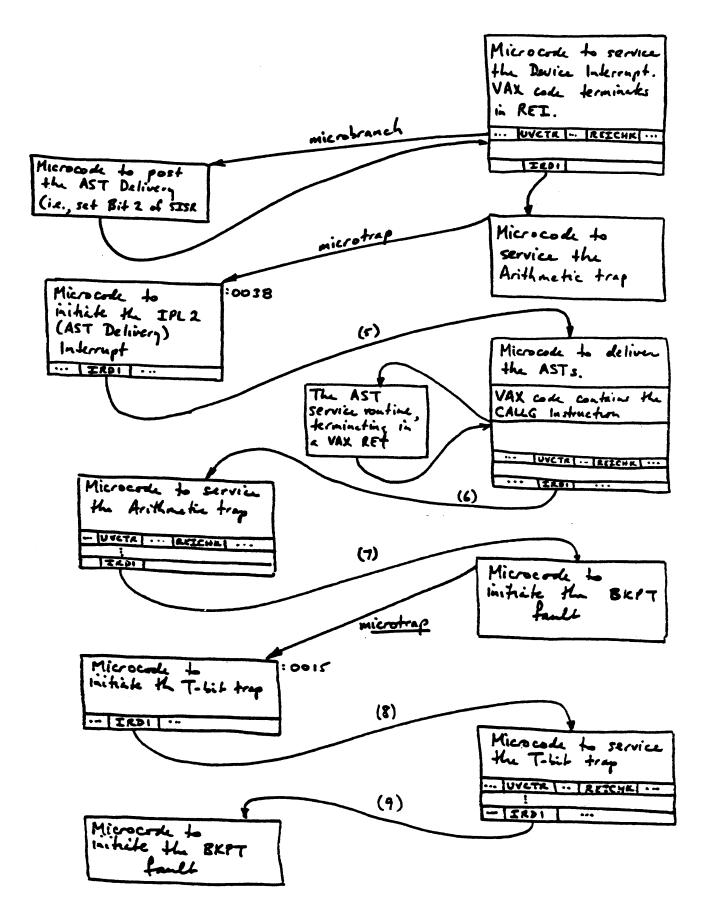

The initiation of exceptions and interrupts are emulated in microcode. The branch to the starting address is caused by either a microtrap in case the condition was detected by the hardware (for example, by DOSERVICE), or by a microbranch in case the condition was detected under microprogram control. In either case the microcode selects the appropriate stack to service the exception or interrupt, pushes the current PC and PSL as well as any necessary parameters on that stack, puts the processor into a consistent machine state, constructs a PSL for the service routine, performs any special tasks peculiar to that exception or interrupt, and loads PC with the starting VAX address of the service routine. The microcode terminates in BUT/IRD1, the signal to fetch the next VAX instruction, which is usually the first instruction in the VAX service routine.

# 1.3 User Microprogramming

There are three general uses for microprogramming: emulation of a target machine, instruction set enhancement, and fine tuning. By instruction set enhancement, we mean addding new machine language instructions to the machine instruction set. By fine tuning, we mean adding a routine in microcode in order to carry out a set of tasks (for example, an operating system subroutine) more efficiently than can be done in machine

language.

A number of COMET features do support writing your own microcode to augment the VAX instruction set or to fine tune some piece of software. These features are discussed below. not intended that COMET be used to emulate other target machines.

To support general microprogramming, the Data Path includes the following features: 18 general purpose 32 bit scratch pad registers, 8 of which have ports to both the RBUS and the MBUS; the Super Rotator, which allows very efficient (in hardware) bit picking operations; and a flexible ALU. As is the case with many microprogrammable computers, inputs to the ALU are multiplexed, the output of the ALU can be shifted or rotated (alone or in combination with the Q register), and the output can be applied to several alternative destinations.

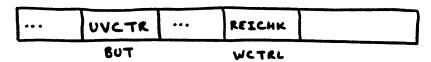

The microsequencer supports general microprogramming in three important ways: conditional branching loop control and subroutine control. COMET has six independent flag bits (FLAGO through FLAG5) which can be set or cleared under microprogram control (e.g., MISC/SET.FLAG0), then later used for conditional branching (e.g. BUT/FLAG0). COMET also has a five-bit step counter which can be initialized to any arbitrary value (0  $\leq$  n  $\leq$ 31) by the microrder WCTRL/STEPC\_WB. If this is followed by a loop which terminates with BUT/DBZ.SC, the loop will be performed n times. Each iteration will conclude with a "decrement the step counter and branch on zero. In the case of subroutine control, a 16-deep microstack is available for nested subroutine calls. The JSR/PUSH micro-order pushes the CSA (control store address) onto the microstack; the BUT/RETURN micro-order pops it. Chapter 2 discusses the functionality of the microsequencer in greater detail.

COMET provides two independent paths to memory, one for data (read/write) and one for instructions (read only). In the case of data, the VA is used as the storage address register, and the MDR (read) and WDR (write) are used as storage data registers. In the case of instruction, PC points to memory and the XB can be used as a storage data register. Both are available to the user microprogrammer, and in fact were used in the VAX firmware where two distinct Data Paths to memory were needed (cf. Section 5.2).

Finally, the COMET microinstruction (80 bits) provides a fair amount of parallelism. In a single microinstruction, one can introduce an immediate operand, perform an ALU function, push a control store address on the microstack, set or clear a flag bit, initiate a read or write to memory, and perform a multi-way conditional branch.

Access to WCS is via the opcode FC in the VAX instruction stream. As is described in Section 2.3 (branch on opcode) and 5.1 (initiate exceptions and interrupts), this causes an "opcode reserved to customers" fault. If WCS is present and if the

System Control Block vector specifies that the exception should be handled in WCS (i.e., SCB [14]<1:0> = 10 (binary), then a branch to a location in writeable control store occurs. From this point on, user microcode has control of the micromachine. The instruction stream (via XB) can be used as appropriate; the VAX firmware is also available.

Control can be returned to the VAX emulation by means of the BUT/IRDl micro-order. We should note that when an exception or interrupt is to be handled in WCS, the PC and PSL of the suspended process are not pushed on the stack (c.f. Section 5.1). Therefore, before BUT/IRDl is invoked, the PC must be set to the memory location of the VAX machine language program where you want the firmware to take over. The micro-order WCTRL/PC WB (load the PC with the contents of the WBUS) can accomplish this.

#### CHAPTER 2. THE MICROSEQUENCER

The COMET microarchitecture contains no microprogram counter. Unless the hardware overrides the microprogram the address of the next microinstruction (i.e., the control store address-CSA) is obtained in one of three ways:

- from the NEXT field of the current microinstruction, ORed with particular signals specified by the BUT field. (this is the multi-way conditional branch mechanism).

- 2. from the microstack.

- from the VAX-specific ROMs.

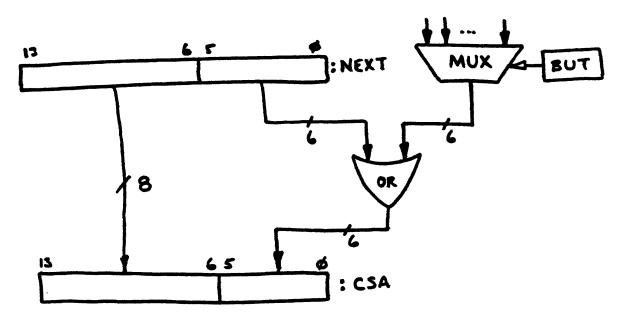

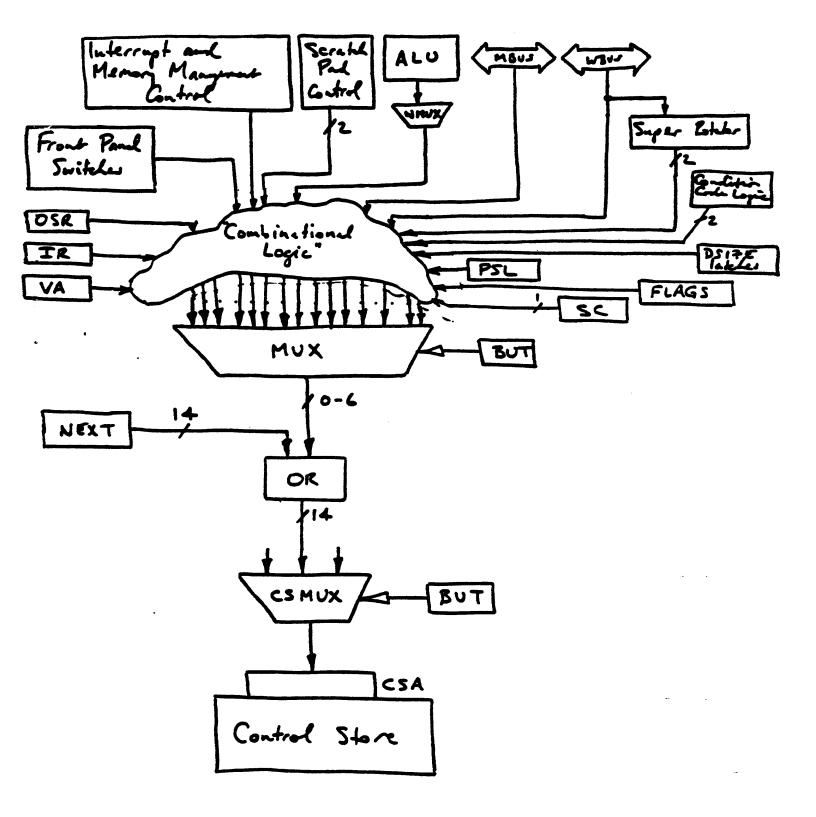

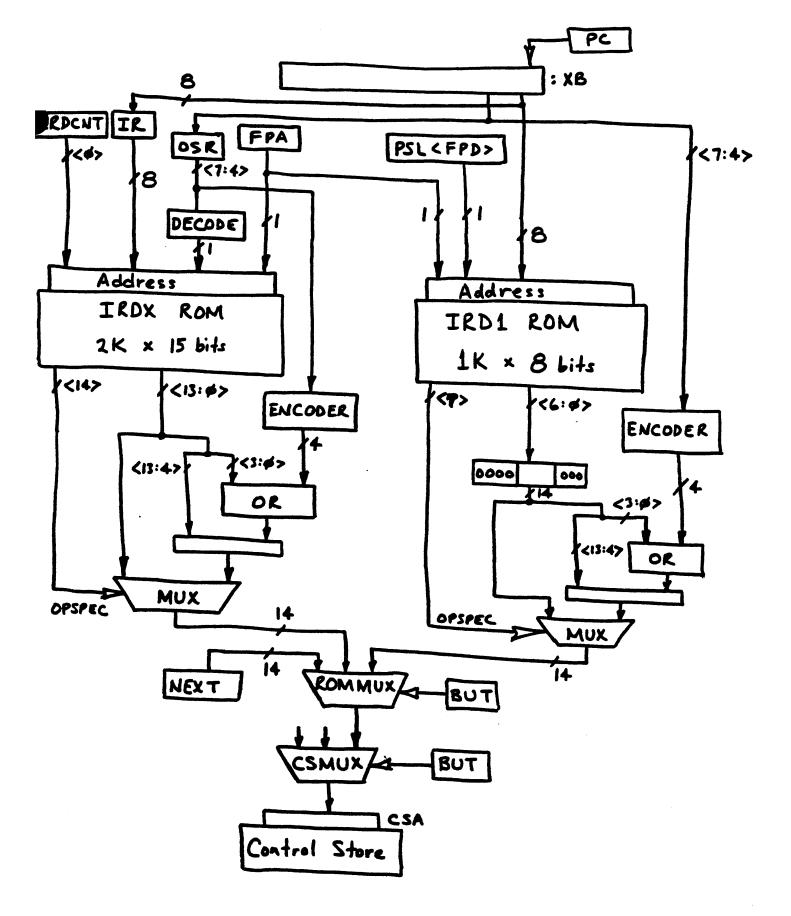

All are under the control of the Branch-U-test (BUT) field. Figure 2.1 is an overview of the microsequencer operation.\*

# 2.1 The Multi-way branch

For all but eight of the BUT codes, the CSA is obtained by performing the logical-OR of the NEXT field of the current microinstruction with the particular set of bits specified by the BUT field. Section 2.1.1 describes the branching mechanism. Section 2.1.2 delineates the sources of the signals to be ORed.

We should point out that in the figures of this chapter, CSA is illustrated as a separate register. In the actual hardware, the CSA is really obtained from the microstack; i.e., from USTK[USTKP]. See Section 2.2.

### 2.1.1 The Branching Mechanism

The general mechanism for forming the multi-way branch is illustrated in figure 2.2.

Figure 2.2

Bits <13:6> of the CSA are loaded directly from bits <13:6> of the NEXT field of the current microinstruction. The source of bits <5:0> of the CSA is determined by the particular BUT micro-order. For each of these 6 bits, if the BUT micro-order specifies a signal, then that bit of the CSA is the logical-OR of the signal specified and the corresponding bit of the NEXT field. If the BUT micro-order does not specify a signal, then that bit of the CSA is the logical-OR of "0" and the corresponding bit of the NEXT field. Table 2.1 is a complete description of this specification. As can be seen from figure 2.3, the signals to be ORed with bits from the NEXT field can come from a variety of sources. Some of the sources, such as the VA register, DSIZE latches, PSL, IR, and OSR are specific to the VAX emulation. Other sources, such as the WBUS, MBUS, and FLAG bits are more general microarchitecture structures.

Example 2.1 BUT/FLAG2T00 specifies that three bits are to be ORed as follows:

NEXT<2> is ORed with FLAG2 NEXT<1> is ORed with FLAG1 NEXT<0> is ORed with FLAG0

Figure 2.1 The Microsequencer (Overview)

Thus, if the current microinstruction had the following value:

| 71  | 47 42       |     | 13 #           |

|-----|-------------|-----|----------------|

| ••• | FLAG 2 TO & | ••• | ΙΙΦΦΙΙΦΦΙΙΦΦΦΦ |

the CSA for the next microinstruction would be

where x is the value of FLAG2, y is the value of FLAG1, and z is the value of FLAG0. In other words, an 8-way conditional branch has been produced.

In the example above, an 8-way branch was produced. If, however, NEXT <0> had been set to 1, then the effect of FLAG 0 would have been lost. The CSA of the next microinstruction would have been

resulting in a 4-way branch. In general, it is possible to produce a 0-,2-,4-,8-,16-,32-, or 64-way conditional branch, depending on the particular BUT code and the state of the six low-order bits of the NEXT field. The actual no. of possible branches is 2°, where k is the number of "relevant" bits in the NEXT field which are cleared. A bit is relevant if it is designated for ORing by the BUT code. In the above example, if the current microinstruction had the value

| 71  | 47        | 42 | 13                     | ø |

|-----|-----------|----|------------------------|---|

| ••• | FLAG 2 TO | ø  | ।।वर्ष ।।वर्ष ।।व् ।।। |   |

the CSA of the next microinstruction would have been

ιιφφιιφφιιφιιι

Hence, a 0-way (unconditional) branch would have resulted.

Example 2.2 BUT/NOP specifies that 0 bits are to be ORed. The CSA of the next microinstruction is identical to the NEXT field of the current microinstruction. An unconditional branch is the result.

Figure 2.3 shows the flow of control for setting the CSA by the multi-way branch mechanism.

# 2.1.1 Sources of Signals to be ORed.

The microsequencer provides conditional branch capability based on a wide variety of relevant conditions microarchitecture. This is accomplished by the choices of signals to be ORed which are available to the BUT field. For example, the BUT/FPS1, BUT/FPS2, and BUT/FPS3 cause conditional branching based on settings of the front panel switches. BUT/SPASTA micro-order causes conditional branching based on signals relating to the Scratch Pad registers (RNUM and Register Back Up Stack). Several micro-orders (e.g., BUT/WBUS1to0, BUT/WBUS31to30, and BUT/SRKSTA) provide branching based on signals on the WBUS. Most of them use the WBUS signals directly. However, the BUT/SRKSTA micro-order uses the combinational logic capacity of the Super Rotator to reduce WBUS <7:0> to one of four conditions, and provides those four conditions as SRKSTA <1:0> to the microsequencer. The BUT/UVCTR micro-order provides microbranch capability needed by the exception and interrupt handling and the memory management microcode.

In addition, COMET contains two sources which can be considered part of the microsequencer: the 5 bit step counter and the six independent flag flip-flops. The step counter can be set to any value from 0 to 31 (WCTRL/STEPC WB) and then used to control the number of iterations through a loop. BUT/DBZ.SC decrements the step counter and then performs a conditional branch based on whether or not the step counter equals 0. The six flag flip-flops can be set and cleared independently by micro-orders in the MISC field, then later used to perform conditional branching based on their state. For example, BUT/FLAGO permits conditional branching based on the state of FLAGO. BUT/FLAG2TOO permits an 8-way branch based on the states of FLAGO, FLAGI, and FLAGO.

Figure 2.3 Microsequencer (The Multi-way Branch)

# 2.2 The Microstack

The microstack can be used to obtain the CSA of the next microinstruction. In particular, an address can be pushed onto the microstack (by means of JSR/PUSH) and later popped (by means of BUT/RETURN or BUT/RET.DINH). The push and pop mechanisms, and their usefulness in subroutine control, will be explained shortly.

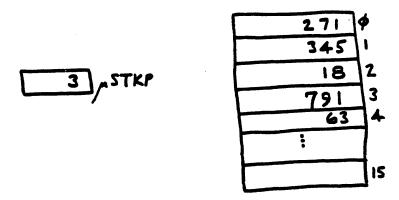

The microstack is capable of storing 16 CSAs, each of length 14 bits. A microstack pointer USTKP always points to the first available word in the microstack. It is updated automatically as a consequence of the push and pop operations. Figure 2.4 shows the microstack with addresses 271, 345, and 18 stored in words 0,1, and 2, respectively. Word 3 is available for storing a CSA.

Figure 2.4. The microstack with valid entries in words 0,1,& 2.

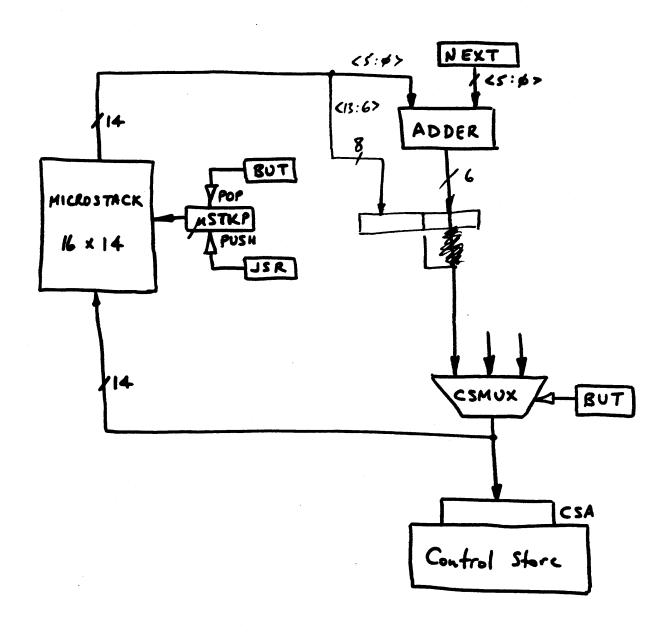

Figure 2.5 shows the flow of control for pushing addresses onto the microstack and for popping them for use in obtaining the CSA of the next microinstruction.

### 2.2.1 The Push Mechanism

During the execution of every microinstruction, the following events occur relative to the microstack:

- (1) During the first part of the microcycle, the JSR bit is examined. If it is set (i.e., JSR/PUSH), the microstack pointer is incremented.

- (2) During the second part of the microcycle, the output of the CSMUX (i.e., the address of the next microinstruction) is stored on the microstack, in USTK[USTKP]. In COMET, USTK[USTKP] is the control store address register.

Figure 2.5 The Microsequencer (from the Microstack)

Therefore, for purposes of clarity in this report, we refer to USTK [USTKP] as the CSA register whenever we are discussing its function as the register containing the address of the next microinstruction. Thus, in figure 2.5, CSA is shown as a separate entity, although in reality, it is USTK [USTKP].

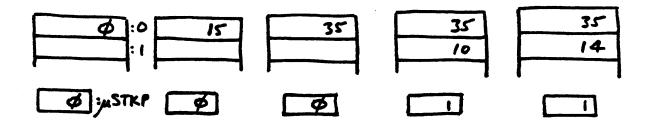

Note that loading the CSA register (i.e., storing the address of the next microinstruction is USTK[USTKP]) does not alter the microstack pointer. Thus, loading the CSA register does not push this address onto the microstack. In other words, although the address is "physically" stored in the microstack, it is stored just above the top of the microstack; i.e., the location in which it is stored is still "logically" part of available space. The following example should make this clear.

Example 2.3 Consider the sequencing of the following microcode:

| 79 | 47 AL | . 14 13 | <b>ø</b> |

|----|-------|---------|----------|

|    | NOP   | ø       | 15 : φ   |

|    | NOP   | Ø       | 35 :15   |

|    | NOP   | 1       | 10 :35   |

|    | NOP   | ø       | 14:10    |

The microstack behaves as follows:

Before 0 Before 15 Before 35 Before 10 After 10 is fetched is fetched is fetched is fetched is executed

Note that before 15 is fetched, the CSA 15 is physically stored in word 0 on the microstack. However, since the microstack pointer is 0, the microstack is still "logically" empty. Note, further, that the JSR bit is set (i.e., JSR/PUSH) in the microinstruction at CSA 35. This calls for pushing CSA 35 onto the microstack. The CSA 35 is stored on the microstack during the execution of the microinstruction at 15. However, the microstack remains empty until the first part of the microcycle

in which the microinstruction at CSA 35 is executed. Since the JSR bit is set, the microstack pointer is incremented, thereby completing the operation of pushing CSA 35 onto the stack. In the second half of that same microcycle, CSA 10 is stored in word 1 of the microstack. But the microstack pointer is not altered. Thus, at the end of execution of that microinstruction (i.e., before 10 is fetched), the microstack pointer contains the value 1, signifying that word 1 is the first available space and that word 0 contains a stacked CSA.

One final remark should be made with respect to the push mechanism. Since every CSA is stored on the stack, indeed that store operation is, in fact, the loading of the CSA register, no additional time is required for pushing an address on the microstack. That is, the machine does not wait until the JSR/PUSH code is detected before stacking the CSA of the current microinstruction. Thus, the push operation does not slow down the processing.

## 2.2.2 The Pop Mechanism

The top of the microstack is popped and used to obtain the CSA of the next microinstruction by the following sequence of operations:

- (1) USTKP  $\leftarrow$  STKP 1.

- (2) CSA<13:6> <-- USTK [USTKP] <13:6> CSA<5:0> <-- USTK [USTKP] <5:0> + NEXT<5:0>

This sequence is caused by BUT/RETURN or BUT/RET.DINH.

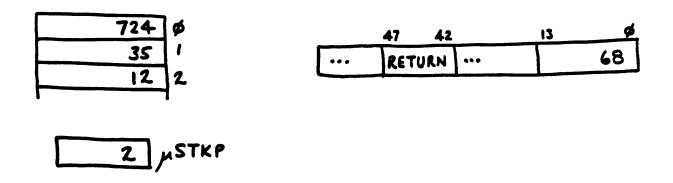

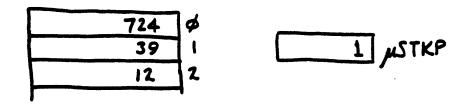

Example 2.4 Consider the following current microinstruction and contents of the microstack (all numbers in this example are decimal representations):

After execution, the CSA of the next microinstruction will be 39. The microstack will be as shown:

Only the address stored in word 0 is "logically" on the stack.

# 2.2.3 Subroutine Control.

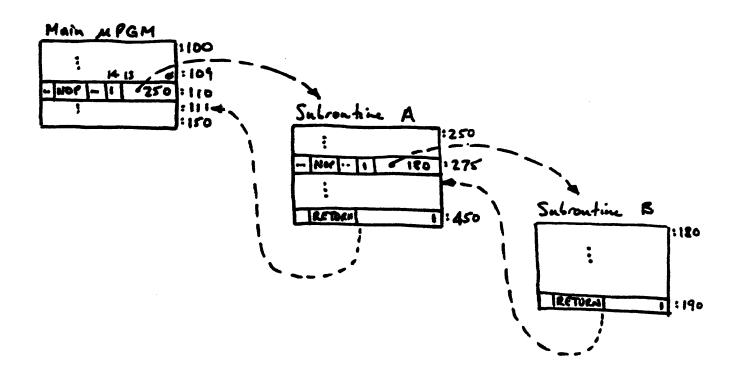

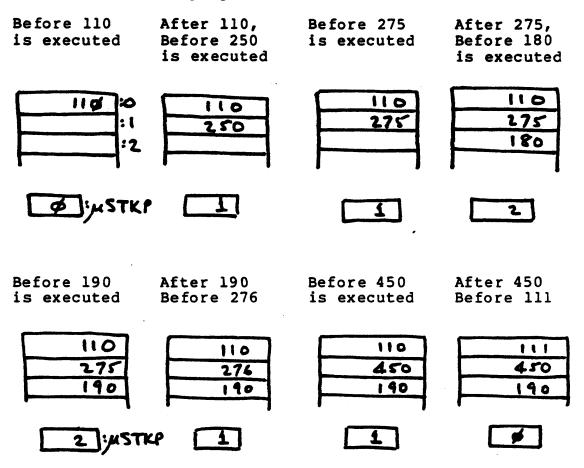

We conclude this section with an example of several nested subroutines, and a demonstration of how the flow of control is handled using the microstack.

Example 2.5 Consider a main microprogram which at CSA 110 invokes subroutine A, which in turn at CSA 275 invokes subroutine B. Assume each microprogram has its microinstructions executing in sequential order. A pictorial representation is shown below:

The contents of the microstack at critical places in the execution of the microprogram are shown below:

# 2.3 The VAX-Specific ROMs

In the emulation of a VAX machine instruction, two places in the microprogram flow of control stand out:

- (1) the initiation of the microsequence to emulate the next machine instruction, and

- (2) the initiation of the microsequence to evaluate the next operand for the current machine instruction.

Recall that a VAX instruction has variable length (each opcode can have from 0 to 6 operands), and further that the access type and data type of each operand can differ depending on whether it is the first, second, third, etc. operand of that opcode. For these two reasons, the flow of control to initiate the emulation of each machine instruction and the flow of control to evaluate each operand must be specified individually for each opcode and for each operand. The COMET microarchitecture provides three ROMS (IRD1, IRDX, and DSIZE) to assist in this specification.

Figure 2.6 shows the use of the ROMs to obtain the CSA of the next microinstruction.

Six BUT codes use the ROMs for obtaining the CSA of the next microinstruction. The BUT/IRD1 code, present in the last microinstruction of the microprogram which is emulating the current machine instruction, is the signal to begin the emulation of the next machine instruction. It uses the IRD1 ROM to obtain the starting address of the microcode to do this job. The BUT/IRDX code, present in the last microinstruction of the microprogram which is evaluating the current operand, is the signal to begin the evaluation of the next operand. It uses the IRDX ROM or the microstack to obtain the starting address of the microcode to do that job. The purpose of the four other BUT codes (BUT/IRD1TST, BUT/BRA.ON.ADD, BUT/LOD.INC.BRA., and BUT/LOD.BRA) will be explained after we describe the ROMs.

# 2.3.1 Organization of the ROMs

### THE IRD1 ROM.

The IRD1 ROM is used to compute the starting address of the microcode which is to emulate the next VAX instruction. It consists of 1K words, each containing 8 bits. Thus, 10 bits are required to address this ROM; that is, to determine the starting address of the particular emulation microcode to be executed next. They are:

- (1) The opcode of the VAX instruction (8 bits),

- (2) Whether or not the FPD bit is set, and

- (3) Whether or not the Floating Point Accelerator hardware is present.

The eight opcode bits are obtained directly from the XB, rather than from the IR. The BUT/IRD1 code initiates the loading of the IR from the XB. However, to wait for the IR to be loaded before obtaining the IRD1 ROM address would be to unnecessarily slow down the processing.

We need to distinguish the case when FPD is set from the case where it is cleared because the emulation proceeds differently for the two cases. If FPD is set, this means that the VAX instruction was suspended in order to service an exception or higher priority process. When that happened, the state of the machine was saved (we say, "packed"). Before the instruction can resume execution, it must be "unpacked." Ergo, two different branch addresses out of the IRD1 ROM. Section 5.1 discusses this in greater detail.

Figure 2.6 The Microsequencer (from the ROMs)

Also, we need to distinguish between the case where the FPA hardware is present and the case where it is not, since the difference in hardware will result in different microcode to emulate the instruction.

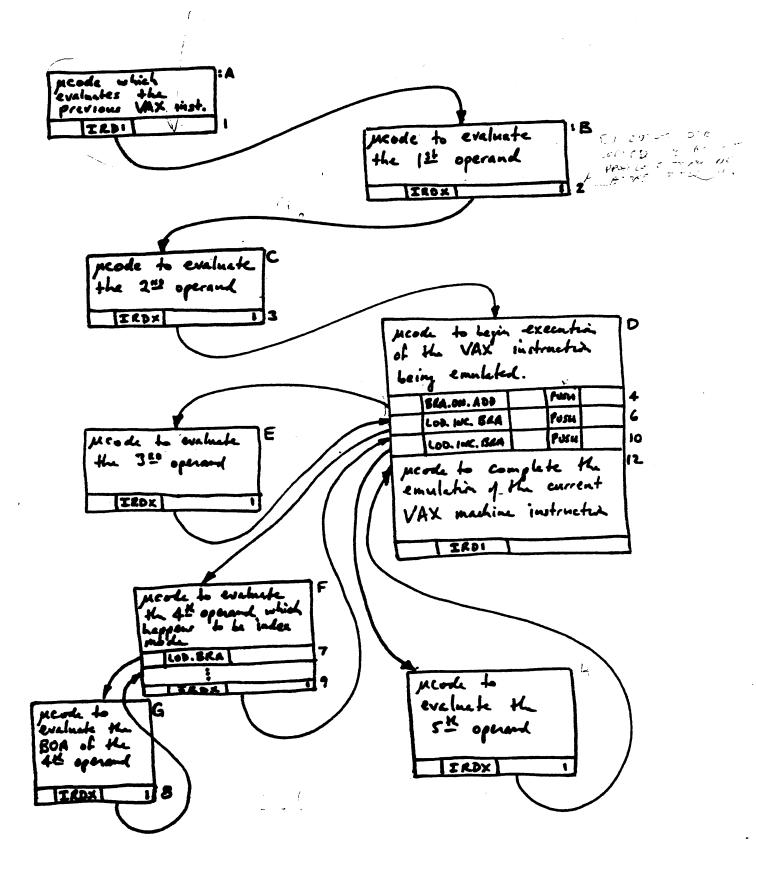

As we said, eight bits of information are stored at each IRD1 ROM address. The seven low order bits form a 14 bit address as follows:

The remaining bit, the high order bit, is called the OPSPEC bit. Its function is to prepare for the evaluation of the next operand. In the case of the IRD1 ROM, if OPSPEC is set, it performs the following functions:

- (1) It causes the OSR to be loaded (from the XB) with the first operand specifier of the current VAX instruction.

- (2) It loads the DSIZE latches from the DSIZE ROM. The data type of the current operand being evaluated is contained in the DSIZE latches. Since an opcode with several operands can have several different data types, the DSIZE ROM specifies the data type of each operand of each opcode. The DSIZE ROM is indexed by opcode and by the IRDCNT register, which keeps track of which operand is being evaluated.

- (3) It specifies that the four low order bits of the 14 bit CSA formed above are to be ORed with a four bit encoding of the addressing mode of the first operand specifier. Since the operand is to be evaluated, and since that evaluation is a function of the addressing mode of the operand specifier, the branch address must take the addressing mode into account.

### THE IRDX ROM

The IRDX ROM consists of 2K words, each containing 15 bits. As in the case of the IRD1 ROM, the high order bit is the OPSPEC bit. It provides all the functions that the OPSPEC bit does in the IRD1 ROM, and in addition it increments the IRDCNT register. The remaining 14 bits constitute a 14 bit address which is used to obtain the CSA of the next microinstruction. As with the IRD1 ROM, this address is first modified by an encoding of the addressing mode of the operand specifier if the OPSPEC bit is set.

The IRDX ROM itself is addressed by 11 bits, as follows:

- 1. The opcode (this time taken from the IR where it has been present since the last BUT/IRD1 micro-order). 8 bits.

- 2. Whether or not register mode.

- 3. Whether or not the Floating Point Accelerator is present.

- 4. The low order bit of IRDCNT.

As will be seen, the IRDX ROM is used to obtain a CSA only if the second operand is being evaluated or if a branch to opcode-specific execution code is to be taken. The low order bit of the IRDCNT is used to distinguish between these two cases.

## DSIZE ROM

The DSIZE ROM consists of 2K words, each containing two bits. The two bits specify the data type ( whether byte, word, longword, or opcode dependent) of each operand of each opcode. Eleven bits are needed to address the DSIZE ROM. The eight high order bits come from the opcode; the three low order bits come from the IRDCNT register. The figure below shows the contents of the DSIZE ROM pertaining to a typical <opcode>.

| Data type of 052  | ]: <opcode>\$</opcode> |

|-------------------|------------------------|

| Data type of OS 3 | : <opcode> 1</opcode>  |

| Data type of 054  | : copcode > 2          |

| Data type of 055  | : copcode > 3          |

| Data type of 056  | : <opcode> 4</opcode>  |

| Not used          | : copcode >5           |

| Not used          | : copcode > 6          |

| Data type of OS1  | : copcode > 7          |

|                   | •                      |

# 2.3.2 Processing of the BUT codes.

## BUT/IRD1

The detection of BUT/IRD1 in the current microinstruction is the signal that this is the last microinstruction in the emulation of the current machine instruction, and that the microarchitecture is to begin processing the next machine instruction. The hardware routine DOSERVE is invoked to initiate the service of any interrupts which may be pending. If there are no higher priority interrupts pending (or after they are serviced), two bytes are fetched from the XB; the first is loaded into the IR, the second is loaded into the OSR. Simultaneously, the IRD1 ROM If the OPSPEC bit is not set, the loading of the is addressed. OSR is inhibited. In either event, the CSA is specified as described in Section 2.3.1 above. Whether or not the OPSPEC bit is set, IRDCNT is forced to 7 at the beginning of the microcycle, which allows the DSIZE latches to be set from the DSIZE ROM (in case the OPSPEC bit is set), and then cleared to 0 at end of the microcycle.

#### BUT/IRD1TST

The BUT/IRDITST code is used to test the hardware. It functions exactly like the BUT/IRD1 code except that the CSA is taken directly from the NEXT field of the microinstruction. This can be used, for example, to test if the IR and OSR have been loaded properly, the IRDCNT cleared, etc. without losing control of the microinstruction flow. The next microinstruction executed is the one at the address specified by the NEXT field, rather than the one addressed by the ROM. Note that since the address specified by the NEXT field would have NEXT<3:0> ORed with an encoding of the addressing mode if OPSPEC is set, it may be desirable to specify NEXT <3:0>=1111 to avoid that multi-way branch.

#### BUT/IRDX

The detection of BUT/IRDX in the current microinstruction is the signal that this is the last microinstruction in the evaluation of the current operand, and that the microarchitecture is to begin its next step. IRDCNT is examined. If IRDCNT is 0 or 1, the IRDX ROM is addressed and the CSA is formed as described in Section 2.3.1. This is the mechanism used for branching to the microcode to evaluate the second operand and to begin execution of opcode-specific microcode. If IRDCNT is greater than 1, the CSA is obtained by popping the microstack. In this case, the loading of the OSR, incrementing the IRDCNT and further addressing mode branching for the purpose of evaluating the remaining operands is controlled in the subsequent microcode by means of BUT/BRA.ON.ADD, BUT/LOD.INC.BRA, and BUT/LOD.BRA codes.

## BUT/LOD.INC.BRA.

This code loads the OSR, increments IRDCNT, and determines the CSA of the next microinstruction in the same way that BUT/IRD1 does with OPSPEC set. This code is used to evaluate operands when the OSR has not been previously loaded.

#### BUT/BRA.ON.ADD

This code does not load the OSR, and does not increment the IRDCNT. This code is used when the OSR has been previously loaded and IRDCNT has been properly set. The CSA of the next microinstruction is formed as in BUT/LOD.INC.BRA.

#### BUT/LOD.BRA.

This code loads the OSR and then forms the CSA as in BUT/LOD.INC.BRA. The IRDCNT is not updated. This code is used in evaluating the Base Operand Address in index addressing mode. Since the BOA is the second operand address to be evaluated for the one operand, the IRDCNT must not be changed.

### 2.3.3 AN EXAMPLE

We conclude this section with an example, showing how the BUT codes are used in emulating a VAX machine instruction.

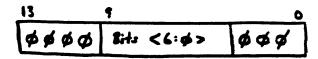

Example 2.6 Consider a VAX machine instruction having five operands, with the fourth operand specifier designating index mode. Figure 2.7 illustrates the flow of control to emulate the machine instruction.

Emulation starts at (1), the last microinstruction of the microcode which emulates the previous machine instruction. BUT/IRDl is a signal to begin the emulation of this machine instruction. The IRDl ROM is addressed. Since OPSPEC=1 the OSR is loaded with the first operand specifier. The DSIZE latches are set from IRDCNT=7, IRDCNT is set to 0 and a branch is taken to B, the microcode to evaluate the first operand. Note that B (as well as C,E,F,G, and H) is common code. It is independent of the opcode. It depends only on the addressing mode of the operand specifier, and that addressing mode was used in computing the branch address.

The last microinstruction in the evaluation of the first operand (2) contains BUT/IRDX. Since IRDCNT=0, the IRDX ROM is addressed, using IRDCNT <0> as part of its index. Since OPSPEC=1, the OSR is loaded with the second operand specifier, the DSIZE latches are set according to IRDCNT=0, IRDCNT is incremented, and a branch is taken to C, the microcode to evaluate the second operand.

The last microinstruction in C contains BUT/IRDX. IRDCNT is still less than 2 (IRDCNT=1), the IRDX ROM is again addressed. Since OPSPEC=1, the OSR is loaded with the third operand specifier, the DSIZE latches are set according to IRDCNT=1, IRDCNT is incremented, and a branch is taken to D. The four low-order bits of the branch address would be obtained by ORing the four low-order bits in the IRDX ROM with an encoding of the addressing mode contained in OSR. Thus, to insure that the branch taken is to D, it is necessary to insist that the four low-order bits of D be 1111, and that the four low-order bits in IRDX ROM also be (Alternatively, we could have set OPSPEC=0, in which case there would be no branching on addressing mode, and there would be no such restriction on the nature of the control store address D. In that case, the BUT micro-order at (4) would have to be LOD.INC.BRA in order to load OSR and update IRDCNT.)

The microcode starting at D is specific to the VAX machine instruction being emulated.\* After executing some number of microinstructions (perhaps none), the microinstruction at 4 is executed. This is a branch to E, the common microcode to evaluate the third operand. The BUT/BRA.ON.ADD code is used since the OSR has already been loaded and the IRDCNT has already been incremented. Both occurred at (3). The JSR/PUSH code is included to store the CSA of (4) on the microstack.

The last microinstruction in E contains BUT/IRDX. Since IRDCNT=2, the net effect is to pop the microstack, causing a branch to (6) due to NEXT/1. In order to evaluate the fourth operand, BUT/LOD.INC.BRA is used. This causes the OSR to be loaded with the fourth operand specifier, IRDCNT to be incremented, and a branch to the common code at F.

We have assumed that the fourth operand specifier designated index mode. Index mode requires a second operand specifier (called the base operand specifier) for this one operand. At some point, therefore, we must load that operand specifier and branch to the common code to evaluate it. We do not increment IRDCNT since we are still dealing with the fourth operand. This is accomplished by BUT/LOD.BRA at (7).

If that were not the case, for example, if the microcode at D were common code used to evaluate the third operand, there would be no way to return control to the emulation of the current machine instruction.

Processing continues in this vein until (11), at which point all five operands have been evaluated. BUT/IRDX pops the stack (IRDCNT=4) and control goes to (12), the microcode to complete the emulation of the current VAX machine instruction.

Figure 2.7 Microsequence Flow Using ROMs. (Example 2.6)

| BUT FIELD                                                                                                                    | CSA<5> | CSA<4> | C5A<3>   | CSA<2>               | CSA<1>                                                               | CSA<0>                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------|--------|--------|----------|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUTXB=20<br>CM.ODD.ADD=21<br>1R.2T00=19<br>1R5=23<br>IR2=22<br>REGMODE=24                                                    |        |        |          | ŢR<2>                | IR<1>                                                                | BUT XB UTRAP = 1, ELSE 0<br>  NOTE 2<br>  IR<0><br>  1R<5> (NOTE 8)<br>  IR<2> (NOTE 8)<br>  OSR<7:4>=5                                                                                                            |

| FRO.FLTZ=2A<br>WBUS1TOO=9<br>WBUS1TOO.NE.O=0E<br>WBUS5TOO=08<br>WBUSO=0A<br>WBUS31TO30=1B                                    | WB<5>  | WB<4>  | wB<3>    | wB<2>                | NOT.MBUS<15><br>WBU5<1><br>WB<1><br>WB<31>                           | WX<31:0>.NE.0<br>WBUS<0><br>WBUS<1:0>.NE.0<br>WB<0><br>WB<0><br>WB<30>                                                                                                                                             |

| WX.EQ.0=28 WX.NE.0=29 BCDCHK=26 SRKSTA=37 SPASTA=2E CCBR=2D CCBR1.CCBR0.IR0=35 CCBR0.SRKSTA0=36 DSIZE=31 DBZ.SC=0C WCSENA=27 |        |        |          | CCBR<1>              | SRKSTA<1> SPASTA<1> CCBR<1> CCBR<0> CCBR<0> CCBR<0> CCBR<0> DSIZE<1> | WMUX<31:0>.EQ.0 WMUX<31:0>.NE.0 NOTE 1 SRKSTA<0> (NOTE 6) SPASTA<0> (NOTE 5) CCBR<0> (NOTE 7) .NOT.IR<0> (NOTE 8) SRKSTA<0> DSIZE<0> (LATCHES) SC.EQ.0 0=WCS PRESENT AND ENABLED 1=WCS NOT PRESENT OR WCS DISABLED |

| BR.SC-4.INT-TS=0D<br>MM.ALLOW.INT=0B<br>INT-TIMSERV=2B<br>CCBR1.INT-TS=2C                                                    |        |        |          | NOTE 3               | NOTE 3<br>NOTE 4<br>.NOT.INT<br>CCBR<1>                              | NOTE 3  TIMSERV (INT.OR.TIMSERV).AND.NOT.CCBR<1>                                                                                                                                                                   |

| FPD=OF<br>PSLC=25<br>PSLTP=2F<br>UVCTR=1E<br>FPS1=34<br>FPS2=33<br>FPS3=32<br>FLAGO=10<br>FLAG1=17                           |        |        | UVCTR<3> | UVCTR<2><br>NOT.HALT | UVCTR<1> START<1> BOOT<1> ACLO FLAG1                                 | PSL<27> PSL <c> PSL<c> PSL<tp> UVCTR&lt;0&gt; (NOTE 9) START&lt;0&gt; BOOT&lt;0&gt; (NOTE 10) FPLOCK FLAGO</tp></c></c>                                                                                            |

| FLAG2=12<br>FLAG3=13<br>MM.NOINT=11<br>STACKFLG=1A<br>FLAG2T00=16<br>FLAG1T00=14<br>F1.XOR23=15                              |        |        |          | FLAG2<br>FLAG2       | FLAG1<br>FLAG1<br>FLAG1                                              | FLAG3 MM.NOINT (FLAG4) PSHSTACK (FLAG5) FLAG0 FLAG0 FLAG2.XOR.FLAG3                                                                                                                                                |

# CHAPTER 3. THE DATA PATH, PART I: THE ALU

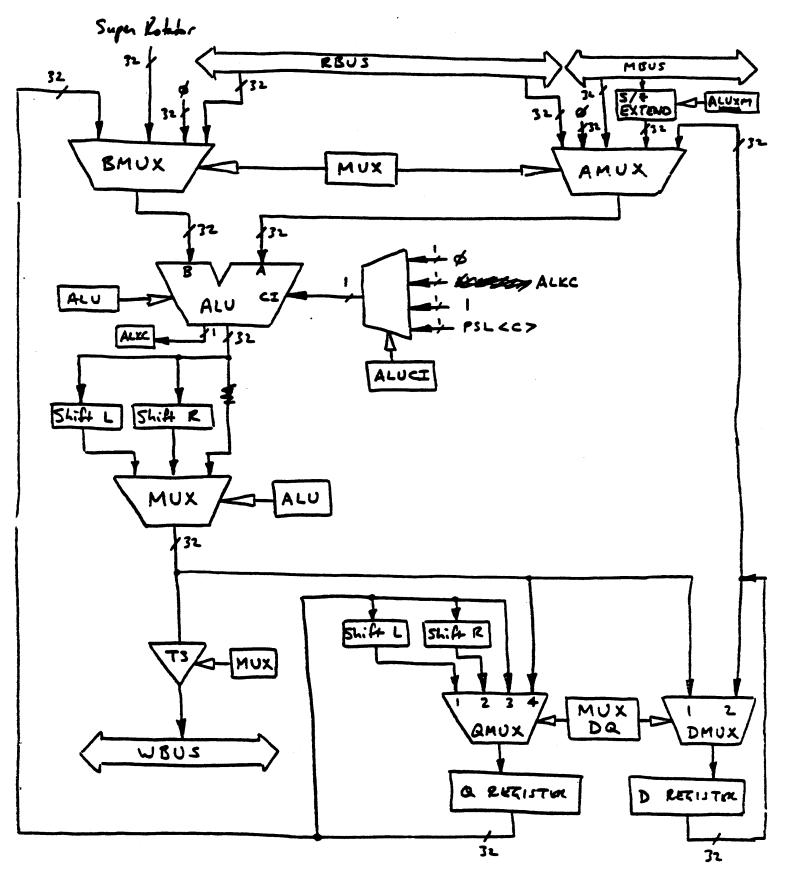

The computational element of the COMET microarchitecture is the Data Path. In this chapter, we discuss that part of it consisting of the ALU, the D and Q registers, the ALKC, ALUSO, and LOOP flags, and the necessary logic to support the relevant fields of the microinstruction. We call this part of the Data Path the ALU system. In Chapter 4, we will discuss the rest of the Data Path, in particular, the Super Rotator and the Scratch Pad registers.

Inputs to the ALU come from the RBUS, the MBUS, the Super Rotator, and the D and Q registers. Output of the ALU goes to the WBUS, the D register and/or the Q register. The ALKC flag is set during add and subtract operations to reflect a carry out of the ALU during addition or a borrow for the most significant bit during subtraction. The ALUSO and LOOP flags are used in the multiply and divide operations. Figure 3.1 is an overall block diagram of the ALU system.

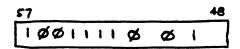

The fields of the microinstruction that control the functioning of the ALU are shown below:

| 63 (     | 26160    | त्र ध  | 57     | ถ | SF | 54  | 53 | n | 51 | n | 49 | 14 |

|----------|----------|--------|--------|---|----|-----|----|---|----|---|----|----|

| A ALUSHF |          |        | MUX    |   |    | ALU |    |   | DQ |   |    |    |

| X        | WC 03414 | Near F | ALPCTL |   |    |     |    |   |    |   |    |    |

| ROT      |          | 1      |        |   |    |     |    |   |    |   |    |    |

We will study the ALU in several parts. In section 3.1, we identify the basic functionality of the ALU system; i.e., that involving the ALUXM, ALUCI, MUX, ALU and DQ fields. In this case, the inputs to the ALU are specified by the MUX, ALUCI, and ALUXM fields. The function performed by the ALU is specified by the ALU field, and the destination of the output of the ALU is controlled by the MUX and DQ fields. In section 3.2, we show how the ALUSHF field provides for shifting and rotating the output of the ALU, the Q register, and both. In section 3.3 we discuss the ALU special functions, wherein the 10 bit field ALPCTL specifies as a unit the entire ALU operation (i.e., inputs, function, and destination of output).

Figure 3.1 ALU System - Overall Block Diagram

Note that the above field specifications provide opportunity for two sets of conflicts. The first set of conflicts involves bits <57:48>. It is resolved in the following way. If the ALPCTL field specifies one of the 50 special functions (from a set of 1024 possible codes), then that special function is performed rather than the separately decoded MUX, ALU, and DQ fields. For example, if bits <57:48> are specified as

then the hardware performs the fast multiply operation (ALPCTL/MULFAST), instead of setting the D register to the logical-AND of the RBUS and the complement of the D register and shifting the Q register one bit to the right (MUX/D.R2, ALUOD/ANDNOT.OD, DQ/SQR.D..WX).

The second set of conflicts involve bits <63:58>. This field is also the ROT field which controls the Super Rotator (see Section 4.1). This conflict is resolved as follows: If the MUX field specifies that the output of the Super Rotator is to be an input of the ALU or if the ROT field specifies the loading of either of its two (P or S) latches (again, see Section 4.1), then the ALUSHF field and the ALUCI field, are both disabled. Their control functions operate as if the codes specified were 0. The ALUXM field, on the other hand, is not disabled. It continues to function on the basis of the value in bit <63>.

#### 3.1 Basic Functioning

The basic funtioning of the ALU is shown in Figure 3.2. The ALU has three inputs: 32 bit A and B inputs and in the case of arithmetic operations, a single bit carry input (CI). The A and B inputs are both multiplexed under the control of the MUX field. The CI input is multiplexed under the control of the ALUCI field. The function performed by the ALU is specified by the ALU field. The ALU generates a 32-bit ouput and in the case of arithmetic operations, a one bit carry out (ALKC). The destination of the output of the ALU is controlled by the MUX field in conjunction with the DQ field.

Table 3.1 shows the multiplexing of the A and B inputs to the ALU. Sources for the AMUX are the MBUS, the RBUS, the constant 0, and the D register. In those cases where the MBUS source as specified by the MSRC field is less than 32 bits, the MBUS is sign or zero extended to 32 bits before it is applied to the AMUX. The ALUXM field specifies whether the extension should be sign extend or zero-extended. Sources for the BMUX are the RBUS, the output of the Super Rotator, the Q register and the constant 0.

Figure 3.2 Basic Functioning of the ALU

Table 3.2 shows the functions performed by the ALU as specified by the ALU field. Note that certain functions specify that the output of the ALU should be shifted one bit right or left before being output to the WBUS, D register, or Q register. The details of that shifting mechanism will be covered in the next section.

The destination of the output of the ALU is controlled by the MUX field in conjunction with the DQ field. The MUX field alone controls whether or not the ouput of the ALU is to go on the WBUS. Note the tri-state device between the output of the ALU and the WBUS (figure 3.2). If the MUX field specifies a binary code of 1001 or 1101, the output is inhibited. For all other MUX codes, the output of the ALU goes on the WBUS. In the case of the D and Q registers, the MUX field acts in a bit steering capacity for the DQ field. Table 3.3 shows the details of that control. Note that in certain cases, the Q register is shifted one bit to the left or right. Details of that shift mechanism will be covered in the next section.

#### 3.2 The Single Bit Shift Operation

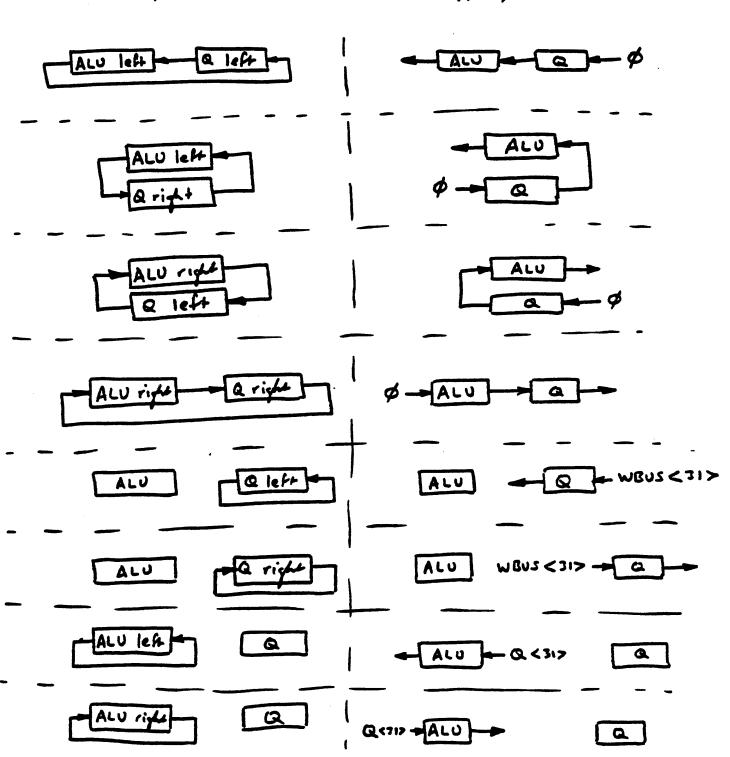

As was stated in Section 3.1, the Q register and the output of the ALU can be shifted one bit left or right before being applied to their respective destinations. Four fields are involved in the control of the shift operation. The ALU field (cf. Table 3.2) specifies whether the output of the ALU is to be shifted right, left, or not at all. The MUX and DQ fields (cf. Table 3.3) specify whether the Q register is to be shifted right or left or not at all. The ALUSHF field specifies the bits to be shifted into the Q register and to the output of the ALU. Table 3.4 delineates the ALUSHF specification.

Two of the codes in Table 3.4 (ALUSHF/SHF and ALUSHF/ROT) require some explanation. In these two cases the ALU output and the Q register can be treated as if they were a 64 bit register. Figure 3.3 illustrates the shift operation for each of the 16 cases.

#### 3.3 Special Functions - The ALPCTL field

The field <57:48> has 1024 possible codes. For all but 50 of them, the MUX, the ALU, and DQ fields are decoded as described in Section 3.1 to determine the functioning of the ALU system. In the remaining 50 cases, the 10 bits are decoded as a

Figure 3.3 Shift Operation for ALUSHF/SHF and ALUSHF/ROT Micro-orders

unit (i.e., the ALPCTL field) to specify the functions to be performed. Figure 3.4 is a block diagram of the data flow for the ALPCTL functions. Table 3.5 lists the 50 functions.

Note in particular the multiply and divide operations which are implemented respectively as sequences of shifts and adds and subtracts. The ALUSO and LOOP flags are provided to aid in the microprogramming of these operations. Consider, for example, the multiply routine. LOOP is set during the first iteration of a multiply routine and then used to control subsequent iterations. ALUSO is the bit shifted out of the ALU. Since multiply is implemented as a sequence of shifts and adds, ALUSO contains the low order bit of the multiplier which is used to determine whether or not the multiplicand should be added to the partial product.

Figure 3.4 Data Flow for the ALPCTL functions

Table 3.1 Sources for the A and B inputs to the ALU

| MUX      | A input    | B input       |

|----------|------------|---------------|

| 0000     | MBUS       | RBUS .        |

| 0001     | MBUS       | RBUS          |

| 0010     | MBUS       | Q REGISTER    |

| 0011     | MBUS       | Q REGISTER    |

| 0100     | MBUS       | Super Rotator |

| 0101     | Ext. MBUS  | RBUS          |

| 0110     | Ext. MBUS  | Q Register    |

| 0111     | Ext. MBUS  | Super Rotator |

| 1000     | D Register | RBUS          |

| 1001(0)* | D Register | RBUS          |

| 1001(1)* | D Register | Constant 0    |

| 1010     | D Register | Q Register    |

| 1011     | D Register | Q Register    |

| 1100     | D Register | Super Rotator |

| 1101     | Constant 0 | Super Rotator |

| 1110     | RBUS       | Q Register    |

| 1111     | RBUS       | Super Rotator |

Bit <49> is steering bit for MUX/1001

Table 3.2 ALU Function Control of the ALU

| ALU  | FUNCTION                                             |

|------|------------------------------------------------------|

| 0000 | A - B - CI                                           |

| 0001 | A - B - CI in BCD                                    |

| 0010 | A - B - CI and shift the result right one bit        |

| 0011 | A - B - CI and shift the result left one bit         |

| 0100 | A + B + CI                                           |

| 0101 | A + B + CI in BCD                                    |

| 0110 | A + B + CI and shift the result right one bit        |

| 0111 | A + B + CI and shift the result left one bit         |

| 1000 | logical-AND (A,B)                                    |

| 1001 | logical-OR (A,B)                                     |

| 1010 | logical-AND (A,B) and shift the result right one bit |

| 1011 | logical-AND (A,B) and shift the result left one bit  |

| 1100 | B - A - CI                                           |

| 1101 | exclusive-OR (A,B)                                   |

| 1110 | logical-AND (A, not B)                               |

| 1111 | logical-AND (not A, B)                               |

Table 3.3 MUX, DQ Control of D and Q Registers

If MUX/1001 (Binary)

| DQ field | <u>Q</u> | <u>D</u>  |

|----------|----------|-----------|

| 00       | 1*       | 1**       |

| 01       | 2        | $\bar{1}$ |

| 10       | <b>1</b> | ī         |

| 11       | 2        | 1         |

If MUX/(0001 or 0011 or 1011)

| DQ field | <u>Q</u> | <u>D</u> |

|----------|----------|----------|

| 00       | 1        | 2        |

| 01       | 2        | 2        |

| 10       | 1        | 1        |

| 11       | · 2      | 1        |

If MUX/anything else

| DQ field | <u>Q</u> | <u>D</u> |

|----------|----------|----------|

| 00       | 3        | 2        |

| 01       | 4        | 2        |

| 10       | 3        | 1        |

| 11       | 4        | 1        |

<sup>\*</sup> Numbers in this column are taken from the QMUX inputs in Figure 3.2

Numbers in this column are taken from the DMUX inputs in Figure 3.2

Table 3.4 ALUSHF control for the Single bit Shift Operations

| ALUSHF  | ALU                 | <u>Q</u>            |

|---------|---------------------|---------------------|

|         |                     |                     |

| ZERO    | 0                   | 0                   |

| ONE     | 1                   | 1                   |

| SHF     | Shift ALU'Q togethe | r (see figure 3.3)  |

| ROT     | Rotate ALU Q togeth | er (see figure 3.3) |

| ALU0.Q1 | 0                   | 1                   |

| ALU1.Q0 | 1                   | 0                   |

| WBUS 30 | WBUS<30>            | WBUS<30>            |

| PSLC    | PSL <c></c>         | PSL <c></c>         |

## Table 3.5 ALPCTL Special Functions

| ALPCTL code                                                                                                                                                           | RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WX D Q Q D WX D Q Q M WX D R Q M WX D R Q M WX D R Q XM WX D S Q C WX D S Q XM WX D S Q XM WX Q Q D WX Q Q M WX R Q D WX R Q M WX R Q M WX R Q XM WX S Q XM WX S Q XM | WMUX,D < Q OLD Q < D OLD WMUX,D < Q OLD Q < MBUS WMUX,D < RBUS Q < D OLD WMUX,D < RBUS Q < MBUS WMUX,D < RBUS Q < S/Z MBUS WMUX,D < SUP ROT Q < O WMUX,D < SUP ROT Q < RBUS WMUX,D < SUP ROT Q < S/Z MBUS WMUX,D < SUP ROT Q < S/Z MBUS WMUX,D < SUP ROT Q < D WMUX < Q OLD Q < D WMUX < Q OLD Q < MBUS WMUX < RBUS Q < D WMUX < RBUS Q < D WMUX < RBUS Q < MBUS WMUX < RBUS Q < MBUS WMUX < RBUS Q < S/Z MBUS WMUX < SUP ROT Q < O WMUX < SUP ROT Q < RBUS WMUX < SUP ROT Q < RBUS WMUX < SUP ROT Q < S/Z MBUS |

| WX_D_Q_S WX_D_S WX_Q_S WX_S WX_D_QNOT.S WX_DNOT.S WX_QNOT.S WX_QNOT.S                                                                                                 | WMUX,D&Q < SUPER ROTATOR WMUX,D < SUPER ROTATOR WMUX,Q < SUPER ROTATOR WMUX < SUPER ROTATOR WMUX,D&Q <not. (super="" <not.="" rotator)="" rotator)<="" td="" wmux="" wmux,d="" wmux,q=""></not.>                                                                                                                                                                                                                                                                                                                |

| WX_D_DSL.SQL<br>WX_D_DSL.SQR<br>WX_D_DSR.SQL<br>WX_D_DSR.SQR                                                                                                          | WMXU,D < D SHF LEFT Q < SHF LEFT WMXU,D < D SHF LEFT Q < SHF RIGHT WMXU,D < D SHF RIGHT Q < SHF LEFT WMXU,D < D SHF RIGHT Q < SHF RIGHT                                                                                                                                                                                                                                                                                                                                                                         |

| WB_LOOPF WB_LOOPF.Q_0 WB_LOOPF.D_0 WB_LOOPF.Q_D_0 WB_ALUF WB_ALUF.Q_S WB_ALUF.D_S WB_ALUF.Q_D_S                                                                       | WB<31:30> < 0'LOOP FLAG WB<31:30> < ALUSO'ALKC WB<31:30> < S                                                                                                                                                                                                                                 |

| MULFAST+ MULSLOW+ MULFAST- MULSLOW- DIVFAST+ DIVSLOW+ DIVFAST- DIVSLOW- REM | MULTIPLY +RBUS BY Q MULTIPLY +RBUS BY Q MULTIPLY -RBUS BY Q MULTIPLY -RBUS BY Q DIVIDE Q BY +RBUS DIVIDE Q BY +RBUS DIVIDE Q BY -RBUS DIVIDE Q BY -RBUS UNSHIFT REMAINDER | (1 ITERATION<br>(2 ITERATIONS<br>(1 ITERATION | PER CYCLE) |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|

| DIVDA<br>DIVDS                                                              | DIVIDE DOUBLE ADD<br>DIVIDE DOUBLE SUB                                                                                                                                    | (KBUS MUST BE                                 | 0)                                                                           |

# CHAPTER 4. THE DATA PATH, PART II: THE SUPER ROTATOR AND THE SCRATCH PAD REGISTERS

This chapter continues the description of COMET's Data Path with discussions of the Super Rotator and the Scratch Pad registers. The efficient bit manipulation capability of the Super Rotator and the easy accessibility of the Scratch Pad registers make these features very useful to the user microprogrammer.

#### 4.1 The Super Rotator

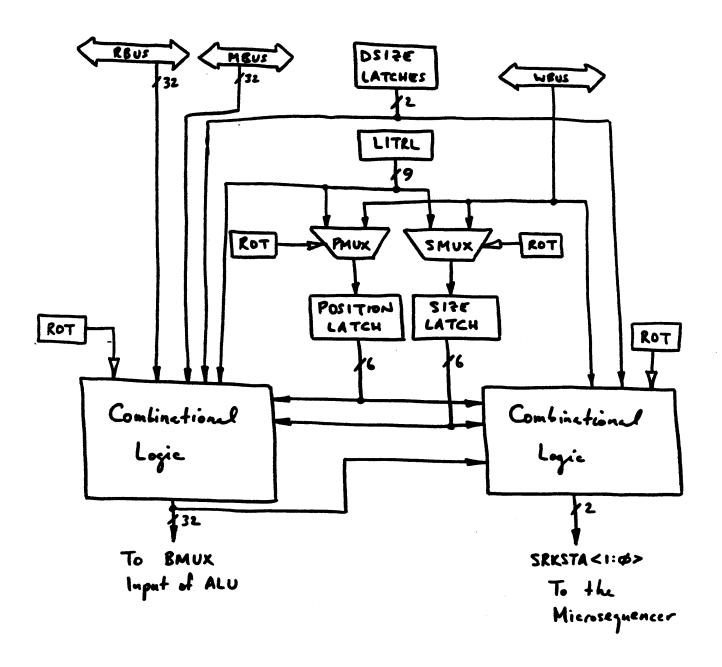

The Super Rotator consists of two powerful combinational logic circuits and the six bit POSITION and SIZE latches. The purpose of the Super Rotator is to generate two outputs: a 32 bit data element and a two bit status code (SRKSTA <1:0>). Figure 4.1 is an overall block diagram of the Super Rotator.

Inputs to the Super Rotator are obtained from the three microarchitecture buses (MBUS, RBUS, and WBUS) and from the DSIZE latches. In addition immediate input data is available from the LITRL field of the current microinstruction. The 32 bit data output is applied to the B input of the ALU (cf. Section 3.1). The two bits of status information is applied to the microsequencer for use as a four-way branch (cf. Section 2.1). The Super Rotator is controlled by the ROT field (Bits <63:58>) of the current microinstruction.

As will be seen in the examples of tis section, the primary usefulness of the Super Rotator comes from the fact that the large combinational circuits provide a great deal of bit-manipulation capability at a much faster speed than could be done in microcode.

#### 4.1.1 32 Bit Data Output

There are 64 ways in which the Super Rotator can produce its 32 bit data output, one for each of its 64 ROT micro-orders. They are listed in Table 4.1. Several are explained below, along with examples.\*

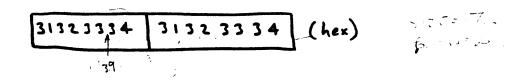

In each of the examples of this section, MBUS=31323334 (hex), RBUS=35363738 (hex), POSITION latch = 22 (decimal), SIZE latch = 17 (decimal), DSIZE latches = 10(Binary), and LITRL = 032 (hex).

Figure 4.1 Super Rotator - Overall Block Diagram

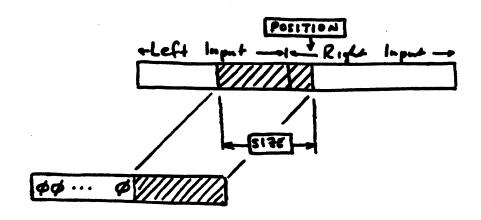

(1) Extract and zero extend. The two 32 bit inputs specified by the ROT code are concatenated, forming a 64 bit element. From this, s bits (the SIZE), starting at bit p (the POSITION) are extracted. The 32 bit output is formed by adding 32-s high order 0's. The general mechanism is shown below:

Specific cases are shown in Examples 4.1 and 4.2.

Example 4.1. If ROT/XZ.MM is specified, the Super Rotator concatenates M'M (recall from the footnote on page 4-1 that the MBUS contains the hex number 31323334)

extracts

and outputs

As is the case in many of the ROT codes, the SIZE latch specifies the number of bits to be extracted, and the POSITION latch specifies the position of the low order bit.

Example 4.2 If ROT/XZ.VPN is specified, the Super Rotator outputs

# \$\$ 189919 (hex)

Note that in example 4.1, the size and position of the fields to be extracted are specified by the SIZE and POSITION latches respectively. In example 4.2, the size and position are constants specified by the ROT/XZ.VPN code; i.e., size is 21, position is 09. The ROT code specifies the number of bits to be extracted (or shifted or rotated) and the position of the low-order bit. The ROT code can specify these numbers as constants, as in ROT/XZ.VPN, or as quantities to be evaluated, as in ROT/XZ.MM.

- (2) <u>Clear bytes.</u> The MBUS is used as the input, the specified number of low order bytes are cleared, and the result is output.

- Example 4.3. If ROT/CLR3BM is specified, the Super Rotator

outputs

## 31 0000000

- (3) Rotate. The two 32 bit inputs specified by the ROT code are concatenated, forming a 64 bit element. The result is rotated (i.e., shifted end-around) the specified number of bits, and the low order 32 bits are output.

- Example 4.4. If ROT/RL.RM.PS is specified, the Super Rotator

concatenates R'M

3536373831323334

rotates left seven bits - since (22+17) mod 32 = 7, and outputs

## 99199818

(4) Convert Numeric to Packed. The VAX-11 architecture provides a numeric data type where each decimal digit is stored in one byte, and a packed data type where two decimal digits are stored in one byte. The Super Rotator provides the capability for converting data from one type to the other.

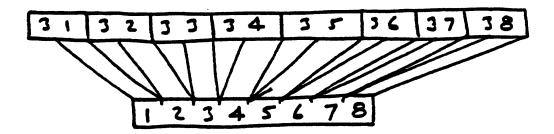

Example 4.5. The ROT/CVTNP code takes the 8 bytes specified by M'R and produces the 32 bit output shown

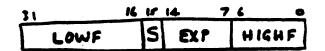

(5) Pack and Unpack Floating Point Fraction. The VAX-11 architecture stores a floating point number in four bytes, as follows:

where S = the sign bit, EXP = the exponent in excess-120 code, HIGHF = the high order bits of the fractional part, LOWF = the low bits of the fractional part. The fractional part consists of 24 bits. The redundant most significant bit is not stored. The next 7 bits, in decreasing order of significance, are stored in bits 6 through 0. The next 16 bits, in decreasing order of significance, are stored in bits 31 through 16.

The Super Rotator provides the capability for recombing the fractional part in a more useable form.

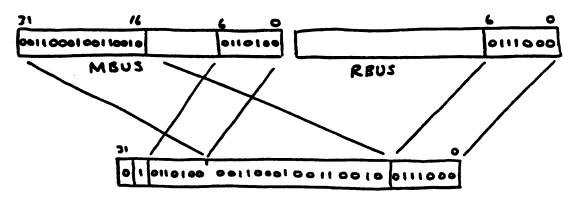

Example 4.6 If ROT/GETFPF is specified, the Super Rotator takes the data on the MBUS and RBUS and produces the 32 bit output shown below:

Note that the redundant most significant bit is now present (Bit <30> of the output), and that the 24 bit fraction is combined in its useable form (Bits <30:7>). Note also that the low order bits (<6:0>) contain the exponent, no longer in excess-code.

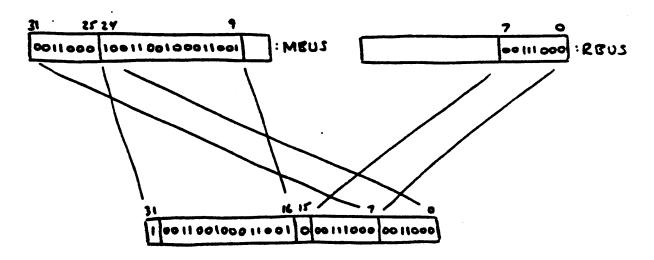

Example 4.7. To recombine the floating point number into its VAX-11 floating data type, ROT/FPACK is used. The Super Rotator takes the data on the MBUS and RBUS and produces the 32 bit output shown below

Note that before ROT/ $\bar{F}$ PACK can be used, the fractional part (on -4-6 -

the MBUS) first must be shifted left until the most significant bit is shifted out, and that the exponent (on the RBUS) first must be expressed in excess-128 code.

- (6) Constants. The ROT field can specify that the 32 bit output be one of the following constants: 0, -1, 1, 2, 4, or 8. Specification of the constant 1, 2, 4, or 8 is by means of ROT/CONX.SIZE. Which one is output is determined by the state of the DSIZE latches, i.e., by 0, 1, 2, or 3 respectively.

- (7) Literal. The ROT field, together with the LITRL field can specify a 32 bit field which is particularly useful for masking operations. The nine bit LITRL field is extended to 32 bits by 23 0's or 23 1's and then rotated a specified number of nibbles. The result is a 32 bit mask such that the nine-bit LITRL field is properly aligned to make the desired test, and the other 23 bits are all 0's or all 1's as is necessary for the test.

Example 4.8 If ROT/OLIT8 is specified, the Super Rotator produces

FFFE 32FF

#### 4.1.2 SRKSTA Status Bits.

The Super Rotator also produces a two bit code containing status information relating to the state of certain signals in the microarchitecture. Recall that these two bits SRKSTA <1> and SRKSTA <0> are applied to the microsequencer for use as a four-way branch.

Table 4.2 shows the specification of the two status lines. Note that the ROT field has been relabeled ROTSRK, and the 64 micro-orders have been relabeled with more relevant mnemonics, as well.\* The specification of SRKSTA <1:0> for absolute value check, ASCII sign check, and for WBUS range check will be described below. The other micro-orders are more straightforward, as shown by examples 4.9 and 4.10.

Example 4.9. ROTSRK/DSIZE.020 specifies that the SRKSTA <1:0> will be formed as follows:

SRKSTA<1> = 1 iff DSIZE <1> = 1 SRKSTA<0> = 1 iff DSIZE <0> = 1

with the result that the SRKSTA <1:0> code conveys the status of the DSIZE latches.

Example 4.10. ROTSRK/PL.EQ.0.SIGN.120 specifies that the SRKSTA <1:0> code conveys the state of the POSITION latch, as follows:

| SRKSTA<1:0> | POSITION LATCH                             |

|-------------|--------------------------------------------|

| 00<br>01    | POSITION LATCH = 0<br>POSITION LATCH = 16  |

| 10<br>11    | 1< POSITION LATCH < 15 POSITION LATCH > 16 |

Recall from the introduction to Chapter 3 that a possible conflict can exist between the ROT field (Bits <63:58>) and the ALUSHF (Bits <62:60>) and ALUCI (Bits <59:58>) fields. In particular, if the ROT field specifies loading either POSITION or SIZE latch, or if MUX specifies the output of the Super Rotator as the B input to the ALU, the ALUSHF and ALUCI default to 0. However, if the ROT field is only concerned with SRKSTA<1:0>, then the ALUSHF and ALUCI are available. The relabeling of Bits <63:58> in Table 4.2 is intended as a convenience to the microprogrammer, allowing the selection of the appropriate ROTSRK micro-order to control both SRKSTA<1:0> and ALUSHF-ALUCI, as well.

(1) Absolute Value Check. The condition tested is the absolute value of the low order byte on the WBUS.

Example 4.11. ROTSRK/ABSVAL.163.D specifies that SRKSTA <1:0> will be formed as follows:

The SRKSTA<1:0> code conveys the following information:

| SRKSTA<1:0> | WBUS<7:0>            |  |

|-------------|----------------------|--|

| 00          | -31 < WBUS<7:0> < -1 |  |

| 01          | - WBUS<7:0> ⋜ -32    |  |

| 10          | 0 < WBUS<7:0> ₹ 31   |  |

| 11          | - WBUS<7:0> ラ 32     |  |

(2) ASCII Sign Check. The condition tested is whether or not the low order byte on the WBUS is an ASCII sign.

Example 4.12. ROTSRK/ASCIISIGN.050 specifies that SRKSTA <1:0> will be formed as follows:

SRKSTA<1> = 1 iff WBUS<7:0> .NE. (32,43,45) SRKSTA<0> = 1 iff WBUS<7:0> .NE. 45

The SRKSTA<1:0> code conveys the following information:

| SRKSTA<1:0> | <u>wbus&lt;7:0&gt;</u>       |

|-------------|------------------------------|

| 00          | ASCII "-"                    |

| 01          | ASCII "+" or "space"         |

| 10          | not possible - machine error |

| 11          | not an ASCII sign            |

(3) WBUS Range Check. The condition tested is the unsigned value of the low order byte on the WBUS.

SRKSTA<1> = 1 iff WBUS<7:0>, as an unsigned

integer, is greater than 31.

SRKSTA<0> = 1 iff WBUS<7:0> .NE. (1,32)

The SRKSTA<1:0> code conveys the following information:

| SRKSTA<1:0> | <u>wbus&lt;7:0&gt;</u>     |  |

|-------------|----------------------------|--|

| 00          | 1 < WBUS<7:0> < 31         |  |

| 01          | $WB\overline{U}S<7:0> = 0$ |  |

| 10          | WBUS < 7:0 > = 32          |  |

| 11          | wbus<7:0> > 32             |  |

### 4.2 The Scratch Pad Registers

A register file is a set of very fast access storage registers. Almost every microprogrammable computer has one. Efficient emulation requires that the host machine have one available both for the purpose of storing frequently used constants and intermediate results and for the purpose of identifying the target machine's processor registers. COMET is no exception. Its register file consists of 48 R Scratch Pad registers, 16 M Scratch Pad registers, and a Long Literal register.\* All are 32 bits wide.

Two other structures are associated with the Scratch Pad registers, a four-bit RNUM register and a six-deep Register Back-Up Stack. RNUM is used for addressing both R and M Scratch Pad registers. The Register Back-Up Stack is used to restore the contents of the VAX general purpose registers (implemented with Scratch Pad registers) if it is necessary to undo the partial emulation of a VAX machine instruction in order to service an interrupt or exception. The state of RNUM or the state of the Register Back Up Stack is available as a two-bit status code (SPASTA<1:0>) for use by the microsequencer in performing a four-way branch.

Actually this is not quite correct; there are really eight fewer registers. This is because eight (i.e., RSP[00] through RSP[07] and eight of the 16 M Scratch Pad registers (i.e., MSP[0] through MSP[7]) are actually the same eight registers, accessible to both MBUS and RBUS.

Addressing the Scratch Pad registers is controlled by the RSRC and MSRC fields of the current microinstruction. Writing is controlled by the SPW field. Figure 4.2 is an overall block diagram of the Scratch Pad registers.

#### 4.2.1 Uses of the Registers

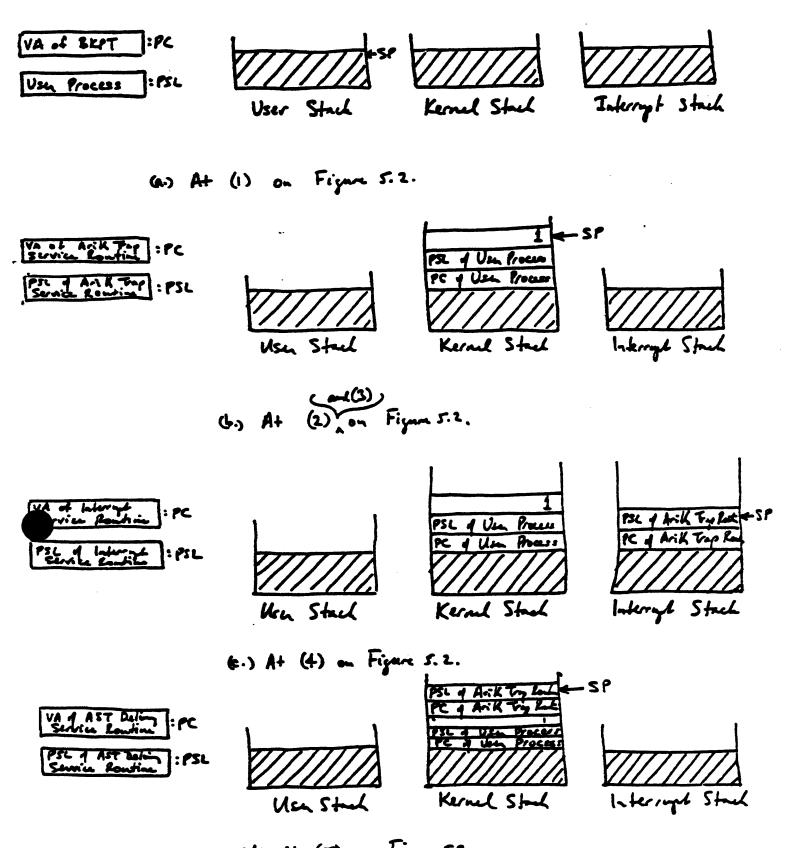

The 16 M Scratch Pad registers (MSP[0] through MSP[F]) are used as follows: