# decsystem10 MF10 CORE MEMORY MAINTENANCE MANUAL

1st Edition, August 1973 2nd Printing, December 1973

Copyright © 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

FLIP CHIP

**DECtape**

UNIBUS

DECsystem-10

PDP

**DEC**magtape

# **CONTENTS**

|           |                                                | Page   |

|-----------|------------------------------------------------|--------|

| CHAPTER 1 | GENERAL INFORMATION                            |        |

| 1.1       | GENERAL DESCRIPTION                            | . 1-1  |

| 1.2       | SYSTEM DESCRIPTION                             | . 1-1  |

| 1.3       | PHYSICAL DESCRIPTION                           | . 1-2  |

| 1.4       | SPECIFICATIONS                                 |        |

| 1.5       | OPERATION OVERVIEW                             |        |

| 1.5.1     | Read/Restore Cycle                             | . 1-7  |

| 1.5.2     | Clear/Write Cycle                              | . 1-7  |

| 1.5.3     | Read/Modify/Write Cycle                        | . 1-8  |

| 1.6       | MAJOR LOGIC SECTIONS                           |        |

| 1.6.1     | Port Control and Core Interface Section (PCCI) |        |

| 1.6.2     | Core Memory and Control Section (CMC)          |        |

| 1.6.2.1   | M7112 Control Logic                            |        |

| 1.6.2.2   | G231 Memory Driver                             |        |

| 1.6.2.3   | G113 Data Loops                                |        |

| 1.6.2.4   | H216 Stack                                     |        |

| 1.7       | INTERLEAVING                                   |        |

| 1.7       | INTERLEAVING                                   | . 1-10 |

| CHAPTER 2 | INSTALLATION                                   |        |

| 2.1       | SCOPE                                          | . 2-1  |

| 2.2       | SITE PREPARATION                               | . 2-1  |

| 2.3       | INSTALLATION PROCEDURE                         | . 2-1  |

| 2.3.1     | Cabling                                        | . 2-1  |

| 2.3.1.1   | Memory Bus                                     | . 2-1  |

| 2.3.1.2   | AC Power                                       | . 2-3  |

| 2.3.1.3   | Power Control                                  | . 2-3  |

| 2.3.1.4   | Ground Mesh Cable                              | . 2-3  |

| 2.3.2     | W974 Module Size Jumpers                       | . 2-3  |

| 2.3.3     | G726-YA Module Jumpers                         | . 2-4  |

| 2.3.4     | Memory Address Switch Settings                 | . 2-4  |

| 2.3.5     | Interleave Switch Settings                     |        |

| CHAPTER 3 | OPERATION                                      |        |

|           |                                                |        |

| 3.1       | INTRODUCTION                                   |        |

| 3.2       | PANEL OPERATION                                |        |

| 3.2.1     | 857 Power Control Panel                        |        |

| 3.2.2     | Memory Address Switch Panel                    |        |

| 3.2.3     | Maintenance Panel                              |        |

| 3.2.4     | Margin Switch Panel                            | . 3-6  |

| 3.2.5     | Indicator Panel                                | . 3-8  |

| CHAPTER 4 | PRINCIPLES OF OPERATION                        |        |

| 4.1       | INTRODUCTION                                   | . 4-1  |

| 4.2       | INITIAL CONDITIONS                             |        |

| 4.3       | REQUEST/ACKNOWLEDGE                            |        |

| 4.3.1     | Single Access Request                          | . 4-2  |

| 43.2      | Simultaneous Access Requests                   |        |

# CONTENTS (Cont)

|           | F                                         | Page       |

|-----------|-------------------------------------------|------------|

| 4.4       | MEMORY CYCLE TIMING                       | 4-2        |

| 4.4.1     | Read Timing                               | 4-3        |

| 4.4.2     |                                           | 4-4        |

| 4.4.3     |                                           | 4-4        |

| 4.4.4     |                                           | 4-6        |

| 4.4.5     | Read/Modify/Write Timing                  | 4-6        |

| 4.5       |                                           | 4-6        |

| 4.5.1     |                                           | 4-6        |

| 4.5.2     | Memory Operation                          | 4-6        |

| 4.5.3     | Memory Addressing                         | L11        |

| 4.5.3.1   | Memory Bank Selection                     | L11        |

| 4.5.3.2   | Data Word Selection                       | L11        |

| 4.5.3.2.1 | Memory Address Latches and Gating Logic   | L11        |

| 4.5.3.2.2 | X and Y Line Decoding                     | L-12       |

| 4.5.3.2.3 | Drivers and Switches                      |            |

| 4.5.4     | Read/Write Current Generation and Sensing | -10<br>L17 |

| 4.5.4.1   | X and Y Current Generators                | .10        |

| 4.5.4.2   | Inhibit Driver                            | -12        |

| 4.5.4.3   | Sense Amplifier                           | -20        |

| 4.5.4.4   | Memory Data Latches                       | 20         |

| 4.5.5     | Stack Discharge Circuit                   | -20        |

| 4.5.6     | DC LO Circuit                             | -21        |

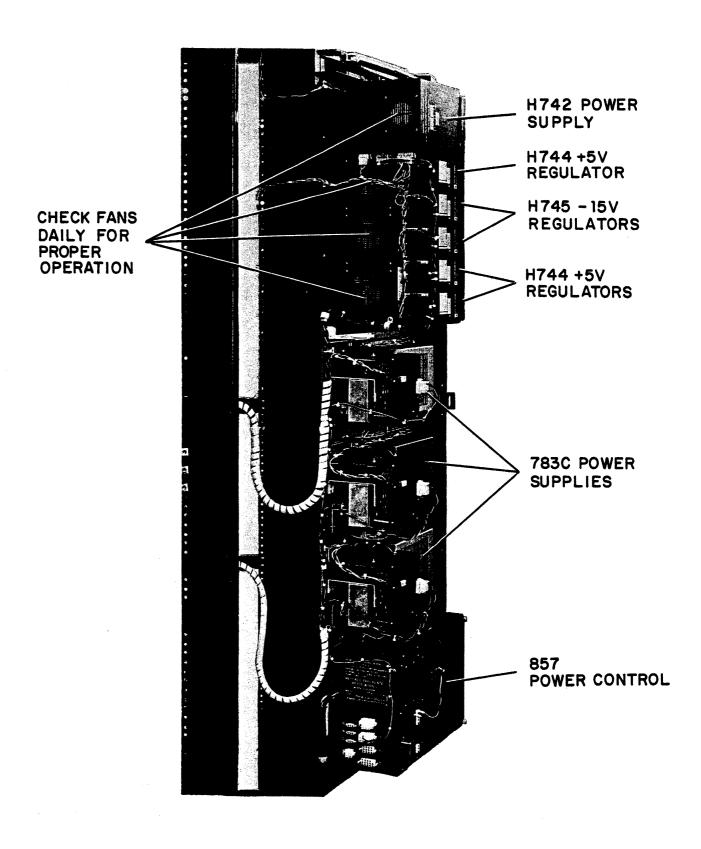

| 4.6       | POWER SYSTEM                              | -22        |

| 4.6.1     | 857 Power Control                         | -22        |

| 4.6.1.1   | System Power On                           | -23        |

| 4.6.1.2   | Normal Power On                           |            |

| 4.6.1.3   | Normal Power Off                          | -23        |

| 4.6.1.4   | Air-Flow Power Control                    | -24        |

| 4.6.1.5   | Door-Panel Power Control                  | -24        |

| 4.6.2     | AC Power Distribution                     | -24        |

| 4.6.3     | 783C Power Supplies                       | -24        |

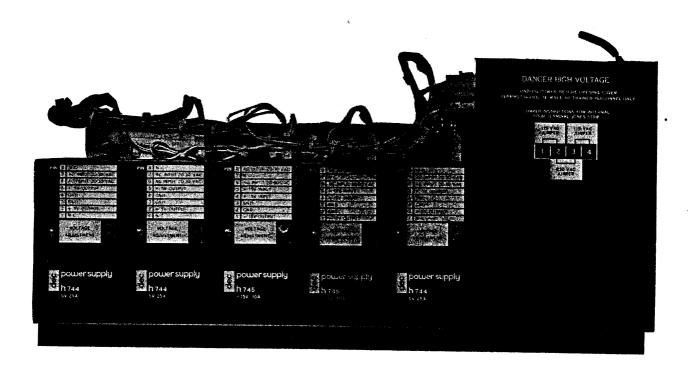

| 4.6.4     | H742A Power Supply                        | -23<br>25  |

| 4.6.4.1   | DC LO Sensing                             | -23<br>25  |

| 4.6.4.2   | +15 V Output                              | -25        |

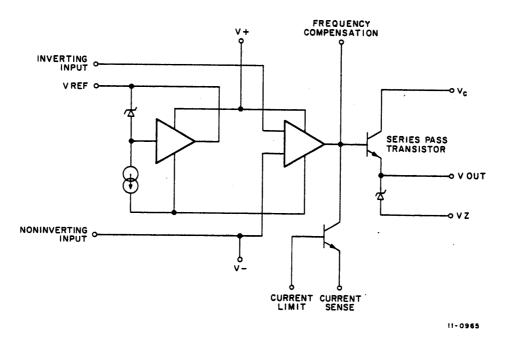

| 4.6.5     | H744 +5 V Regulators                      | -23<br>25  |

| 4.6.5.1   | Regulator Circuit                         | -23        |

| 4.6.5.2   | +5 V Overcurrent Sensing Circuit          | -20        |

| 4.6.5.3   | +5 V Overvoltage Crowbar Circuit          | -21        |

| 4.6.6     | H745 -15 V Regulators                     | -27        |

| 4.6.6.1   |                                           | -27        |

| 4.6.6.2   | -15 V Organizant Sansing Circuit          | -27        |

| 4.6.6.3   | -15 V Overcurrent Sensing Circuit         | -27        |

| T.U.U.J   | -15 V Overvoltage Crowbar Circuit         | -27        |

| CHAPTER 5 | MAINTENANCE                               |            |

| 5.1       | GENERAL INFORMATION                       | 5-1        |

| 5.2       | TOOLS AND TEST EQUIPMENT                  | 5-1        |

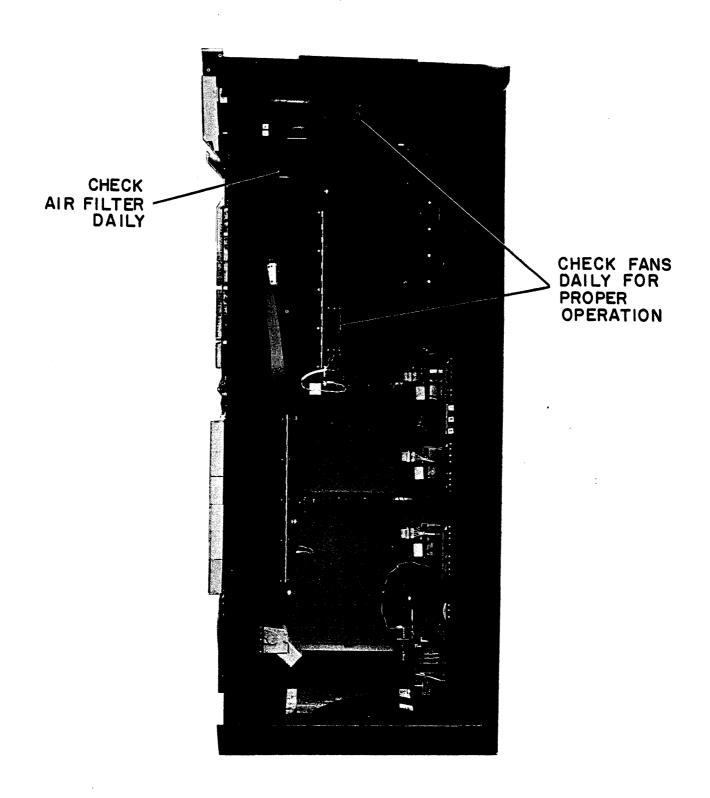

| 5.3       | PREVENTIVE MAINTENANCE                    | 5-1        |

| 5.3.1     | Daily Tasks                               | 5-1        |

# CONTENTS (Cont)

|            | Page                                                                |

|------------|---------------------------------------------------------------------|

| 5.3.2      | Monthly Tasks                                                       |

| 5.3.3      | Quarterly Tasks                                                     |

| 5.3.4      | Semiannual Tasks                                                    |

| 5.4        | CORRECTIVE MAINTENANCE                                              |

| 5.4.1      | Maintenance Practices                                               |

| 5.4.2      | Power Supply Measurements                                           |

| 5.4.3      | MF10-M Replacement and Checkout                                     |

| 5.4.4      | Margin Checks                                                       |

| 5.4.4.1    | G024 Slice Control Check Adjustment                                 |

| 5.4.4.2    | Threshold Voltage Margin Check                                      |

| 5.4.4.3    | X/Y Current Margin Check                                            |

| 5.4.4.4    | Strobe Position Margin Check                                        |

| 5.4.4.5    | +10 V and -15 V Margin Checks                                       |

| 5.4.5      | Timing Measurements and Delay Adjustments                           |

| 5.4.5.1    | PSOK (W505 Module) Adjustment                                       |

| 5.4.5.2    | MC1 AW RQ CLR (R303 Module) One-Shot Adjustments                    |

| 5.4.5.3    | MC1 WR RS TIMEOUT (R303 Module) One-Shot Adjustment 5-11            |

| 5.4.5.4    | PC1 ACT STRB (B312 Module) Delay Adjustment                         |

| 5.4.5.5    | CI INITIATE R/L (M363 Module) Delay Adjustment                      |

| 5.4.5.6    | PC3 STRB (B312 Module) Delay Adjust                                 |

| 5.4.5.7    | MC1 CYC DONE (B312 Module) Delay Adjustment                         |

| 5.5        | TROUBLESHOOTING                                                     |

| 5.5.1      | Procedural Aids                                                     |

| 5.5.1.1    | Read/Modify/Write Instruction                                       |

| 5.5.1.2    | Loading Diagnostic Into Failing Memory                              |

| 5.5.1.3    | Forcing Failure                                                     |

| 5.5.1.4    | Performing Repeat-Examine Operation With KI10 Hung                  |

| 5.5.1.5    | Checking Power-Up Sequence                                          |

| 5.5.1.6    | Interpretation of Diagnostic Error Indications                      |

| 5.5.2      | MF10 Power System Maintenance                                       |

| 5.5.2.1    | Recommended Test Bench Source                                       |

| 5.5.2.2    | Initial Tests                                                       |

| 5.5.2.3    | Output Short-Circuit Tests                                          |

| 5.5.2.4    | Testing a "Dead" Regulator                                          |

| 5.5.2.5    | Testing a Voltage Regulator After Repairs                           |

| J.J.2.J    | Tooming a volume responsion ration responsion vivia vivia vivia and |

|            | ILLUSTRATIONS                                                       |

| Figure No. | Title Page                                                          |

| 1-1        | MF10 Core Memory                                                    |

| 1-2        | System Diagram                                                      |

| 1-3        | MF10 Rear View (Access Ports)                                       |

| 1-4        | MF10 Core Memory Front View (Door Open)                             |

| 1-5        | MF10 Core Memory Rear View (Logic Sections)                         |

| 1-6        | Memory/Processor Interface                                          |

| 1-7        | Logic Subsection Interconnection Block Diagram                      |

| 2-1        | MF10 Core Memory Service Clearances                                 |

|            | ▼                                                                   |

# ILLUSTRATIONS (Cont)

|           | Pa                                                       | ige          |

|-----------|----------------------------------------------------------|--------------|

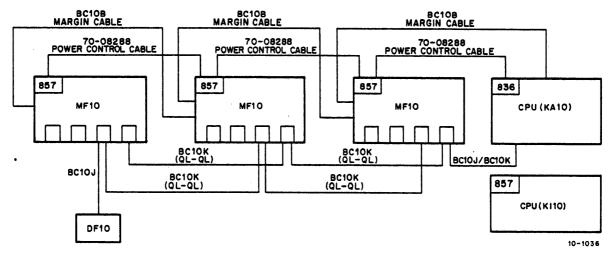

| 2-2       | MF10 Cabling                                             | 2-2          |

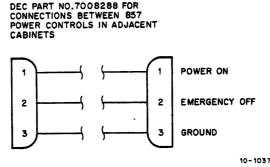

| 2-3       | Remote Power Control Cable                               | 2-3          |

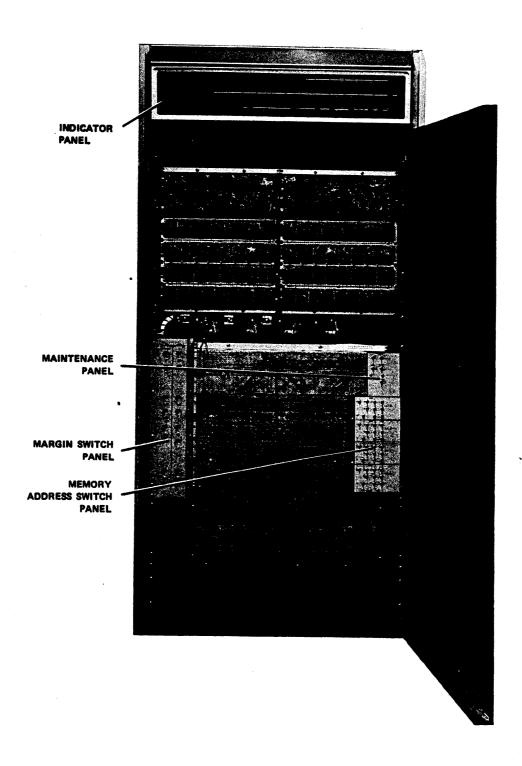

| 3-1       | MF10 Switch Panel Locations                              | 3-2          |

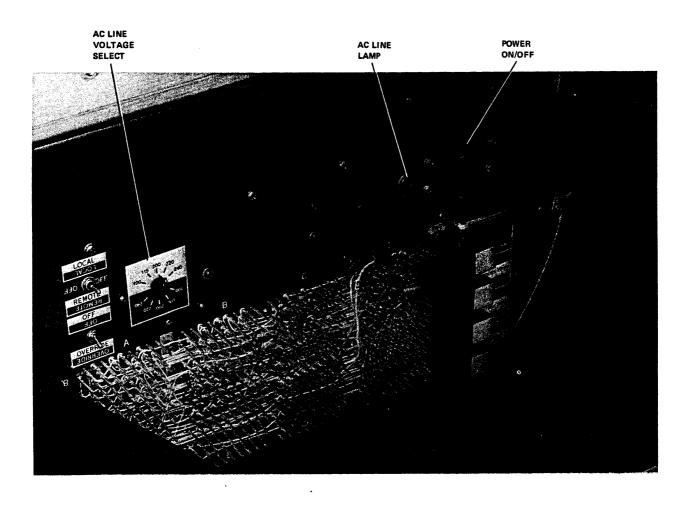

| 3-2       | 857 Power Control Panel                                  | 3-3          |

| 3-3       | Memory Address Switch Panel                              | 3-4          |

| 3-4       | Maintenance Panel                                        | 3-5          |

| 3-5       | Margin Switch Panel                                      | 3-7          |

| 3-6       | Indicator Panel                                          | 3-8          |

| 4-1       | Data Path Diagram                                        | 1-3          |

| 4-2       | Read/Restore Timing Chart                                | 1-5          |

| 4-3       | Clear/Write Timing Chart                                 | <b>1-7</b>   |

| 4-4       | Read/Modify/Write Timing Chart                           |              |

| 4-5       | Three-Wire Memory Configuration                          |              |

| 4-6       | Three-Wire 3D, 16-Word by 4-Bit Memory                   |              |

| 4-7       | Memory Address                                           | 11           |

| 4-8       | Type 8251 Decoder, Pin Designation and Truth Table       | 13           |

| 4-9       | Decoding of Read/Write Switches and Drivers Y4-Y7        |              |

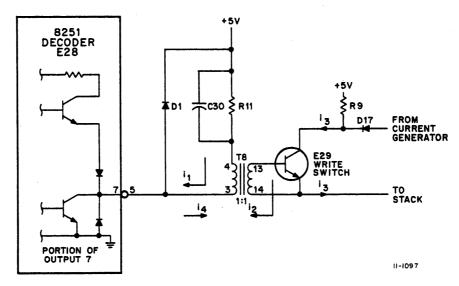

| 4-10      | Switch or Driver Base Drive Circuit                      |              |

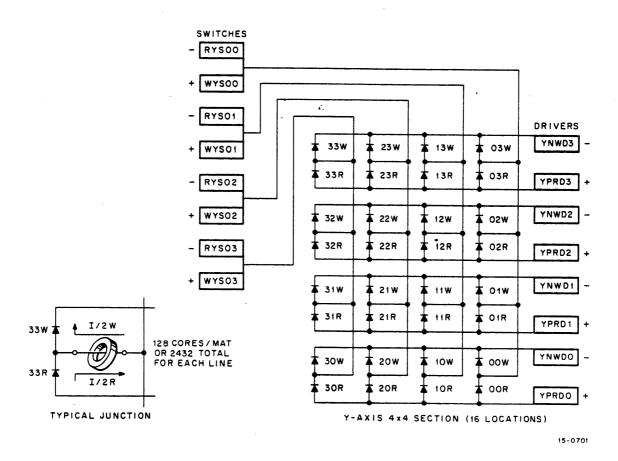

| 4-11      | Y Line Selection Stack Diode Matrix                      |              |

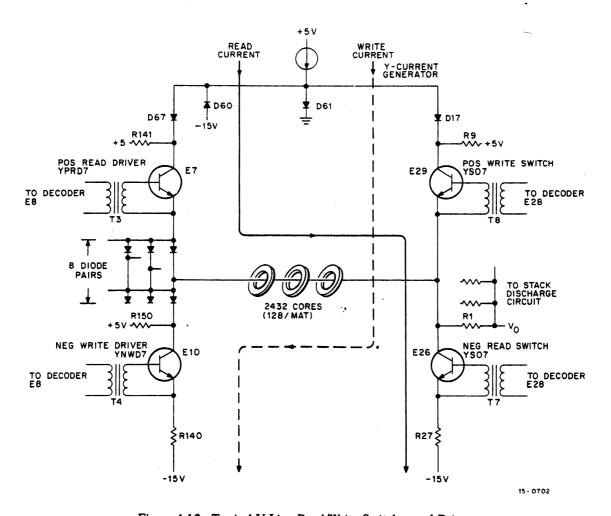

| 4-12      | Typical Y Line Read/Write Switches and Drivers           |              |

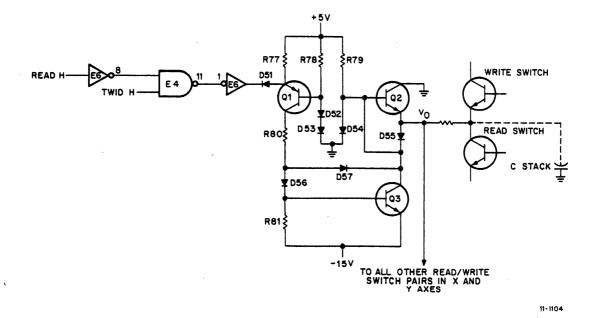

| 4-13      | Read and Write Data Path                                 |              |

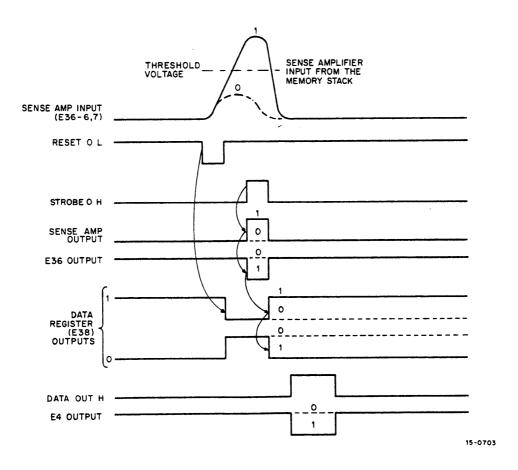

| 4-14      | Timing Diagram for the Sense Portion of a Read Operation |              |

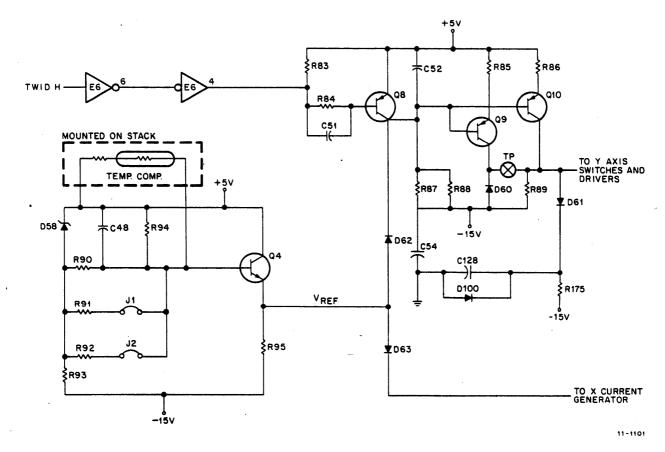

| 4-15      | Y Current Generator and Reference Voltage Supply         |              |

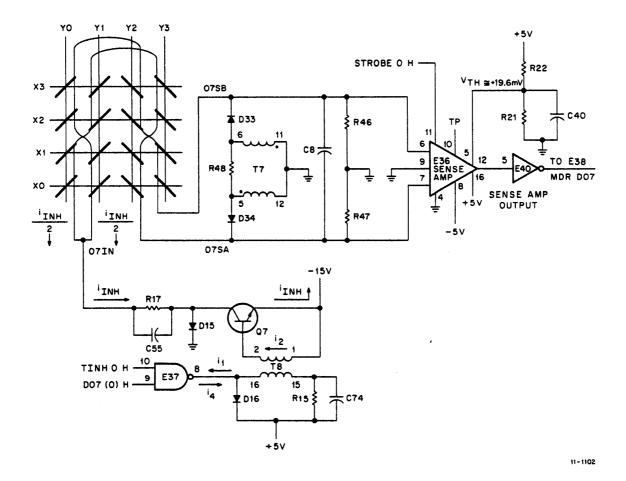

| 4-16      | Sense Amplifier and Inhibit Driver                       |              |

| 4-17      | Stack Discharge Circuit                                  |              |

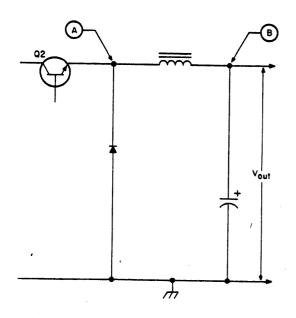

| 4-18      | Voltage Regulator E1, Simplified Diagram                 |              |

| 5-1       | MF10 Right Side View                                     |              |

| 5-2       | MF10 Power Supplies                                      |              |

| 5-3       | H744 and H745 Regulators/H742 Power Supply               |              |

| 5-4       | 783C Power Supply                                        | 5-7          |

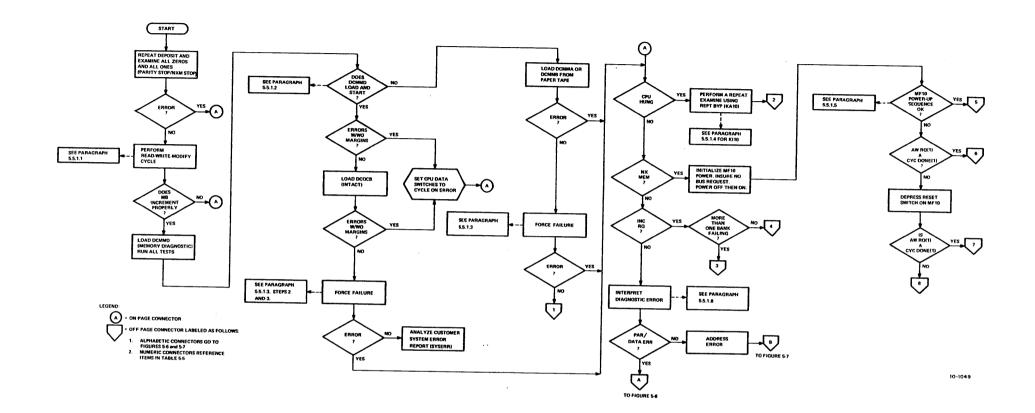

| 5-5       | CPU Hung, NX MEM, and INC RQ Troubleshooting Flowchart   |              |

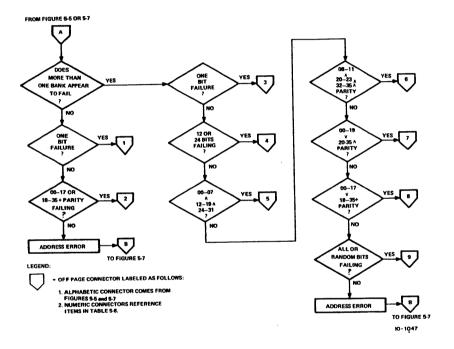

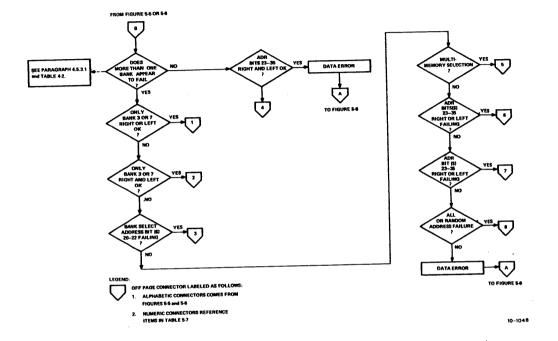

| 5-6       | Memory Parity/Data Error Troubleshooting Flowchart       |              |

| 5-7       | Addressing Error Troubleshooting Flowchart               |              |

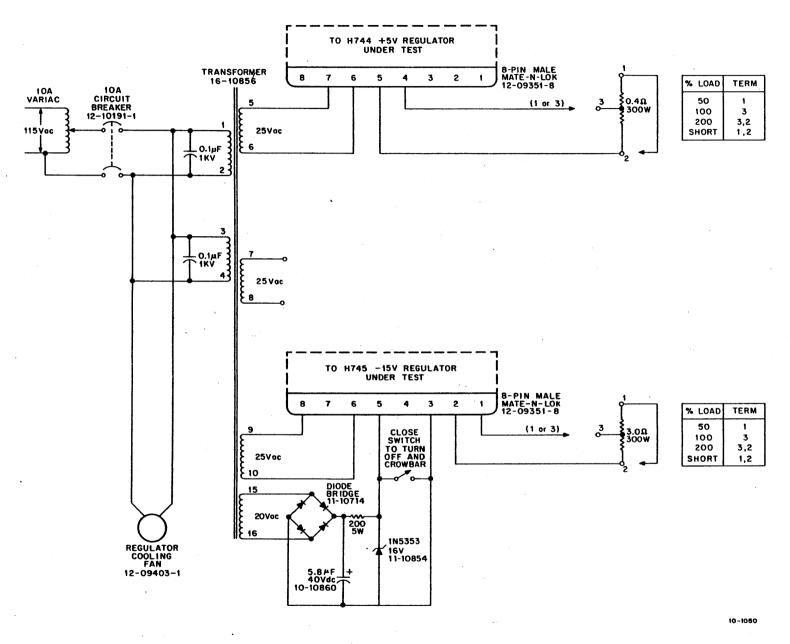

| 5-8       | Voltage Regulator Test Bench Source and Loads            |              |

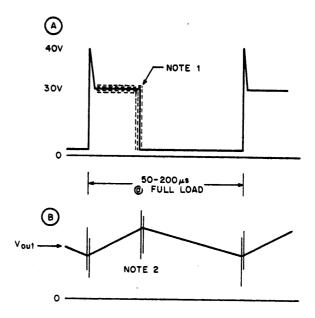

| 5-9       | Typical Voltage Regulator Output Waveforms               |              |

|           | Typion volume respective various                         |              |

|           | TABLES                                                   |              |

| Table No. | Title Pa                                                 | age          |

| -1-1      | Specifications                                           | 1-6          |

| 2-1       | <del>-</del>                                             | 2-3          |

| 2-2       | •                                                        | 2-4          |

| 2-3       | · · · · · · · · · · · · · · · · · · ·                    | 2-5          |

| 2-4       |                                                          | 2-5          |

| 3-1       |                                                          | 3-3          |

| 3-2       | ,                                                        | 3 <b>-</b> 4 |

| 3-3       |                                                          | 3-5          |

# TABLES (Cont)

|     | Pa                                                      | ge  |

|-----|---------------------------------------------------------|-----|

| 3-4 | Maintenance Panel Switches                              | 3-6 |

| 3-5 | Margin Specifications                                   | }-8 |

| 3-6 | Indicator Panel Lamp Functions                          |     |

| 4-1 | Memory Cycle Type Coding                                |     |

| 4-2 | Memory Bank Selection Decoding                          |     |

| 4-3 | Enabling Signals for Word Register Gating               |     |

| 4-4 | Memory Address to Driver/Switch Decoding                |     |

| 5-1 | Tools and Test Equipment                                |     |

| 5-2 | Diagnostic and Test Programs                            |     |

| 5-3 | Power Supply Specifications                             |     |

| 5-4 | X/Y Current and Strobe Locations                        |     |

| 5-5 | CPU Hung, NX MEM, and INC RQ, Probable Cause of Failure |     |

| 5-6 | Memory Parity Error, Probable Cause of Failure          |     |

| 5-7 | Memory Addressing Error, Probable Cause of Failure 5-   |     |

# CHAPTER 1 GENERAL INFORMATION

This chapter contains a general functional description of the MF10 Core Memory. It includes an operational overview of the logic, a physical description, and general design specifications.

#### 1.1 GENERAL DESCRIPTION

The MF10 (Figure 1-1) is a coincident current, ferrite core, 3D, 3-wire memory, storing up to 65,536 37-bit words (36 data bits plus 1 parity bit), with a cycle time of 950 ns. The MF10-A is the basic system and is capable of storing 32K word locations (32,768 actual locations). The MF10-E option is a 32K expansion unit, which, installed in a basic MF10-A, yields a 64K MF10-G. As many as 16 memory units may be physically connected to the memory bus; however, memory systems of greater than 262,144 total addressable word locations must be approved by the DECsystem-10 product line.

#### 1.2 SYSTEM DESCRIPTION

The operation of the MF10 within the PDP-10 system is asynchronous; that is, access to memory units is governed by a "request/response" system wherein the processor makes a memory cycle request and waits for a response from a memory unit. Communication between processor and memory unit takes place over the memory bus. Each processor in the system has an associated memory bus which is connected to an active port in each memory unit.

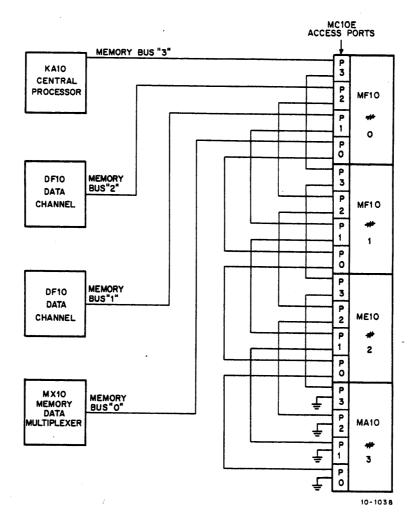

A memory unit may contain up to four MC10-F Access Ports; each port is associated with one particular processor, data channel, multiplexer, etc. (Figure 1-2). If an MX10 Memory Data Multiplexer is included in the system, as many as eight DF10 Data Channels may be associated with one memory port. Priority logic contained in each memory unit designates the sequence in which the processors are granted access in the event of simultaneous requests.

MF10s are compatible with all DECsystem-10 memories and processors. Systems containing multiples of 2 or 4 MF10s may be 2-way or 4-way interleaved, respectively, by setting the interleave switches on the memory unit switch panels. The units must, however, contain equal amounts of storage. Interleaving rotates successive memory cycles between the interleaved memory units if the addressing is sequential. Operation in this mode effectively decreases cycle time which, in turn, reduces processor idle time.

Figure 1-1 MF10 Core Memory

Figure 1-2 System Diagram

# 1.3 PHYSICAL DESCRIPTION

The MF10 is housed in a standard PDP-10 cabinet (Figure 1-1). The major physical differences in the MF10 and the earlier DECsystem-10 memories are:

- a. Higher storage capacity

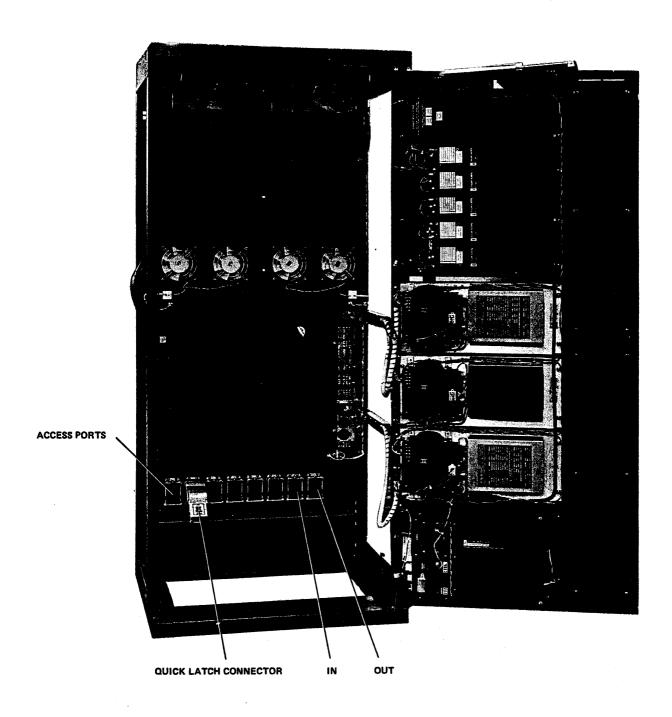

- b. Quick Latch bus connectors (Figure 1-3)

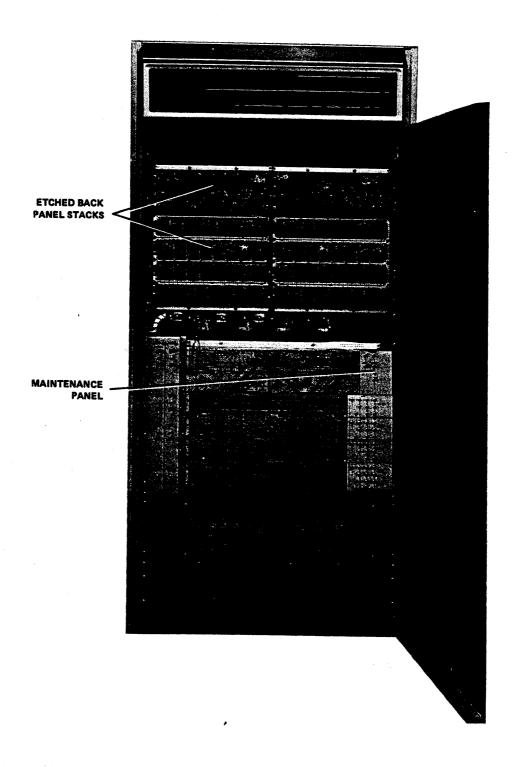

- c. Etched back panel boards (Figure 1-4)

- d. Maintenance Panel (Figure 1-4).

The Quick Latch bus connectors provide low maintenance, and fast, simple attachment of the bus cable to the four access ports (P0-P3) located at the lower rear of the logic frame. There are two physical connectors (in/out) associated with each port, which are in parallel, allowing Pn of one unit to be daisy chained to the respective Pn of the next unit. These ports are the electrical inputs from the memory bus to the MF10.

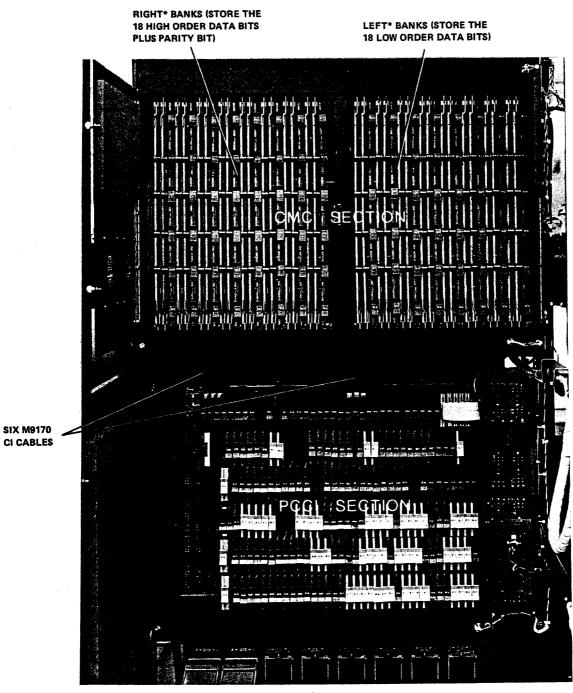

The MF10 is divided into two major logic sections: the Core Memory and Control (CMC) section, and the Port Control and Core Interface (PCCI) section. These two sections are connected by six M9170 Core Interface Cables as shown in Figure 1-5.

Figure 1-3 MF10 Rear View (Access Ports)

Figure 1-4 MF10 Core Memory Front View (Door Open)

\*RIGHT/LEFT LOOKING AT FRONT OF CABINET

Figure 1-5 MF10 Core Memory Rear View (Logic Sections)

# 1.4 SPECIFICATIONS

The MF10 Core Memory general specifications are listed in Table 1-1.

Table 1-1 Specifications

| Specifications            |                                                                                       |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Characteristic            | Specification                                                                         |  |  |  |  |  |

| Power Requirements        | 115 Vac ± 10%, 60 Hz ± 2%<br>230 Vac ± 10%, 50 Hz ± 2%                                |  |  |  |  |  |

| Line Current — 60 Hz      | 14 A                                                                                  |  |  |  |  |  |

| Line Current — 50 Hz      | 7 A                                                                                   |  |  |  |  |  |

| Power Dissipation         | 1500 W                                                                                |  |  |  |  |  |

| Internal Logic Potentials | Positive Logic: 0 V to +3 V Negative Logic: -3 V to 0 V Stack Voltage: -15 V and +5 V |  |  |  |  |  |

| Power Interrupt           | Up to 20 ms with no effect on operation. No loss of stored data at power ON/OFF.      |  |  |  |  |  |

| Cycle Time                | 950 ns                                                                                |  |  |  |  |  |

| Read Access Time          | 610 ns maximum                                                                        |  |  |  |  |  |

| Address Acknowledge Time  | 200 ns maximum                                                                        |  |  |  |  |  |

| Word Length               | 36 bits plus parity bit                                                               |  |  |  |  |  |

| Memory Size               |                                                                                       |  |  |  |  |  |

| MF10-A                    | 32,768 words                                                                          |  |  |  |  |  |

| MF10-G                    | 65,536 words                                                                          |  |  |  |  |  |

| Access Ports              | 4 maximum                                                                             |  |  |  |  |  |

| Interleaving              | 2- or 4-way                                                                           |  |  |  |  |  |

| Dimensions                |                                                                                       |  |  |  |  |  |

| Height                    | 72 in. (1.83 m)                                                                       |  |  |  |  |  |

| Width                     | 33 in. (0.84 m)                                                                       |  |  |  |  |  |

| Depth                     | 30 in. (0.76 m)                                                                       |  |  |  |  |  |

| Weight                    | 850 lb (386 kg)                                                                       |  |  |  |  |  |

| Operating Temperature     | 60° F to 95° F<br>15° C to 35° C                                                      |  |  |  |  |  |

| Storage Temperature       | 40° F to 110° F<br>5° C to 45° C                                                      |  |  |  |  |  |

| Relative Humidity         | 20% to 80%                                                                            |  |  |  |  |  |

| Heat Dissipation          | 5100 Btu/hr                                                                           |  |  |  |  |  |

#### 1.5 OPERATION OVERVIEW

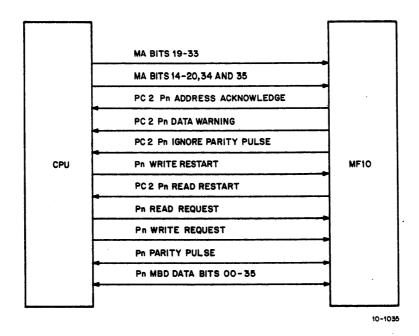

To begin operation, a processor requests access to a memory unit by placing the memory address on the memory bus along with the type of cycle requested (Figure 1-6). The cycle type is established by the Read Request (Pn MADR RD RQ) and Write Request (Pn MADR WR RQ) signals as follows:

- a. Read/Restore Cycle = Pn MADR RD RQ (1) AND Pn MADR WR RQ (0)

- b. Clear/Write Cycle = Pn MADR RD RQ (0) AND Pn MADR WR RQ (1)

- c. Read/Modify/Write Cycle = Pn MADR RD RQ (1) AND Pn MADR WR RQ (1)

Memory address bits 14-20 are decoded in the Port Address Selection (PAS) logic by ANDing them with the memory address switches. In the event of simultaneous requests, the memory port priority logic determines the highest priority port request; then, the ADR ACK (Address Acknowledge) pulse is sent to the corresponding processor, signifying acceptance of the request.

Figure 1-6 Memory/Processor Interface

# 1.5.1 Read/Restore Cycle

The read/restore cycle transfers data from a selected memory location to a requesting processor. During the read portion of this cycle, the memory reads data from the addressed memory location and loads it into the memory data latches (registers). From there the data, accompanied by a parity pulse, is placed on the bus to the requesting processor. If the parity bit is not operational, the IGN PARITY (Ignore Parity) pulse is sent to the processor. Concurrent with the IGN PARITY pulse, the RD RS (Read Restart) pulse is sent to the processor, indicating that the data requested has been sent. During the restore portion of the cycle, the memory disconnects from the bus and writes the data in the memory data latches back into the addressed memory location. This last step is necessary because the MF10 is a destructive readout memory.

## 1.5.2 Clear/Write Cycle

The clear/write cycle transfers data from a processor to a selected memory location. During the clear portion of the cycle, the memory reads data from the addressed memory location, discards it, and loads the data from the processor into the memory data latches. During the write portion of the cycle, the processor sends the parity bit and raises the WR RS (Write Restart) signal to the memory which then writes the new data and parity bit contained in the memory data latches into the addressed memory location.

# 1.5.3 Read/Modify/Write Cycle

The read/modify/write cycle transfers data from a selected memory location to a processor for modification and then transfers the modified data back to the selected memory location. During the read portion of the cycle, the memory reads the data from the addressed memory location, loads it into the memory data latches, places the data on the bus to the processor, clears the memory data latches, and pauses. While the memory pauses, the processor modifies the data (modify portion) and initiates the write portion of the cycle by placing the modified data on the bus and raising the WR RS signal. The memory then loads the modified data into the memory data latches and writes it into the same selected memory location.

#### 1.6 MAJOR LOGIC SECTIONS

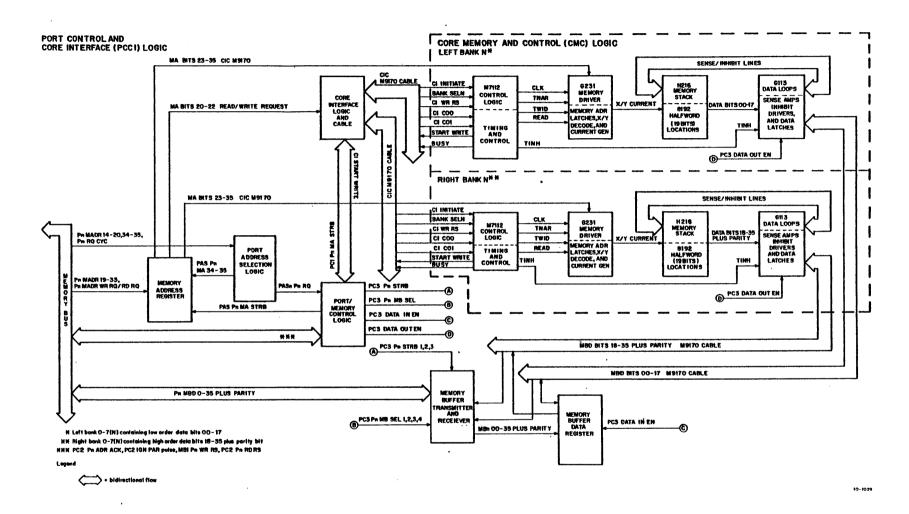

A brief description of the two major logic sections is presented in the following paragraphs. The PCCI section comprises the Request-Acknowledge and Port Priority Selection logic, as well as logic that initiates and controls the interfacing between the two sections. The CMC section comprises the core memory stack, and the addressing and timing control logic for reading and writing the data words. Figure 1-7 shows major control signals and data flow, and the logic subsection interconnections.

# 1.6.1 Port Control and Core Interface Section (PCCI)

The PCCI consists of the following logic sections and is illustrated on Engineering Drawings:

- a. Port Address Selection (PAS) consists of memory address switches and logic for selecting the proper MF10 module (unit).

- b. Port Control (PC) consists of the logic that performs the following:

- 1. port priority selection in the event of simultaneous requests

- 2. generates strobe to load the Memory Address Register

- 3. generates signals that control the entrance and exit of data and other interface signals.

- c. Memory Control (MC) consists of status logic (e.g., run, stop, cycle done, etc.) and conditioning logic (e.g., restart, error stop, start, single step, reset, clear, etc.).

- d. Memory Address (MA) contains the Memory Address Register with associated input/output gating, and the Read and Write Request flip-flops.

- e. Memory Buffer (MB) contains the Memory Data Buffer with associated input/output gating, and the data transmitters/receivers.

- f. Core Interface (CI) consists of logic levels generated for transmission to the Core Memory and Control Section over the core interface cable (CIC) for initiation and control of the read/write timing sequence. Core memory status signals are received from the CMC section over the CIC in this section.

## 1.6.2 Core Memory and Control Section (CMC)

The CMC is divided into sections or banks, each bank providing 8K, 19-bit words of memory. The banks are organized in two groups: the left banks which store the low order bits (00-17), and the right banks which store the high order bits (18-35) plus the parity bit. Thus, the left banks and the right banks combine to form a 37-bit word memory.

For addressing purposes, the banks are considered in pairs with each pair consisting of one left bank and one right bank. The MF10 may have four bank pairs or eight bank pairs, depending on the memory size desired (32K or 64K). The bank pairs of a memory are addressed as bank pairs 0 through 3 (32K) or 0 through 7 (64K). A memory address is decoded to determine the bank pair number as well as the particular word address in that bank pair. Bank pair number 0 contains the lowest 8K memory addresses, bank pair number 1 contains the next to the lowest 8K memory addresses, and so on.

Figure 1-7 Logic Subsection Interconnection Block Diagram

The MF10 shown in Figure 1-5 is a 64K unit and contains sixteen 8K, 19-bit word memory banks. Each memory bank consists of four modules:

- a. M7112 Control Logic

- b. G231 Memory Driver

- c. G113 Data loop

- d. H216 Stack.

- 1.6.2.1 M7112 Control Logic This module contains the logic which generates the timing and other signals that control addressing and reading/writing of the data.

- 1.6.2.2 G231 Memory Driver This module contains the address selection logic, switches and drivers, current generator, stack discharge circuit, and DC LO protection circuit.

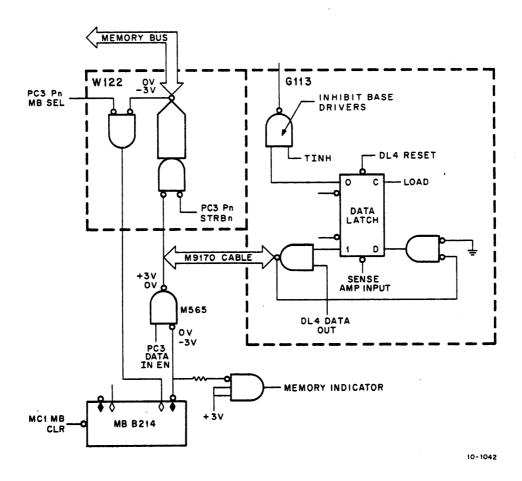

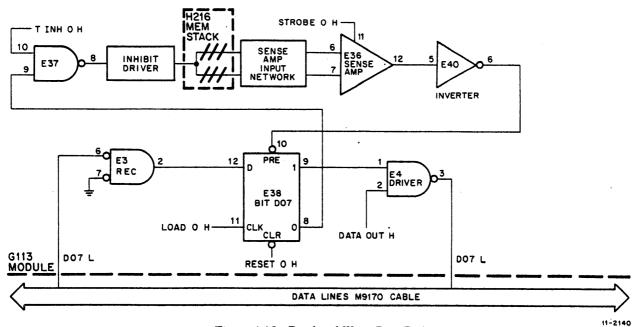

- 1.6.2.3 G113 Data Loops This module contains the sense amplifiers, inhibit drivers, data latches, strobe circuit, and -5 V supply.

- 1.6.2.4 H216 Stack This module contains the ferrite core array and the X/Y diode matrices. The core array consists of 19 mats, each wired in a  $128 \times 64$  matrix. The stack also contains the resistor-thermistor combination to control the X/Y current generator temperature compensation.

#### 1.7 INTERLEAVING

Interleaving logic allows 32K and 64K MF10 memory units to be addressed in a manner that allows consecutive memory addresses to alternate between two memories or rotate through four memories.

Only memories of the same size and having consecutive port addresses with an even port address first may be interleaved. For example, 2-way interleaving can exist between memories 0 and 1 but not between 1 and 2; 4-way interleaving can exist between memories 0, 1, 2, 3 but not between 1, 2, 3, 4.

Interleaving is accomplished by swapping port address bits with word address bits. Functionally the memory address can be divided into three segments:

|             |                   | Segments         |                   |

|-------------|-------------------|------------------|-------------------|

| Memory Size | Port Address Bits | Bank Select Bits | Word Address Bits |

| 32K         | 14 – 20           | 21, 22           | 23 – 35           |

| 64K         | 14 – 19           | 20 - 22          | 23 - 35           |

When 2-way interleaving is selected, the least significant port address bit (bit 20 for 32K and bit 19 for 64K) is swapped with the least significant word address bit (bit 35). In this configuration, should the processor generate consecutive addresses starting at address 0 of MF10 number 0, the subsequent memory cycles would alternate between MF10 memories 0 and 1, addressing only the even word locations (0, 2, 4. 6, etc.) until all the even locations were addressed, and then addressing all the odd locations (1, 3, 5, 7, etc.) until all locations were addressed. This sequence would be continuously repeated until the processor ceased generating consecutive addresses.

When 4-way interleaving is selected, the two least significant port address bits are swapped with the two least significant word address bits. In this configuration, should the processor generate consecutive addresses starting at address 0 of MF10 number 0, the subsequent memory cycles would rotate between MF10 memories 0, 1, 2, and 3, starting at address 0. Memory locations would be addressed in the following sequence at each of the four MF10 memories:

- a. 0, 4, 10, 14, 20, 24, etc.

- b. 1, 5, 11, 15, 21, 25, etc.

- c. 2, 6, 12, 16, 22, 26, etc.

- d. 3, 7, 13, 17, 23, 27, etc.

This addressing sequence would be continuously repeated until the processor ceased generating consecutive addresses.

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter, in conjunction with the PDP-10 Site Preparation Guide and the Engineering Drawings provided with each unit, contains the information required for installation of the MF10.

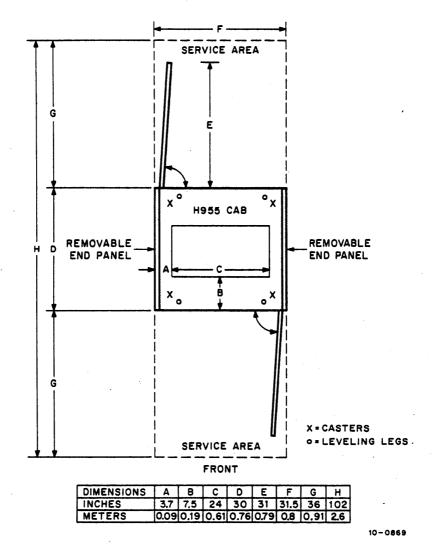

## 2.2 SITE PREPARATION

There are no special site requirements other than those dictated by environmental conditions (Table 1-1) and service clearances (Figure 2-1). Subflooring is not normally required. The units are free standing; up to four units may be bolted together. The memory unit installed closest to the CPU should not be separated from it by more than 3 feet\* or less than 1/4 inch.

#### 2.3 INSTALLATION PROCEDURE

After removing the equipment packing material, visually inspect the exterior and interior of the equipment; ensure that all modules are properly seated.

#### **CAUTION**

Check to ensure that logic pins are not shorted together before applying power to equipment.

# 2.3.1 Cabling

All cables enter or leave the memory unit through access cutouts under the bottom right and left sides. Figure 2-2 shows an example of a system configuration with cabling data.

2.3.1.1 Memory Bus — One memory bus cable is required for connection of the unit to a processor, or to another memory unit if more than one unit is included in the system. One memory bus cable is included for each MC10-F Access Port option (all access ports are optional), with a maximum of four ports per unit. The maximum allowable physical length of the memory bus is 100 feet, including wire runs through each memory unit. The memory bus must be terminated in the last memory unit in the system using one H866 type terminator per access port.

## **CAUTION**

Do not force connection when installing memory bus cable with Quick Latch cable connector.

<sup>\*</sup>Speedy, the processor timing program, is written for the standard 10 foot memory bus cable connection between the CPU and the first memory unit. If lengths in excess of 10 feet are used, Speedy timing printouts will not agree with the timing specifications.

Figure 2-1 MF10 Core Memory Service Clearances

Figure 2-2 MF10 Cabling

- 2.3.1.2 AC Power Each 60-Hz MF10 unit is furnished with a 3-wire ac power cable with the Hubbell 2611 Twist-Lok plug to be mated with a Hubbell 2610 receptacle. For 50-Hz users, a Hubbell 2321 Twist-Lok plug is mated with a Hubbell 2320 receptacle. Ensure that the power supplies are jumpered for the appropriate line voltage (115 or 230 Vac). Appropriate jumper configurations are shown on the power supply label.

- 2.3.1.3 Power Control The 857 Power Controls in all cabinets must be interconnected to enable central control of power ON/OFF from the PDP-10 console power switch.

There are three Mate-N-Lok connectors on each 857 Power Control for interconnection via a 3-wire bus (Figure 2-3). One 3-wire bus cable is supplied with each cabinet to connect the 857 Power Control to the 857 Power Control in the next cabinet. Since each power control must connect to the power controls in the preceding and following cabinets, two Mate-N-Lok connectors are reserved for the intercabinet bus. A third connector is provided for connection to the cabinet-mounted thermal switches and to the PDP-10 console power switch.

Figure 2-3 Remote Power Control Cable

Ensure that the REMOTE/LOCAL toggle switch on the 857 Power Control is in the REMOTE position before operating the MF10 on-line with the processor, if remote control is desired. Also ensure that the ac line voltage select switch on the 857 Power Control selects the proper ac line voltage level (115 Vac or 240 Vac position).

2.3.1.4 Ground Mesh Cable — Connect a No. 4 gauge wire from the copper bolt on the bottom of the MF10 cabinet to the adjacent cabinet(s).

# 2.3.2 W974 Module Size Jumpers

The W974 size jumper module (drawing D-BS-MF10-0-PAS1/2) selects the two high order address bits which are interchanged with bits 34 and 35 when interleaving. Bits 19 and 20 are used for the MF10-A, and bits 18 and 19 are used for the MF10-G. Table 2-1 shows the jumper connections for the 32K and 64K memory sizes. Ensure that the maintenance panel SIZE switch (Figure 3-4) is in the correct position (32K or 64K) for memory unit installed.

Table 2-1

W974 Module Size Jumpers

| 32K Ju     | ımpers     | 64K Ju | mpers      |

|------------|------------|--------|------------|

| From       | To         | From   | То         |

| H1         | <b>K</b> 1 | F1     | <b>K</b> 1 |

| F1         | J1         | E1     | J1         |

| H2         | K2         | F2     | K2         |

| F2         | Ј2         | E2     | J2         |

| <b>P</b> 1 | S1         | N1     | S1         |

| N1         | R1         | ' M1   | R1         |

| P2         | S2         | N2     | S2         |

| N2         | R2         | M2     | R2         |

# 2.3.3 G726-YA Module Jumpers

Ensure that the G726-YA module (drawing D-BS-MF10-0-PAS1/2) for each port is jumpered correctly for the corresponding KA10 or KI10 type memory bus used in that port.

# 2.3.4 Memory Address Switch Settings

The MF10 port address must be established prior to memory operation. The port address is established via toggle switches on the memory address switch panel. There is one switch panel for each of four memory ports and all four panels must be set to the same address. Table 2-2 lists address switch settings for a typical system having eight 32K MF10-A memories connected to one KA10 or KI10 processor memory bus.

Note that KA10 based memory systems are limited in size. If a KA10 processor is used, the number of 32K MF10 memories connected to its bus must not exceed eight. This limitation is dictated by the memory addressing capability of the KA10 (256K word locations).

Table 2-2

MF10-A (32K) Memory Address Switch Settings

|                  | MADR Swi |    |    |    | R Switch | ches* |    |      |

|------------------|----------|----|----|----|----------|-------|----|------|

| Memory Addresses | MF10 No. | 14 | 15 | 16 | 17       | 18    | 19 | 20   |

| 000000-077777    | 0        | 0  | 0  | 0  | 0        | 0     | 0  | 0    |

| 100000-177777    | 1        | 0  | 0  | 0  | 0        | 0     | n  | ۱ ĭ  |

| 200000-277777    | 2        | 0  | 0  | 0  | 0        | Ŏ     | 1  | هٔ ا |

| 300000-377777    | 3        | 0  | 0  | 0. | 0        | 0     | 1  | ľi   |

| 400000-477777    | 4        | 0  | 0  | 0  | 0        | 1     | 0  | 0    |

| 500000-577777    | 5        | 0  | 0  | 0  | 0        | 1     | 0  | ľ    |

| 600000677777     | 6        | 0  | 0  | 0  | 0        | li    | 1  | ه ا  |

| 700000-777777    | 7        | 0  | 0  | 0  | 0        | 1     | 1  | 1    |

<sup>\*</sup>If processor KA10 is used, switches 14 through 17 must be set to IGN (Ignore).

Note: If the KA10 processor is used, only eight 32K MF10-A memories can be connected to the memory bus.

MF10 memories connected to a KA10 memory bus must have consecutive addresses. For example, if only five 32K MF10-A memories are connected to a KA10 memory bus, they must be addressed 0 through 4. If this addressing procedure is not followed, holes are created in the memory address space and the KA10 will attempt to address memory that does not exist.

When 64K MF10-G memories are connected to the memory bus, the memory address switch panel toggle switches are set a little differently. Only four MF10-G memories can be connected to the KA10 processor memory bus due to the memory size limitation of the KA10. The toggle switches representing bit 18 in the 32K port address must now be set to IGN (Ignore) and toggle switches previously identified as 19 and 20 become 18 and 19. This effectively reduces the port address capability by a factor of 2 but does not affect addressing capability of the processor. Table 2-3 lists address switch settings for a typical system having four 64K MF10-G memories connected to one KA10 memory bus or eight MF10-G memories connected to one KI10 memory bus.

Table 2-3 MF10-G (64K) Memory Address Switch Settings

|                       |          | MADR Switches* |    |    |    |     |     |    |  |

|-----------------------|----------|----------------|----|----|----|-----|-----|----|--|

| Memory Addresses      | MF10 No. | 14             | 15 | 16 | 17 | IGN | 18  | 19 |  |

| 000000-177777         | 0        | 0              | 0  | 0  | 0  | IGN | 0   | 0  |  |

| 200000-377777         | 1        | 0              | 0  | 0  | 0  | IGN | . 0 | 1  |  |

| 400000-577777         | 2        | 0              | 0  | 0  | 0  | IGN | 1   | 0  |  |

| 600000 <i>-777777</i> | 3        | 0              | 0  | 0  | 0  | IGN | 1   | 1  |  |

| 1000000-1177777       | 4        | 0              | 0  | 0  | 1  | IGN | 0   | C  |  |

| 1200000-1377777       | 5        | 0              | 0  | 0  | 1  | IGN | 0   | 1  |  |

| 1400000-1577777       | 6        | 0              | 0  | 0  | 1  | IGN | 1   | 0  |  |

| 1600000-1777777       | 7        | 0              | 0  | 0  | 1  | IGN | 1   | 1  |  |

<sup>\*</sup>If processor KA10 is used, switches 14 through 17 must be set to IGN (Ignore).

If processor KA10 is used, only four 64K MF10-G memories can be connected to the memory bus.

# 2.3.5 Interleave Switch Settings

Interleaving of MF10 memories is controlled by two toggle switches located on the memory address switch panel. These switches are used to select normal (non-interleaved) operation, 2-way interleaved operation, and 4-way interleaved operation. Table 2-4 lists switch settings for the different interleaved situations.

# NOTE

Only memory units with the same number of memory locations can be interleaved; i.e., a 32K memory cannot be interleaved with a 64K memory (Paragraph 1.7).

Table 2-4 **Interleave Switch Settings**

| Mode   | MADR Switches |      |  |  |  |

|--------|---------------|------|--|--|--|

|        | 34            | 35   |  |  |  |

| Normal | NORM          | NORM |  |  |  |

| 2-way  | NORM          | INTL |  |  |  |

| 4-way  | INTL          | INTL |  |  |  |

Note: Only memory units with the

same number of word locations

can be interleaved.

# CHAPTER 3 OPERATION

#### 3.1 INTRODUCTION

The MF10 controls and indicators are grouped on five separate panels: memory address switch panel, maintenance panel, margin switch panel, indicator panel, and the 857 Power Control panel. The following paragraphs state the purpose of each panel and describe each control and indicator. Figure 3-1 shows all the panels except the 857 Power Control (Figure 3-2) which is mounted to the rear door of the cabinet.

#### 3.2 PANEL OPERATION

Generally, the panels can be described as follows:

- a. The 857 Power Control panel controls input power to the MF10.

- b. The memory address switch panels control access port operation.

- c. The maintenance panel, the margin switch panel, and the indicator panel provide fault detection, checkout, and troubleshooting controls and indicators.

## 3.2.1 857 Power Control Panel

The 857 Power Control panel (Figure 3-2) performs the following functions:

- a. adapts the MF10 to different ac line voltage inputs

- b. enables central control of power turn ON/OFF from the PDP-10 console power switch

- c. initiates power shut-down if any of the memory logic door interlocks or the air flow sense switches are activated (Paragraphs 4.6.1.4 and 4.6.1.5)

- d. enables memory logic door interlocks and air flow sense switch to be overridden for maintenance purposes

- e. provides circuit breaker protection against overloading.

Tables 3-1 and 3-2 describe the 857 Power Control panel switches and indicators.

Figure 3-1 MF10 Switch Panel Locations

Figure 3-2 857 Power Control Panel

Table 3-1

Power Control Switches

| Switch                 | Function                                                                      |  |  |

|------------------------|-------------------------------------------------------------------------------|--|--|

| LOCAL/OFF/REMOTE       | Allows power turn ON/OFF from the CPU (REMOTE) or from the MF10 unit (LOCAL). |  |  |

| OVERRIDE               | Overrides the temperature sense switches and door interlock switches.         |  |  |

| AC Line Select Voltage | This switch is set for the ac line voltage that is supplied.                  |  |  |

| Power ON/OFF           | This is the ac input line voltage circuit breaker.                            |  |  |

Table 3-2

Power Control Indicators

| Indicator     | Function                                                                                                                         |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| PWR SW ON     | Lights when ac power is applied to all power supplies in the memory unit. A flashing light means that the OVERRIDE switch is on. |  |

| DOORS OPEN    | Lights when either or both of the logic cabinet doors are open.                                                                  |  |

| CKT BRK TRP'D | Not Used.                                                                                                                        |  |

| OVERTEMP      | Lights when an overtemperature condition occurs.                                                                                 |  |

| AC Line Lamp  | Lights when ac line voltage is present.                                                                                          |  |

# 3.2.2 Memory Address Switch Panel

Each of the memory address switch panels (Figure 3-3) performs the following functions:

- a. enables or disables the access port circuitry

- b. establishes the access port address

- c. selects 32K or 64K access port operation

- d. selects interleaved or non-interleaved memory operation.

The P3 Memory Address Switch panel contains additional switches which aid in the detection and location of errors occurring in the memory control logic. Refer to Table 3-3 for a description of memory address switch panel switches.

Figure 3-3 Memory Address Switch Panel

Table 3-3

Memory Address Switch Panel

| Switch           | Function                                                                                                                                                                                                                                                            | Engineering<br>Drawing No.   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| MADR 14-20*      | Three-position toggle switches which are set to establish the address of the memory unit, allowing memory address bits 14-20 to select a particular unit (Paragraph 2.3.4).                                                                                         | MF10-0-PAS1/2                |

| SEL/DES*         | The Select/Deselect two-position toggle switch is the master port selection switch, which allows the memory port to be switched on/off-line.                                                                                                                        | MF10-0-PAS1/2                |

| INTL/NORM 34,35* | Two-position toggle switches which select 2- or 4-way interleave or normal mode operation. (See Table 2-4 for interleave switch settings.)                                                                                                                          | MF10-0-PAS1/2                |

| ERROR STOP       | When in the up position, causes the STOP indicator to light and prevents further memory cycles when a memory control logic error is detected. The STOP condition is cleared with the RESET switch.                                                                  | MF10-0-MC1                   |

| SINGLE STEP**    | When in the up position, prevents the completion of the memory cycle but allows the completion of one memory cycle each time the RESET switch is activated. (The request and acknowledge portion of the cycle is allowed, but the read/write portion is inhibited.) | MF10-0-MC1 and<br>MF10-0-CI2 |

| RESET            | Spring-loaded momentary switch which clears and initializes the memory when placed in the up position.                                                                                                                                                              | MF10-0-MC1 and<br>MF10-0-CI2 |

<sup>\*</sup>These switches are duplicated for each of the four ports and all four ports should be set to the same address.

# 3.2.3 Maintenance Panel

The maintenance panel (Figure 3-4) assists in maintaining the MF10. The only switch on the panel which does not perform a maintenance function is the SIZE switch. Refer to Table 3-4 for maintenance panel switch description. The circuitry for each switch is shown on the engineering drawing listed to the right of the switch description.

Figure 3-4 Maintenance Panel

<sup>\*\*</sup>All 0s are written into memory when SINGLE STEP is used on a clear/write cycle.

Table 3-4

Maintenance Panel Switches

| Switch                      | Function                                                                                                                                                                                                                       | Engineering<br>Drawing No. |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| SIZE*                       | Three-position switch which enables the memory unit to decode the memory address to select the proper banks for 32K or 64K word locations.                                                                                     | MF10-0-CI1                 |

| MEM SEG<br>(Memory Segment) | Two-position switch which enables the lower 32K (banks 0-3) of a 64K memory unit to be interchanged with the upper 32K (banks 4-7).                                                                                            | MF10-0-CI1                 |

| STROBE POSITION             | Three-position switch which varies sense amplifier STROBE by ±15 ns to check for marginal CMC conditions.                                                                                                                      |                            |

| THRESHOLD VOLTAGE           | Two-position switch which allows sense amplifier threshold amplitude to be varied from +4 V to +6 V via the margin check vernier on the CPU maintenance panel, with the MARGIN CHECK selection switch in the +10 L/R position. | MF10-0-C12                 |

|                             | The THRESHOLD switch, located on the margin switch panel, must be in the VAR (variable) position to permit threshold amplitude variation.                                                                                      |                            |

|                             | The NORM position of the THRESHOLD VOLTAGE switch applies a fixed +5 V to the sense amplifiers.                                                                                                                                |                            |

| X/Y CURRENT                 | This two-position switch increases or decreases $X/Y$ core selection currents by $\pm 5\%$ of 440 mA to check for marginal CMC conditions.                                                                                     | MF10-0-CI2                 |

<sup>\*</sup>A switch position is provided for 128K size selection for future systems.

# 3.2.4 Margin Switch Panel

The margin switch panel (Figure 3-5) also assists in the maintenance of the MF10. The panel is used to perform monthly preventive maintenance checks to locate marginal operational modules; i.e., modules that are deteriorating (due to age or other factors) and will probably fail in the near future. The panel may also be used to cause intermittent failures to become constant, and thereby facilitate troubleshooting.

The margin switches (H-N) are used to perform marginal operation checks on logic module rows in the PCCI logic section. By placing the margin switches in the VAR (variable) position, the fixed voltages (+10 V and -15 V) normally applied to the modules are replaced by variable voltage via the margin cables. These variable voltages are controlled by the margin check vernier located on the CPU. The module must operate without errors in the voltage range specified in Table 3-5 to pass the maintenance check.

The THRESHOLD switch is used in conjunction with the maintenance panel THRESHOLD VOLTAGE switch (Table 3-4) to provide a variable threshold voltage (+4 V to +6 V) to the sense amplifiers. Placing the THRESHOLD switch in the VAR position applies +10 V  $\pm$  7.5 V to the G024 Slice Control module (drawing D-BS-MF10-0-CI2) via the margin cable. This voltage is variable via the CPU margin check vernier. The slice control module is adjusted for +5 V output with a +10 V input. The input voltage may then be varied from +2.5 V to +17.5 V to provide the +4 V to +6 V output.

Figure 3-5 Margin Switch Panel

Table 3-5

Margin Specifications

| Row        | +10 V Margins               | -15 V Margins  |

|------------|-----------------------------|----------------|

| Н          | Threshold +2.5 V to +17.5 V | -12 V to -18 V |

| J          | +2.5 V to +17.5 V           | -12 V to -18 V |

| . <b>K</b> | +2.5 V to +17.5 V           | -12 V to -18 V |

| L          | +6.0 V to +17.5 V           | -12 V to -18 V |

| M          | +5.0 V to +16.0 V           | -12 V to -18 V |

| N          | +6.0 V to +16.0 V           | -12 V to -18 V |

# 3.2.5 Indicator Panel

The indicator panel (Figure 3-6) provides memory operation status indicators to aid in the maintenance of the MF10. Visual displays indicate memory operation and the contents of the Address and Buffer Registers. When an operation indicator lights, the function identified is active or true; when a register indicator lights, the particular bit position identified contains a binary 1. The register indicators (Table 3-6) are grouped in octal format to facilitate translation of the binary word segments.

Figure 3-6 Indicator Panel

Table 3-6

Indicator Panel Lamp Functions

| Indicator                           | Function                                                                                                                      |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| MEMORY ADDRESS 19-35                | Indicates the contents of the Memory Address Register.                                                                        |

| MEMORY BUFFER 0-35 and PAR (parity) | Indicates the contents of the Memory Buffer Register.                                                                         |

| PSOK                                | Indicates power is applied to the unit, and regulated voltages are within tolerances.                                         |

| REQUESTS<br>AW                      | Indicates memory unit is awaiting a processor request for access.                                                             |

| RD                                  | Indicates a read request is being processed, or was the last memory cycle processed.                                          |

| WR                                  | Indicates a write request is being processed, or was the last memory cycle processed.                                         |

| P0-P3                               | Indicates which processor port(s) is requesting access.                                                                       |

| ACTIVE PO-P3                        | Indicates which port request is being processed.                                                                              |

| LAST P2-P3                          | Indicates which port (considering only P2 and P3) was last granted access.                                                    |

| ENABLES<br>MB SEL                   | Indicates the active port memory bus receivers are enabled to receive data from the processor.                                |

| DATA IN                             | Indicates the data transfer from the Memory Buffer to the data latches is enabled.                                            |

| DATA OUT                            | Indicates the bus DR (drivers on G113 module) are enabled to transmit the data from the data latches to the bus transmitters. |

| INC RQ                              | Indicates the write operation failed to start in a time frame of 20 $\mu$ s from the start of the memory cycle.               |

| RUN                                 | The memory unit is performing a memory cycle.                                                                                 |

| STOP                                | Indicates the detection of an error while in the error stop mode.                                                             |

| WR RS                               | Indicates the Write Restart signal was received from the processor.                                                           |

| CYC DONE                            | Indicates the completion of the memory cycle.                                                                                 |

# CHAPTER 4 PRINCIPLES OF OPERATION

# 4.1 INTRODUCTION

A block diagram of the MF10 is shown in Figure 1-7, and circuit and timing diagrams are interspersed throughout the chapter. Engineering drawings are also referenced where applicable.

Note that the mnemonic prefix portion of signal names shown on the illustrations indicate the signal source. For example, the MC1 CYC DONE (1) signal is generated by the Memory Control 1 logic, drawing D-BS-MF10-0-MC1.

#### 4.2 INITIAL CONDITIONS

Applying power to the MF10 initializes the system and places it in the idle state, ready to respond to access requests from a processor (refer to drawing D-FD-MF10-0-PDF for a flow diagram of the power up/down and initialize sequences). When power is applied, the CI PSOK signal is asserted, which enables the memory buffers and a 200 ms one-shot multivibrator. Approximately 200 ms later, MC1 START is asserted, which clears the MC1 STOP and PC1 INC RQ flip-flops and generates MC1 RESET. MC1 RESET generates MC1 STATE CLR and CI INITIALIZE. The MC1 STATE CLR signal clears the Port Address Select, Port Control, and Memory Control flip-flops; CI INITIALIZE clears the M7112 Control Logic flip-flops. Approximately 140 ns later, the MC1 STOP flip-flop is examined. If it remains cleared (indicating conditions are go), PC1 SET CYC DONE is asserted; this sets the PC1 AW RQ (Port Control 1 Await Request) flip-flops, and after a variable delay, sets the MC1 CYC DONE flip-flop. The memory is now ready to accept access requests.

# 4.3 REQUEST/ACKNOWLEDGE

Basic request/acknowledge circuitry must be capable of recognizing an access request from a processor and acknowledging that request when the memory is free to service it. However, the MF10 request/acknowledge circuitry is required to perform tasks in addition to the basic request/acknowledge tasks. Because the MF10 is required to service four separate processors on a timesharing basis, the request/acknowledge circuitry must include a priority network to handle simultaneous access requests. In the event two or more simultaneous requests occur, the priority network allows access to the processor having highest priority. The Request and Port Flow Diagram (drawing D-FD-MF10-0-RPP) illustrates the priority scheme and the sequential operation of the request/acknowledge circuitry. The following paragraphs explain the request/acknowledge sequence with reference to the flow diagram.

# 4.3.1 Single Access Request

Assuming the memory is in the idle state as explained in Paragraph 4.2, the sequence is initiated when a processor generates a memory address which matches the address of the port to which it is connected. (The port address is established by the memory address switch panel toggle switches.) When this happens, one of the Pn RQ CYC signals goes true and is ANDed with the PC1 AW RQ (1) to set a PAS (Port Address Select) flip-flop. The PAS flip-flop output is ANDed with MC1 CYC DONE (1) to reset the PC1 AW REQ flip-flop and generate the PC1 MA CLR (Port Core 1 Memory Address Clear) pulse. As long as the PC1 AW RQ flip-flop is reset, subsequent processor requests are ignored. The PC1 MA CLR pulse clears the Memory Address and Memory Buffer Registers and the CI WR RS DISPLAY (Core Interface Write Restart Display) flip-flop. The registers are now ready to receive the current memory address and data. After a time delay of 60 ns, PC1 ACT STRB (Port Control 1 Acknowledge Strobe) clears the MC1 CYC DONE flip-flop and is ANDed with the PAS flip-flop outputs (PC1 Pn RQ) in the priority network to generate the Port 0, 1, 2, or 3 Memory Address Strobe (PC1 Pn MA STRB) which loads the address into the Memory Address Register and initiates the memory operation. The priority network also sets the proper Port Acknowledge flip-flop (PC1 Pn ACT). The Port Acknowledge flip-flop output is used to generate the Port Control 2 Port 0, 1, 2, or 3 Address Acknowledge Signal (PC2 Pn ADR ACK) which notifies the processor that its request is granted.

# **NOTE**

The G726-YA Address Acknowledge, Data Warning, and Request Cycle jumper module configurations are determined by the relative speeds of the memories on the bus. Refer to Paragraph 6.5 (Memory Control) in the KI10 Central Processor Maintenance Manual for an explanation of memory cycle overlapping.

Finally, 60 ns later, the PC1 LAST STRB is ANDed with PC1 P2 ACT (1) or PC1 P3 ACT (1) (if either is true) to set or reset the PC1 P2/P3 LAST flip-flop, thus completing the request/acknowledge sequence. The P2/P3 LAST flip-flop determines which port has third priority (P2 or P3) during subsequent memory cycles.

# 4.3.2 Simultaneous Access Requests

Simultaneous access requests dictate the need for a priority scheme. If two or more requests are received by the MF10 simultaneously, the priority network enables the port having the highest priority. The priority scheme is as defined by the logic expressions on the flow diagram:

| Priority | Port               |  |

|----------|--------------------|--|

| First    | PO                 |  |

| Second   | P1                 |  |

| Third    | P2 and P3 (shared) |  |

Third priority is shared between ports P2 and P3 such that if P2 were serviced last in the previous memory cycles, then P3 would be given priority over P2 should simultaneous requests occur on those ports.

# 4.4 MEMORY CYCLE TIMING

As previously stated (Paragraph 1.5), data may be read from memory and sent to a processor (read/restore cycle); data may be transferred from a processor and written into memory (clear/write cycle); or data may be read from memory, sent to a processor, modified by the processor, returned to the memory and written into the memory at the same location from which it was originally read (read/modify/write). The following paragraphs discuss memory cycle timing.

The basic operations of memory cycle timing, the read operation and the write operation, are common to the three memory cycles. Figure 4-1 illustrates the data path of information written into and read from memory (drawing D-FD-MF10-0-MCF). Note that times stated in the following paragraphs are approximate.

Figure 4-1 Data Path Diagram

# 4.4.1 Read Timing

Read timing begins when CI INITIATE is true, 60 ns after PC1 Pn MA STRB (drawings D-FD-MF10-0-MCF and D-CS-M7112-0-1). The M7112 Control Logic module associated with the selected memory bank (Paragraph 4.5.3.1) generates the read timing sequence for that specific bank.

CI INITIATE, CI BANK SELECT nR/L, CIC DC LO, and MEM BUSY (0) L are ANDed to generate RESET, which clears the data latches, sets the Read and Delay flip-flops, generates CLK (Clock Pulse) to load the memory address into the memory address latches, and initiates the DL1 multi-tapped delay line timing by sending a high-to-low transition down the delay line. CLK also loads the C00 and C01 flip-flops which determines the type of memory cycle to be performed (Table 4-1). The high DL1, pin 8 output, ANDed with DELAY (1) H, latches the DL1, pin 8 output back to the DL1, pin 1 input, holding the input low for a total of 195 ns. DL1, pin 2 goes low 25 ns after the input, initiating the generation of TNAR (Time Narrow) and TWID (Time Wide). These timing signals cause the proper read drivers/switches and current generators to turn on. Also, TNAR sets the MEM BUSY flip-flop which prevents the regeneration of CLK during the cycle, locks out further requests while the current cycle is in progress, and enables an AND gate which generates BUSY (Busy is the same as CIC BUSY L/R). Pin 6 of DL1 remains low for 125 ns after the input pin 1 goes high; this extends TNAR to 290 ns. In the same manner, pin 8 of DL1 remains low for 175 ns after input pin 1 goes high, extending TWID to 340 ns. Also, DL1, pin 8 going low clears the Delay flip-flop, which prevents DL1 pin 1 from going low when the 175 ns tap times out.

Table 4-1

Memory Cycle Type Coding

| Memory Cycle Type | State of C00 | State of C01 |

|-------------------|--------------|--------------|

| Read/Restore      | 0            | 0            |

| Clear/Write       | 0            | 1            |

| Read/Modify/Write | 1            | 0            |

The data is sensed during TWID/TNAR times and strobed into the data latches at strobe time. (The exception is during a clear/write cycle. Strobe Enable is not generated because C01 (0) H is false, disabling the STRB EN AND gate. The data will not be strobed from the sense amplifiers.) TNAR is delayed 35 ns and ANDed with STRB EN to trigger the 74121 Monostable Multivibrator (drawing D-CS-G113-0-1) and a negative-going pulse is generated on pin 1. The trailing edge of the pulse occurs approximately 300 ns after CI INITIATE. When the trailing edge occurs, the DL4 STROBE AND gates (E11) are enabled for 30 ns, thus generating the 30 ns DL4 STROBE 1 H/0 H. STROBE 1 H/0 H samples the amplified core output and causes the corresponding Data Latch flip-flop to be set. PC3 DATA OUT EN (1) H becomes true 200 ns after CI INITIATE to enable the bus drivers (BUS DRS) on the G113 board. Each bus driver activates immediately with a 1 bit in the respective data latch, allowing the data to pass from the memory bank, through the core interface cable to the memory bus transmitters. TWID going low is inverted to clock the Read flip-flop to the 0 state (the data input pin 12 is tied to ground), ending the read portion of the cycle.

PC3 STRB (L) becomes true 315 ns after CI INITIATE to set PC3 MB SEL. PC3 STRB is ANDed with PC1 Pn ACT (1) to generate PC3 Pn STRB 1, 2, 3, which strobes the proper port to send the data to the processor. Also, PC3 MB SEL (1) L is ANDed with PC1 Pn ACT (1) to generate PC3 Pn MB SEL 1, 2, 3, 4, which gates the proper memory bus data transmitter output into the Memory Buffer to display the contents on the indicator panel.

# 4.4.2 Write Timing

A read operation is always performed before a write operation. At the end of a read operation, READ (1) H becomes false to AND with WR STRB (1) L (if a clear/write or a read/modify/write is being performed), or READ/RESTORE CYCLE (if a read/restore is being performed). The WR STRB flip-flop is set by the WR RS signal generated by the processor to initiate the write portion of a clear/write or clear/modify/write memory cycle. The output of the AND gate clocks the DELAY flip-flop to the 1 state [the data input pin 2 is tied to DELAY(1) L] and causes the generation of START WRITE (START WRITE is the same as CIC START OF WRITE L/R). DELAY (1) H, becoming true, is ANDed with the DL1 output pin 8, which is high, to restart the DL1 timing. TNAR and TWID are generated in the same manner as in a read operation. TWID, RESET (L) inverted, and READ (0) H (READ=WRITE) are ANDed to generate TINH (L), allowing the proper inhibit drivers to operate.

In the CI logic, CIC START OF WRITE goes low and is ANDed with CIC BUSY L/R to complete the CI START OF WRITE input gating. This pulse causes the generation of MC1 STATE CLR which sets PC1 AW RQ after a delay of 140 ns. The MF10 may now accept the next request.

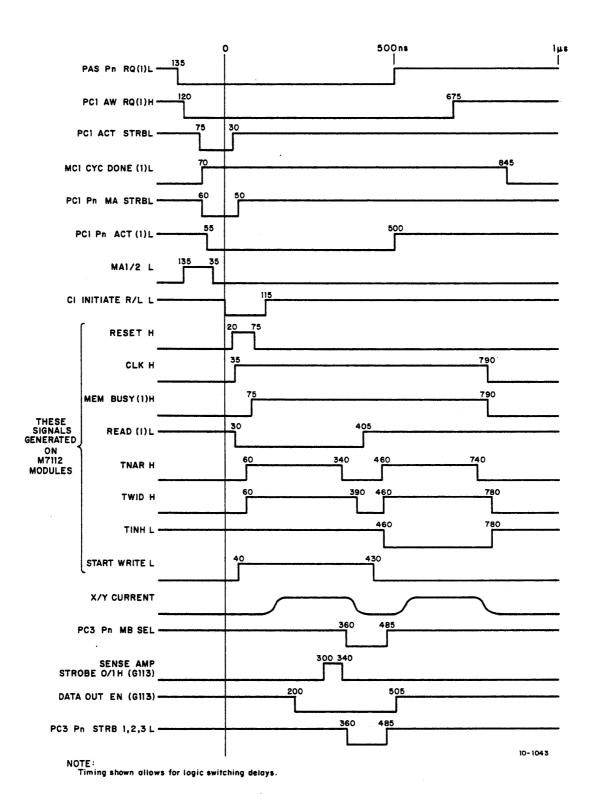

## 4.4.3 Read/Restore Cycle Timing

During a read/restore cycle (Figure 4-2), the data sensed from the cores are strobed into the data latches and gated by DL4 DATA OUT to the memory bus transmitters. PC3 Pn STRBn enables the data to be transmitted through the proper port to the processor. At the same time, the PC3 Pn MB SELn transfers the data into the Memory Buffer for display. The data still retained in the data latches is then rewritten into the same memory location.

Figure 4-2 Read/Restore Timing Chart

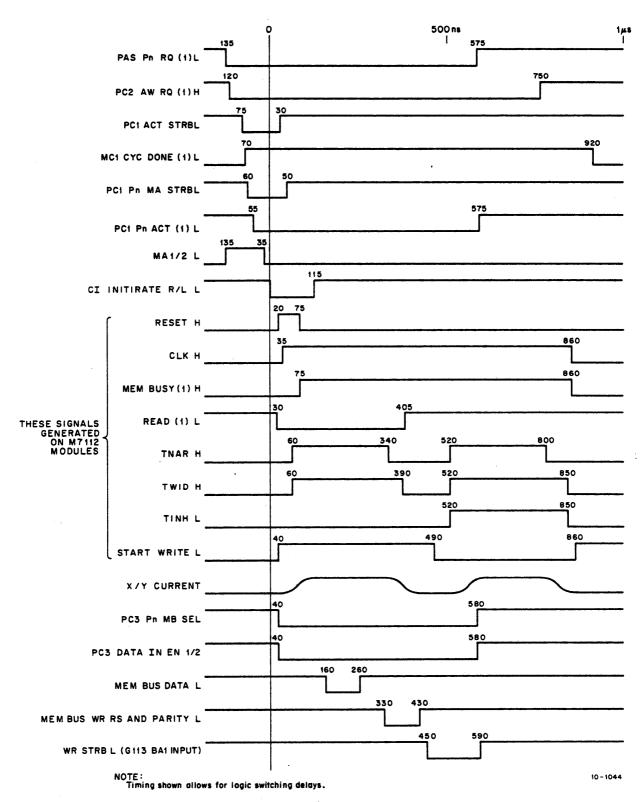

# 4.4.4 Clear/Write Timing

During a clear/write cycle (Figure 4-3), a read operation is first performed; however, the data is lost because CO1 (0) is false disabling the STRB EN gate and the data is not strobed from the sense amplifiers. CI INITIATE ANDED with MA2 RD RQ (0) sets PC3 DATA IN EN and PC3 MB SEL. PC3 Pn MB SELn enables the Memory Buffer receivers for the proper ports to receive the data from the processor.

The data is received from the processor (along with WR RS) and loaded into the Memory Buffer for display on the indicator panel. PC3 DATA IN EN allows the data to be transferred from the Memory Buffer through the M9170 Core Interface Cables to the data latches in the CMC section. CI WR RS causes WR STRB to start the write operation, and generates DL4 LOAD 0 H/1 H to clock the data into the latches. The data word is then written into the addressed memory location.

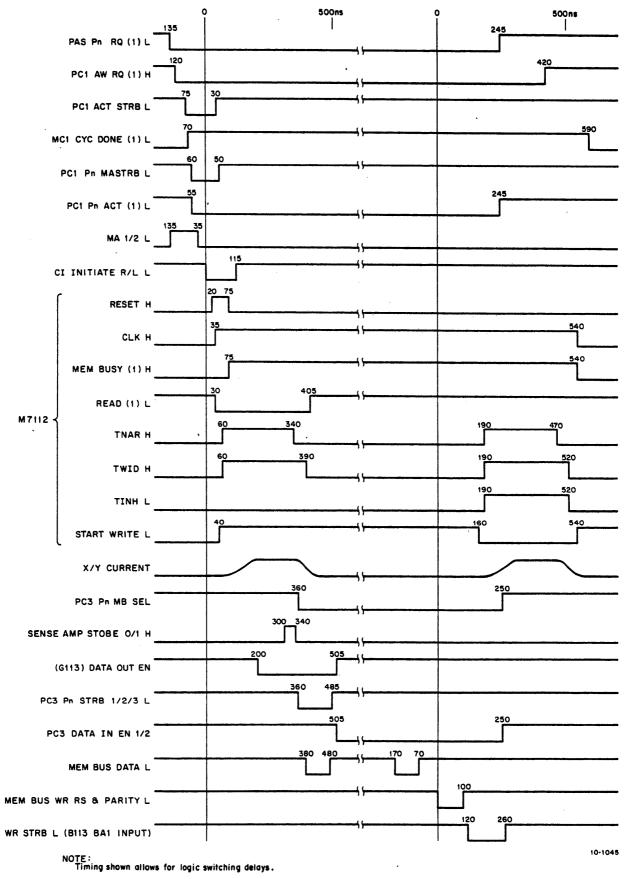

# 4.4.5 Read/Modify/Write Timing

During a read/modify/write cycle (Figure 4-4), the read operation is first performed. The data read is then sent to the processor for modification and the Memory Buffer is cleared. The memory then pauses (20  $\mu$ s maximum) to await the return of the modified data.

During the read operation, PC3 STRB sets PC3 MB SEL (remains set until MC1 STATE CLR), and the AND of MA2 WR RQ (1) and PC3 DATA OUT EN CLR sets PC3 DATA IN EN (also remains set until MC1 STATE CLR). When the modified data is sent from the processor along with WR RS, a write operation is performed as in a clear/write cycle.

# 4.5 DETAILED MEMORY DESCRIPTION

#### 4.5.1 Core Array

The 8K, ferrite core, memory module consists of 19 memory mats arranged in a planar configuration. Each mat contains 8192 ferrite cores arranged in a 128 × 64 array. Each mat represents a single bit position of a word. This planar configuration provides a total of 8192 19-bit half-word locations. Each ferrite core can assume a stable magnetic state corresponding to either a binary 1 or binary 0. When power is removed from the core, the core retains its state until changed by appropriate control signals. The outside diameter of each core is 18 mil; the inside diameter is approximately 11 mil. Each core is 4.5 mil thick.

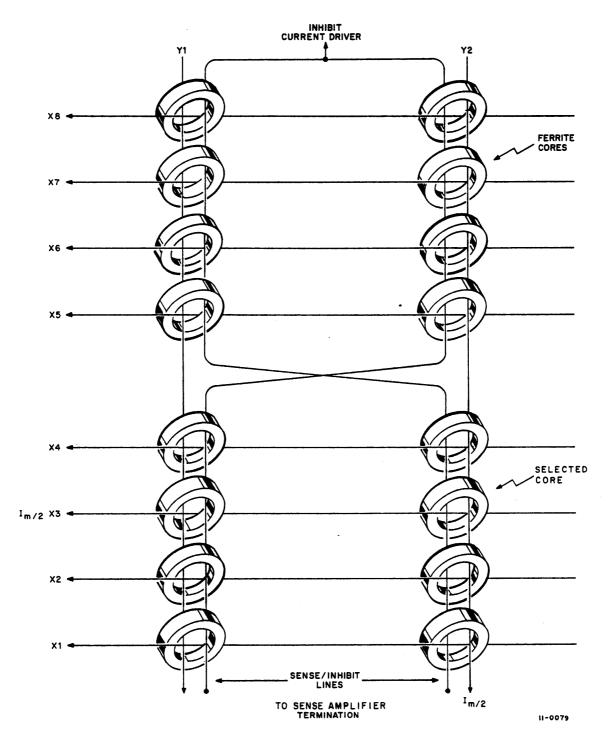

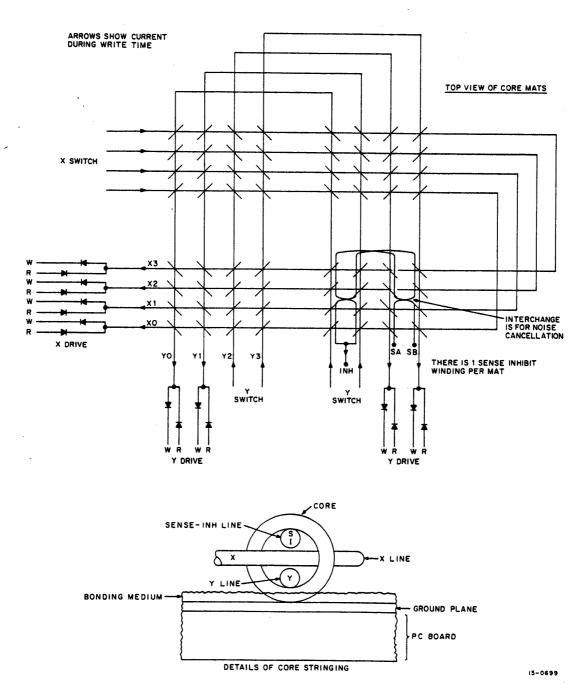

The memory uses a 3-wire core selection technique (Figure 4-5). An X axis read/write line passes through all cores in each horizontal row for all 19 mats. A Y axis read/write line passes through all cores in each vertical row for all 19 mats. Through the use of selection circuits, which control the current applied to a specific X-Y line, any one of the 8192 word locations can be addressed for writing data into memory or reading data out of memory. A third line passes through each core on a mat to provide the sense inhibit functions. There is one sense inhibit line per mat. This single sense inhibit line, as well as the selection circuits, are discussed in subsequent paragraphs.

# 4.5.2 Memory Operation

The H216 Memory Stack is a standard 3D, 3-wire, coincident current, core array (Figure 4-5). The current passing through any one line (X or Y) is one-half that required to change the magnetic state of the core. X1 and Y1 intersect once on each of the 19 mats, thereby producing full current at 19 cores. If the cores are being read, the current direction is such that the 19 cores are forced to the 0 magnetic state (destructive readout); the other 8191 cores on each mat are not affected. When an addressed core containing a 1 is switched to the 0 magnetic state, the resultant flux change is detected by the sense/inhibit line and a logical 1 is generated at the output of the sense amplifier on the G113 module.

Figure 4-3 Clear/Write Timing Chart

Figure 4-4 Read/Modify/Write Timing Chart

Figure 4-5 Three-Wire Memory Configuration

The memory is accessed in a similar fashion during a write operation except that the current through the X and Y lines is in the opposite direction. All 19 cores are switched to the 1 magnetic state except on those cores having current applied to their sense/inhibit line. This current cancels out the affect of the half-current in the Y line (inhibit current is in the opposite direction of Y write current) and the addressed core remains in the 0 state. For example, when a write operation is performed to complete a read/restore cycle, only those cores containing 1s originally will be forced to the 1 state. All cores containing 0s originally will have current applied to their sense/inhibit line during the restore portion of the cycle. Figure 4-6 shows a 16-word by 4-bit planar memory. The 8K H216 Memory Stack is configured in the same manner, except that it has 128 X lines, 64 Y lines, and 19 core mats. The core stringing is identical, and each of the 19 sense lines are laced through 8192 cores with the interchange between X63 and X64 instead of between X1 and X2.

Figure 4-6 Three-Wire 3D, 16-Word by 4-Bit Memory

# 4.5.3 Memory Addressing

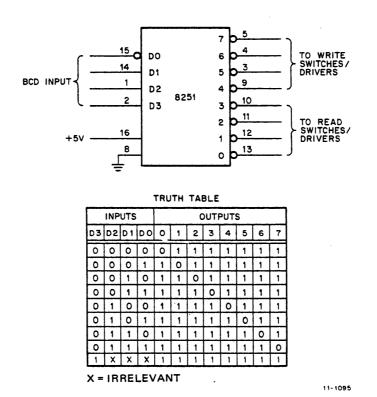

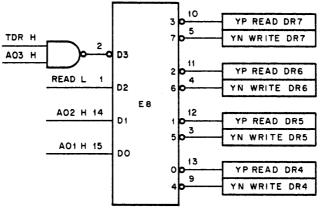

The memory locations of the MF10 are addressed by bits 20-35 of the memory address (Figure 4-7) generated by the processor. These bits are capable of addressing 64K (65,536) locations. One H216 Memory Stack module contains 8K (8192) half-word locations (19 bits). For each 8K full words, two H216 modules are used to store 36 data bits plus one parity bit.

| BANK SELEC | SELECT X SELECTION |         |       | Y SELECTION |      |      | N      |     |               |

|------------|--------------------|---------|-------|-------------|------|------|--------|-----|---------------|