# PDP-11/05 computer manual

1st Printing August 1972 2nd Printing September 1972 3rd Printing January 1973

Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

**PDP**

FLIP CHIP

**FOCAL**

DIGITAL

COMPUTER LAB

# CONTENTS

|           |                                            | Page |

|-----------|--------------------------------------------|------|

|           | PART I-COMPUTER DESCRIPTION                |      |

| CHAPTER 1 | COMPUTER COMPONENTS                        |      |

| 1.1       | Introduction                               | 1-1  |

| 1.2       | Computer Components                        | 1-1  |

| 1.2.1     | KD11-B Processor                           | 1-1  |

| 1.2.2     | Core Memory                                | 1-2  |

| 1.2.2.1   | Memory Organization                        | 1-3  |

| 1.2.2.2   | Memory Specifications                      | 1-3  |

| 1.2.3     | Power Supply                               | 1-3  |

| 1.2.4     | Backplane                                  | 1-4  |

| 1.3       | ME11-L Core Memory System                  | 1-5  |

| 1.4       | Extension Mounting Box                     | 1-5  |

| CUARTER O | LINHIDLIC                                  |      |

| CHAPTER 2 | OIVIRO2                                    |      |

| 2.1       | Introduction                               | 2-1  |

| 2.2       | Unibus Structure                           | 2-1  |

| 2.2.1     | Bidirectional Lines                        | 2-2  |

| 2.2.2     | Master-Slave Relationship                  | 2-2  |

| 2.2.3     | Inter-Locked Communication                 | 2-2  |

| 2.3       | Peripheral Device Organization and Control | 2-3  |

| 2.4       | Unibus Control Arbitration                 | 2-3  |

| 2.4.1     | Priority Transfer Requests                 | 2-4  |

| 2.4.2     | Processor Interrupts                       | 2-5  |

| 2.4.3     | Data Transfe <b>rs</b>                     |      |

|           |                                        | Page |

|-----------|----------------------------------------|------|

| CHAPTER 3 | UNPACKING AND INSTALLATION             |      |

| 3.1       | Introduction                           | 3–1  |

| 3.2       | Unpacking                              | 3–1  |

| 3.3       | Mechanical Description                 | 3–3  |

| 3.4       | Installation                           | 3–10 |

| 3.4.1     | Mounting Computer on Installed Slides  | 3–10 |

| 3.4.2     | Securing Computer to Cabinet Rack      | 3–10 |

| 3.4.3     | Installation of I/O Cables             | 3–11 |

| 3.5       | Interchangeable Peripheral Slots       | 3–11 |

| 3.6       | Side and Top Cover Installation        | 3-11 |

| 3.7       | AC Power Supply Connection             | 3-12 |

| 3.7.1     | Connecting to Voltages Other Than 115V | 3-12 |

| 3.7.2     | Quality of AC Power Source             | 3-12 |

| 3.8       | Cabinet Power Control                  | 3-12 |

| 3.9       | Installation Certification             | 3–13 |

| 3.10      | Warranty Service (Domestic Only)       | 3–14 |

| CHAPTER 4 | OPERATION                              |      |

| 4.1       | Introduction                           | 4-1  |

| 4.2       | Power Switch Operation                 | 4-1  |

| 4.3       | Function Switches                      | 4-1  |

| 4.4       | Address/Data Switches                  | 4-3  |

| 4.5       | Console Indicators                     | 4-3  |

| 4.6       | Operation Console                      | 4-3  |

| 4.6.1     | LOAD ADDRess Switch                    | 4-5  |

| 4.6.2     | EXAM Switch                            | 4-5  |

| 4.6.3     | DEPosit Switch                         | 4-6  |

|           |                                                            | Page         |

|-----------|------------------------------------------------------------|--------------|

| 4.6.4     | ENABLE/HALT Switch                                         | 4-6          |

| 4.6.5     | START Switch                                               | 4-7          |

| 4.6.6     | CONTINUE Switch                                            | 4-7          |

| 4.7       | Unconditional Computer and Unibus Initilization            | 4-8          |

| 4.8       | Loading Programs from Paper Tape                           | 4-8          |

| 4.8.1     | The Bootstrap Loader                                       | 4-9          |

| 4.8.1.1   | Loading the Loader Into Memory                             | 4-10         |

| 4.8.1.2   | Loading Bootstrap Tapes                                    | 4-11         |

| 4.8.1.3   | Bootstrap Loader Operation                                 | 4-13         |

| 4.8.2     | The Absolute Loader                                        | 4-14         |

| 4.8.2.1   | Loading the Loader Into Memory                             | 4-15         |

| 4.8.2.2   | Loading Absolute Tapes                                     | 4-15         |

| 4.8.3     | Memory Dumps                                               | 4-17         |

| 4.8.3.1   | Operating Procedures                                       | 4-17         |

| 4.8.3.2   | Output Formats                                             | <b>4–</b> 18 |

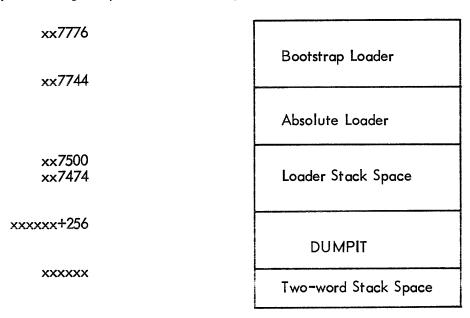

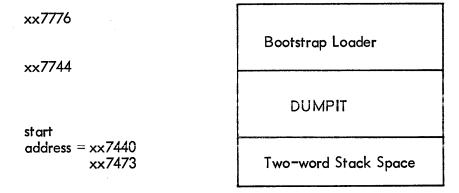

| 4.8.3.3   | Storage Maps                                               | 4-19         |

| 4.9       | Installation Testing                                       | 4-19         |

| 4.10      | SCL Baud Rate Adjustment                                   | 4-20         |

|           | PART II - KD11-B PROCESSOR                                 |              |

| CHAPTER 1 | GENERAL DESCRIPTION                                        |              |

| 1.1       | Introduction                                               | 1-1          |

| 1.2       | KD11-B Definition                                          | 1-1          |

| 1.3       | KD11-B and the Unibus                                      | 1-2          |

| 1.4       | KD11-B As an Instruction Interpreter                       | 1-3          |

| 1.5       | KD11-B Print Set                                           | 1-4          |

| 1.5.1     | Medium and Large Scale Integration Circuit Representations | 1-7          |

|           |                             | Page |

|-----------|-----------------------------|------|

| 1.5.2     | Microprogram Documentation  | 1-7  |

| 1.5.3     | Read-Only Memory (ROM) Maps | 1-8  |

| CHAPTER : | 2 INSTRUCTION SET           |      |

| 2.1       | Introduction                | 2-1  |

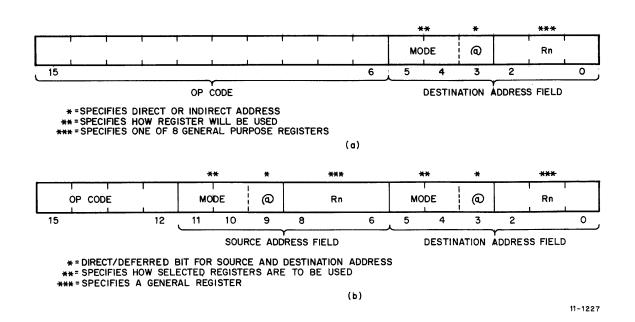

| 2.2       | Addressing Modes            | 2-1  |

| 2.2.1     | Introduction                | 2-1  |

| 2.2.2     | Instruction Timing          | 2-4  |

| 2.3       | PDP-11/05 Instructions      | 2–4  |

| CHAPTER : | 3 CONSOLE DESCRIPTION       |      |

| 3.1       | Introduction                | 3–1  |

| 3.2       | General Description         | 3-1  |

| 3.2.1     | Address/Data Register Logic | 3-1  |

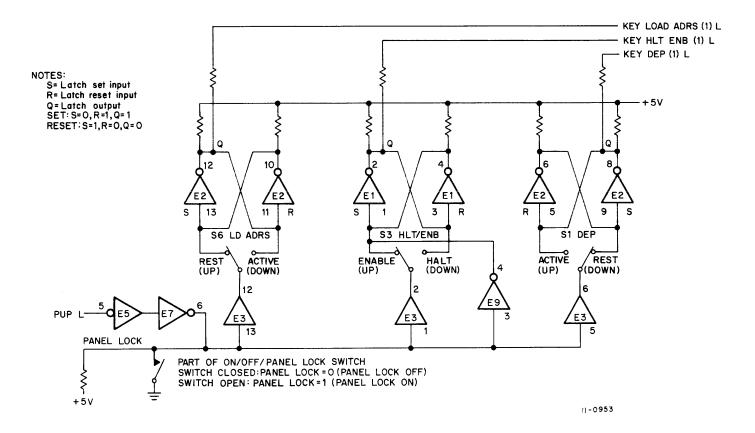

| 3.2.2     | Control Switch Logic        | 3–3  |

| 3.3       | Detailed Description        | 3–3  |

| 3.3.1     | Multiplexer                 | 3-4  |

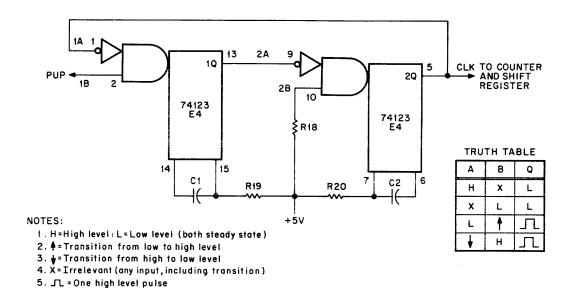

| 3.3.2     | Clock                       | 3–5  |

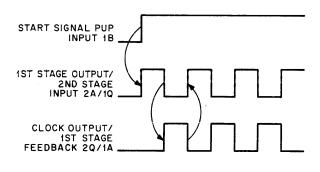

| 3.3.3     | Counter                     | 3–6  |

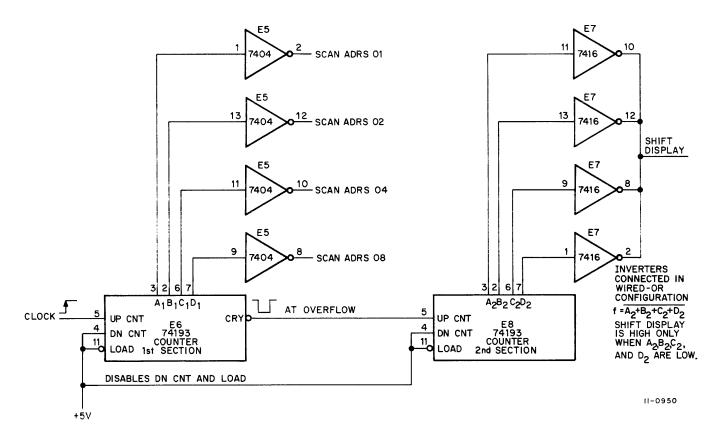

| 3.3.4     | Display Buffer and Driver   | 3–10 |

| 3.3.5     | Control Switches and Logic  | 3-10 |

| 3.3.5.1   | Normal Operating Mode       | 3-12 |

| 3.3.5.2   | Panel Lock Mode             | 3-14 |

| 3.3.5.3   | Power Loss During Operation | 3-14 |

| CHAPTER   | 4 DETAILED DESCRIPTION      |      |

| 4.1       | Introduction                | 4-1  |

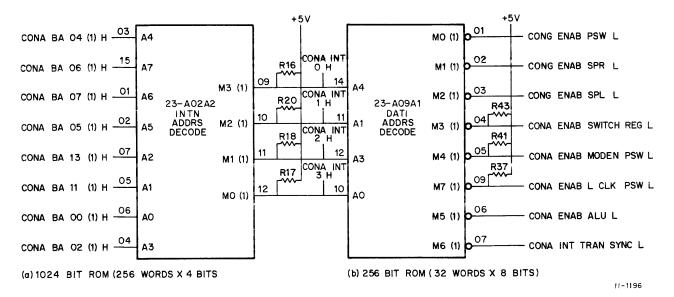

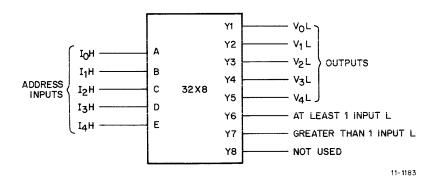

| 4.2       | ROMs As Generalized Gates   | 4-1  |

|         |                                              | Page |

|---------|----------------------------------------------|------|

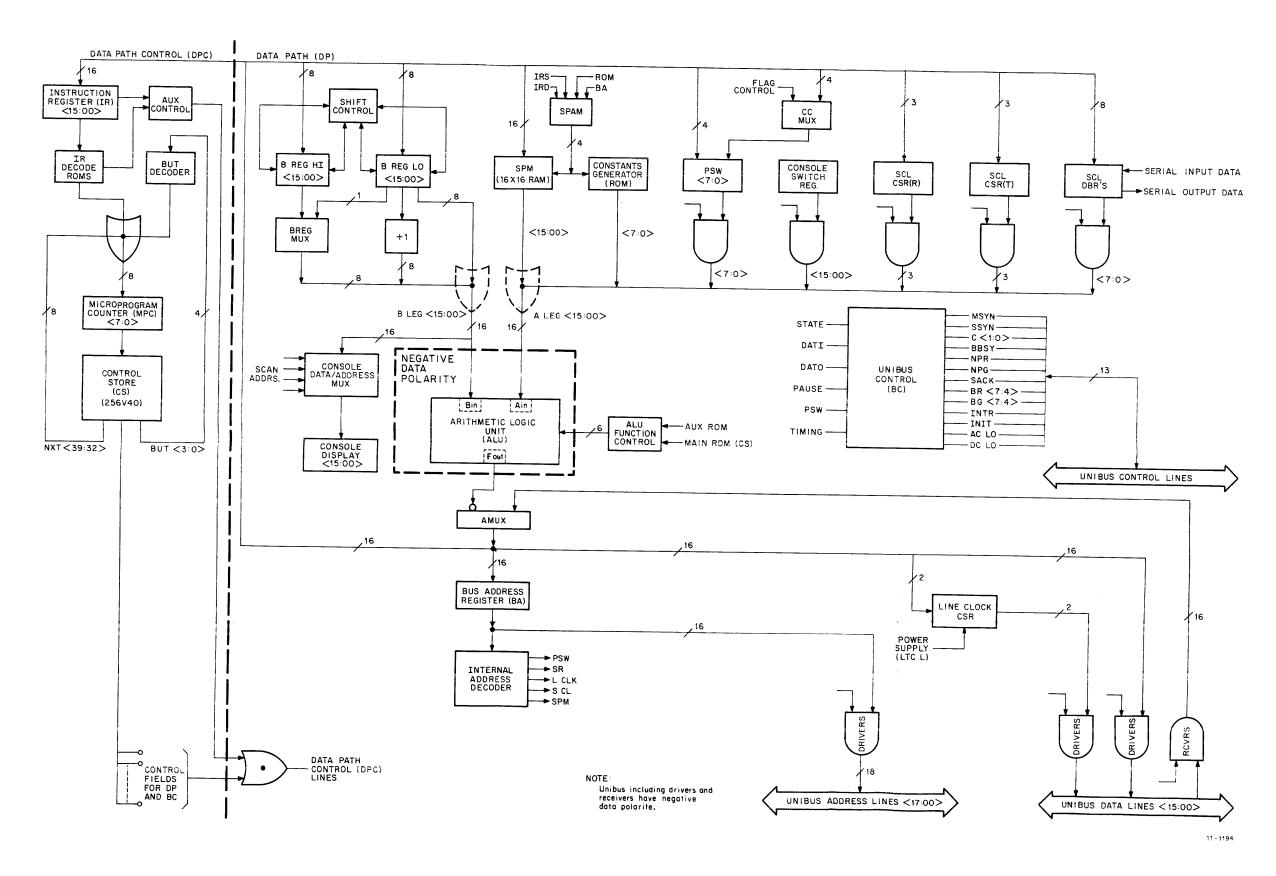

| 4.3     | KD11-B Data Path, Simplified Description     | 4-2  |

| 4.3.1   | Data Path (DP) Detailed Description          | 4-2  |

| 4.3.2   | DP Data Polarities                           | 4-3  |

| 4.3.3   | Data Path Control (DPC)                      | 4-4  |

| 4.3.4   | The A MUX1                                   | 4-6  |

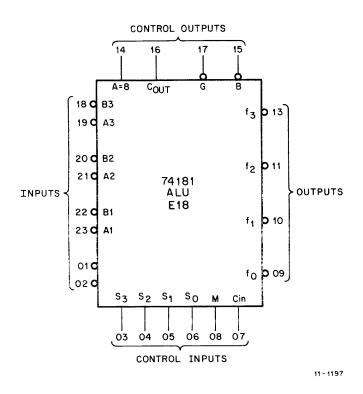

| 4.3.5   | The ALU                                      | 4-6  |

| 4.4     | Scratch Pad Storage Register                 | 4-7  |

| 4.4.1   | Scratch Pad Address Multiplexer (SPAM)       | 4-7  |

| 4.4.2   | Processor Status Word Register               | 4-7  |

| 4.4.3   | The Constants Generator                      | 4-8  |

| 4.4.4   | The Console Switch Register                  | 4-11 |

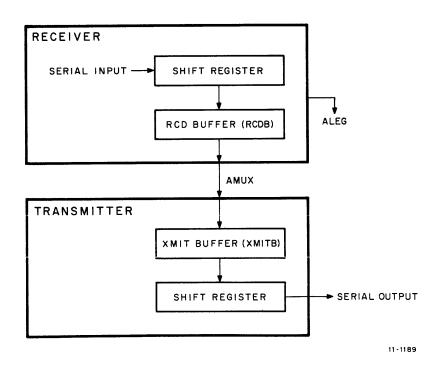

| 4.4.5   | Serial Communications Line                   | 4-11 |

| 4.5.    | B-Leg Storage Register                       | 4-11 |

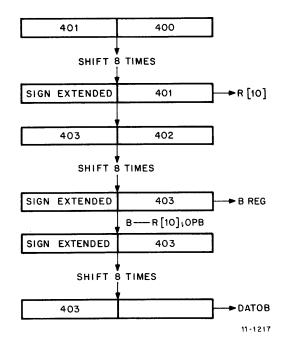

| 4.5.1   | Byte Instructions                            | 4-11 |

| 4.5.2   | Instruction Register (IR) and IR Decode      | 4-12 |

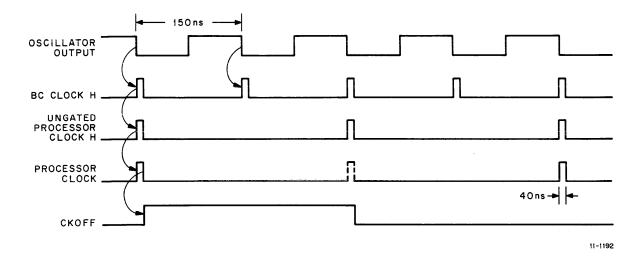

| 4.6     | Data Path Control and Clocking               | 4-13 |

| 4.7     | Unibus Control                               | 4-15 |

| 4.7.1   | DATI Timing                                  | 4-16 |

| 4.7.2   | DATI Operation                               | 4-16 |

| 4.7.2.1 | DATIP Operation                              | 4-18 |

| 4.7.2.2 | DATIP Logic                                  | 4-19 |

| 4.7.3   | DATO                                         | 4-20 |

| 4.7.4   | Byte Operations                              | 4-20 |

| 4.7.5   | Bus Errors                                   | 4-21 |

| 4.8     | Internal Unibus Addresses                    | 4-22 |

| 4.9     | Bus Requests (BR)                            | 4-23 |

| 4.10    | Non-Processor Requests (NPR)                 | 4-28 |

| 4.11    | Serial Communications Line Description (SCL) | 4-28 |

| 4.12    | Line Clock                                   | 4-31 |

| 4.13    | Power Fail                                   | 4-31 |

|                                                  | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MICROPROGRAM CONTROL                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Introduction                                     | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Microprogrammed Control CVS Conventional Control | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

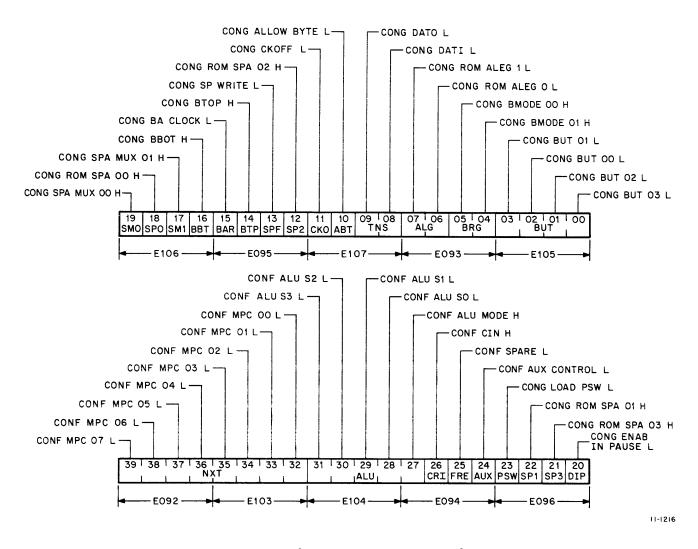

| Control Store                                    | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Branching Within Microroutines                   | 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

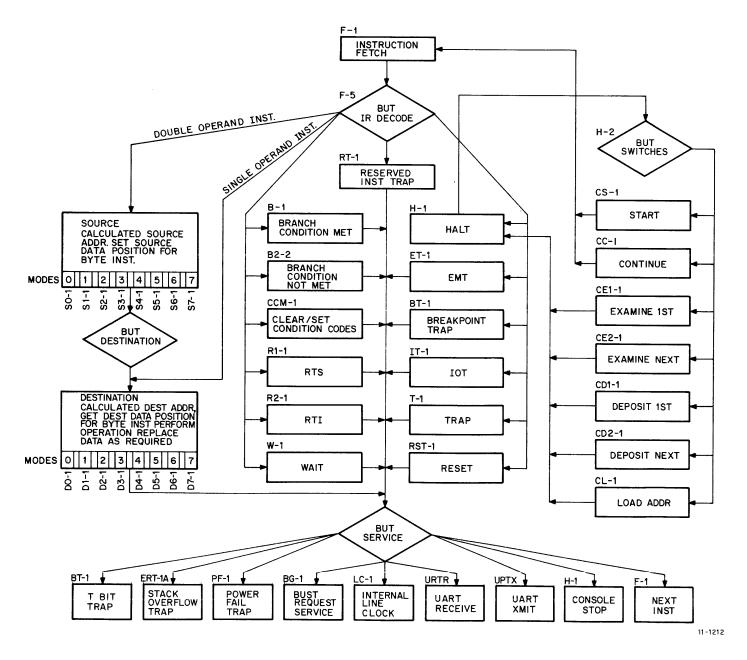

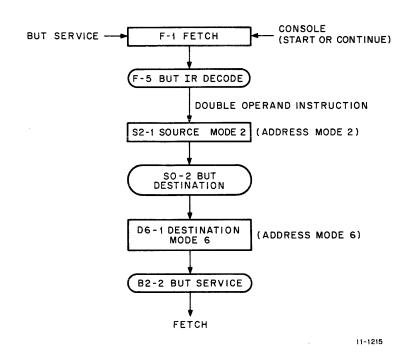

| Microprogram Flow                                | 5-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Flow Chart Notation                              | 5-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Traps and Interrupts                             | 5-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Console Functions                                | 5-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Microprogram Symbolic Listing                    | 5-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Microprogram Binary Listing                      | 5-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Microprogram Cross Reference Listing             | 5–28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MAINTENANCE                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Introduction                                     | 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Diagnostics                                      | 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Types of Failures                                | 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Suggested Equipment                              | 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Procedures                                       | 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Adjustments                                      | 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| KD11-B Print Function Table                      | 6–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| External Clock Inputs                            | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

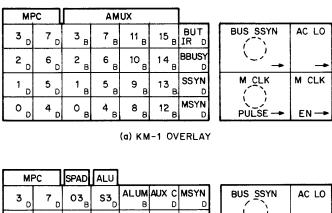

| KM11 Maintenance Panel                           | 6-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Using KM Maintenance Panel                       | 6-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Console Maintenance                              | 6-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                  | Introduction Microprogrammed Control CVS Conventional Control Control Store Branching Within Microroutines Microprogram Flow Flow Chart Notation Traps and Interrupts Console Functions Microprogram Symbolic Listing Microprogram Binary Listing Microprogram Cross Reference Listing  MAINTENANCE Introduction Diagnostics Types of Failures Suggested Equipment Procedures Adjustments KD11-B Print Function Table External Clock Inputs KM11 Maintenance Panel Using KM Maintenance Panel |

|           |                                                | Page |

|-----------|------------------------------------------------|------|

|           | PART III - MM11-K, MM11-L MEMORIES             |      |

| CHAPTER 1 | GENERAL DESCRIPTION                            |      |

| 1.1       | Introduction                                   | 1-1  |

| 1.2       | General Description                            | 1-1  |

| 1.2.1     | Physical Description                           | 1-2  |

| 1.2.2     | Specifications                                 | 1-2  |

| 1.2.3     | Functional Description                         | 1-7  |

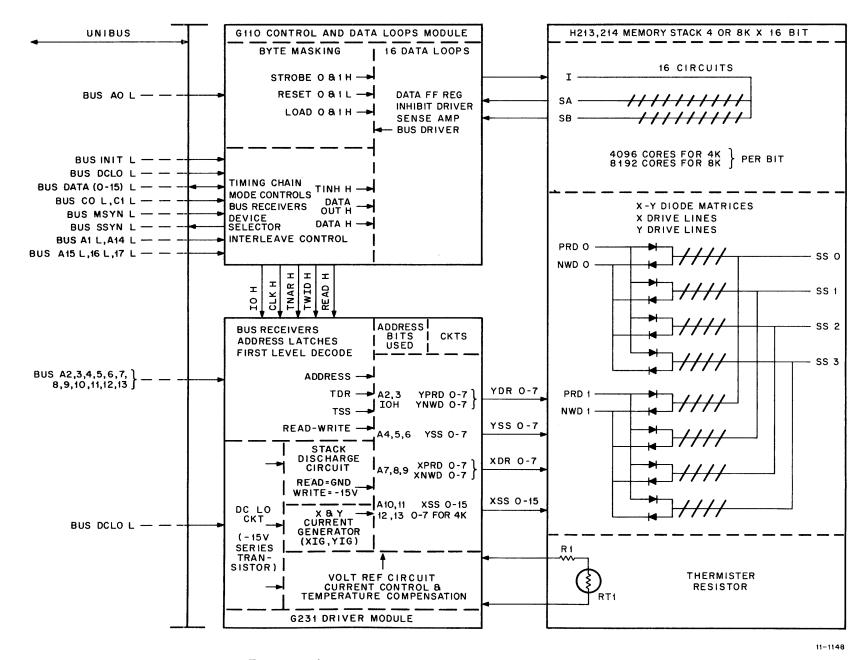

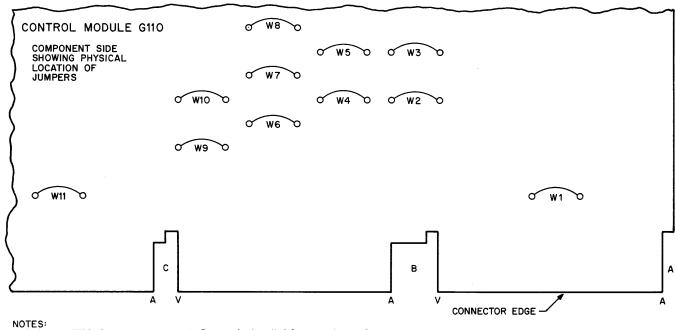

| 1.2.3.1   | G110 Control Module                            | 1-7  |

| 1.2.3.2   | G231 Drive Module                              | 1-9  |

| 1.2.3.3   | H213 or H214 Stack Module                      | 1-10 |

| 1.2.4     | Basic Memory Operations                        | 1-10 |

| 1.2.4.1   | Data In (DATI) Cycle                           | 1-11 |

| 1.2.4.2   | Data In, Pause (DATIP) Cycle                   | 1-11 |

| 1.2.4.3   | Data Out (DATO) Cycle                          | 1-11 |

| 1.2.4.4   | Data Out, Byte (DATOB) Cycle                   | 1-12 |

| CHAPTER 2 | DETAILED DESCRIPTION                           |      |

| 2.1       | Introduction                                   | 2-1  |

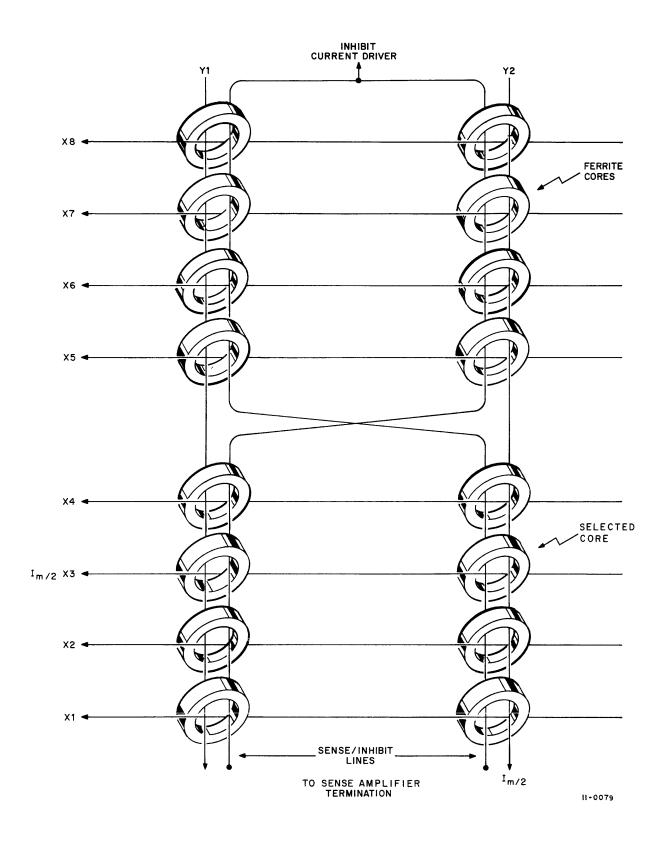

| 2.2       | Core Array                                     | 2-1  |

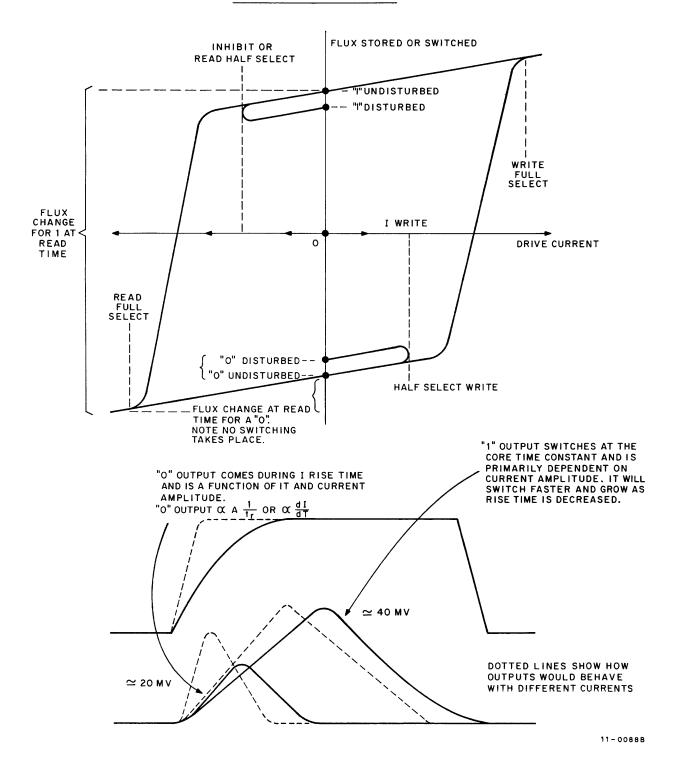

| 2.3       | Memory Operation                               | 2-3  |

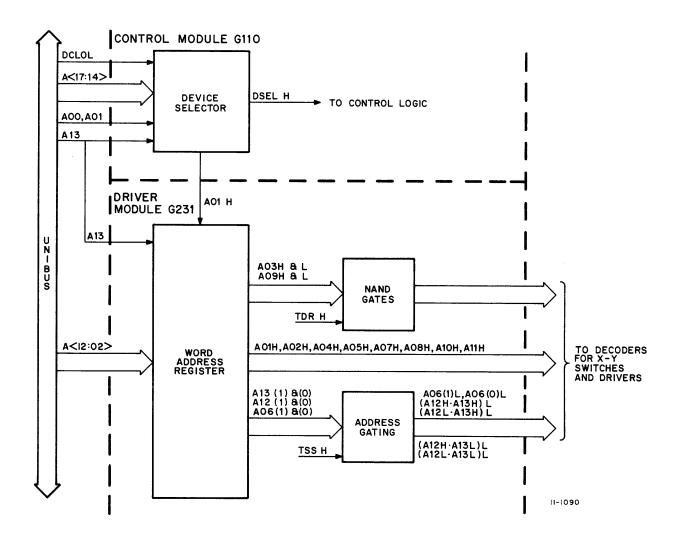

| 2.4       | Device and Word Selection                      | 2-5  |

| 2.4.1     | Memory Organization and Addressing Conventions | 2-8  |

| 2.4.2     | Device Selector                                | 2-10 |

| 2.4.3     | Word Selection                                 | 2-14 |

| 2.4.3.1   | Word Address Register and Gating Logic         | 2-14 |

| 2 1 3 3   | Drivers and Switches                           | 2-21 |

|           |                                              | Page |

|-----------|----------------------------------------------|------|

| 2.4.3.4   | Word Address Decoding and Selection Sequence | 2-24 |

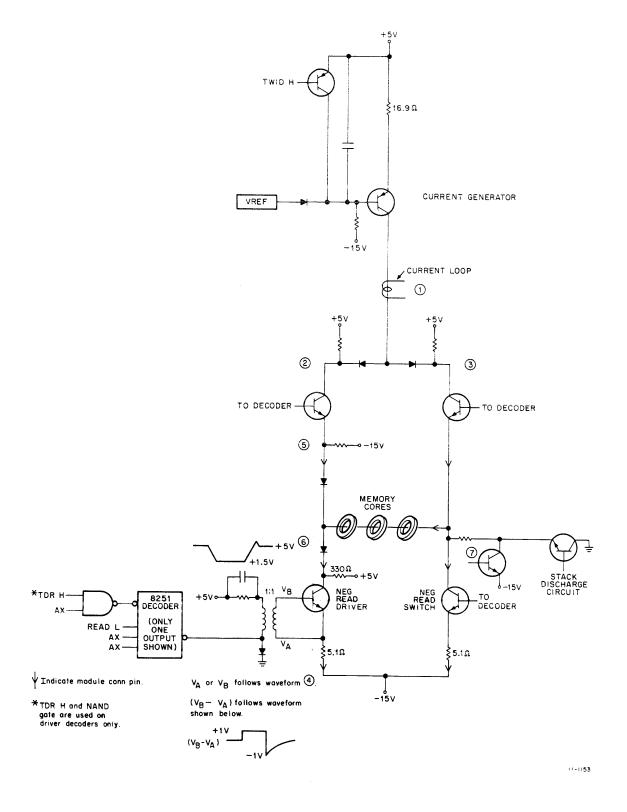

| 2.5       | READ/WRITE Current Generation and Sensing    | 2-26 |

| 2.5.1     | Read/Write Operations                        | 2-26 |

| 2.5.2     | X- and Y-Current Generators                  | 2-29 |

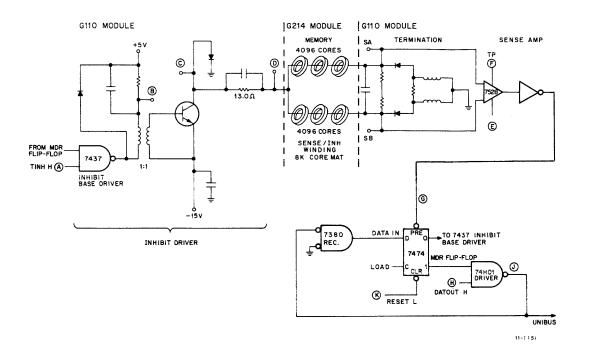

| 2.5.3     | Inhibit Driver                               | 2-31 |

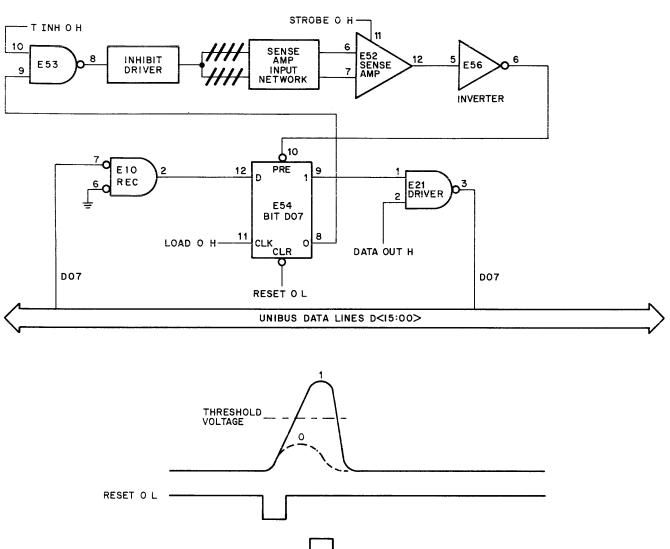

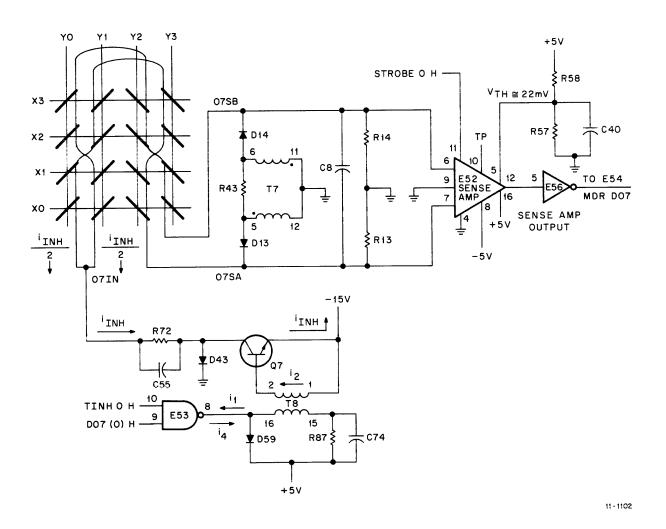

| 2.5.4     | Sense Amplifier                              | 2-33 |

| 2.5.5     | Memory Data Register                         | 2-33 |

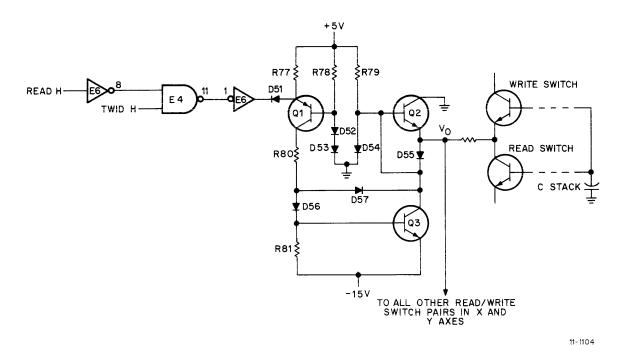

| 2.6       | Stack Discharge Circuit                      | 2-34 |

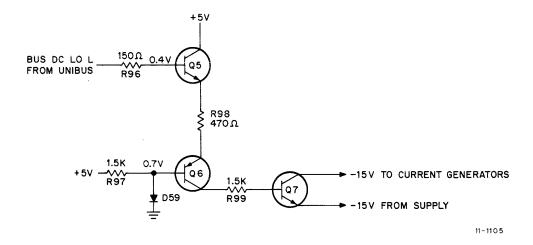

| 2.7       | DC LO Circuit                                | 2-36 |

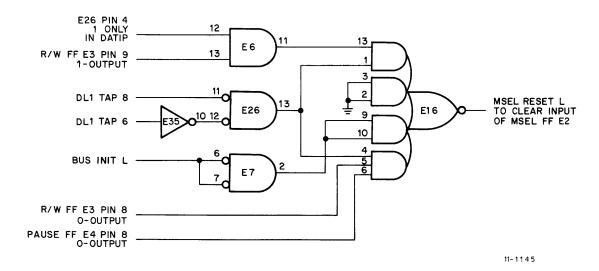

| 2.8       | Operating Model Selection Logic              | 2-37 |

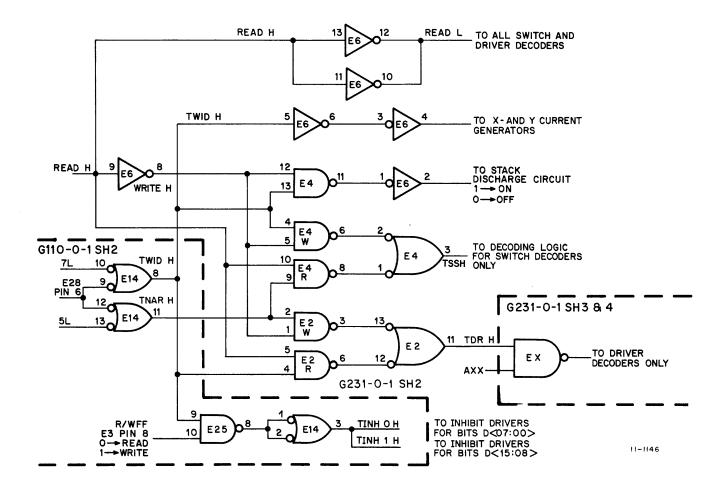

| 2.9       | Control Logic                                | 2-40 |

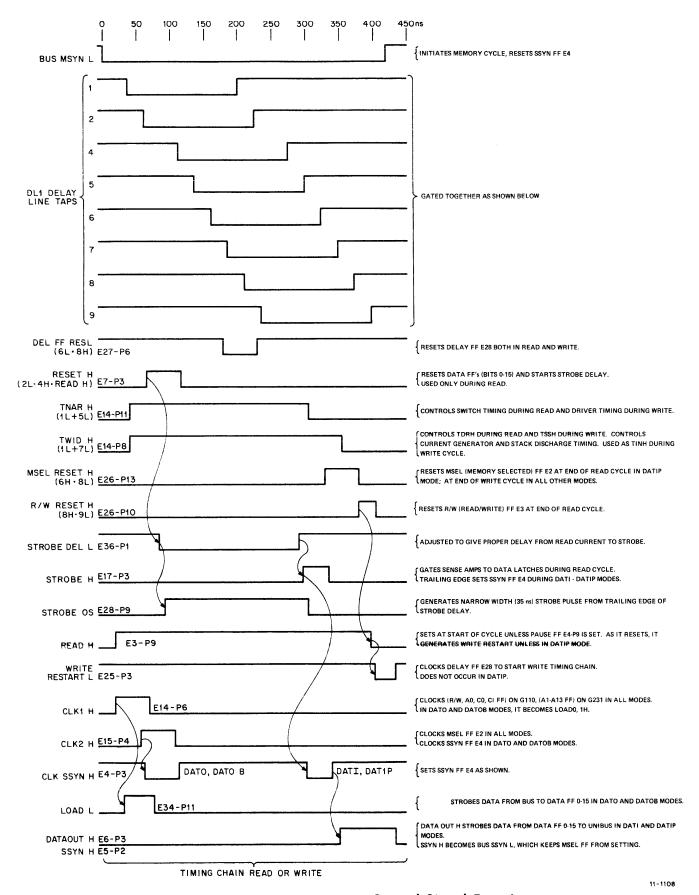

| 2.9.1     | Timing Circuit                               | 2-40 |

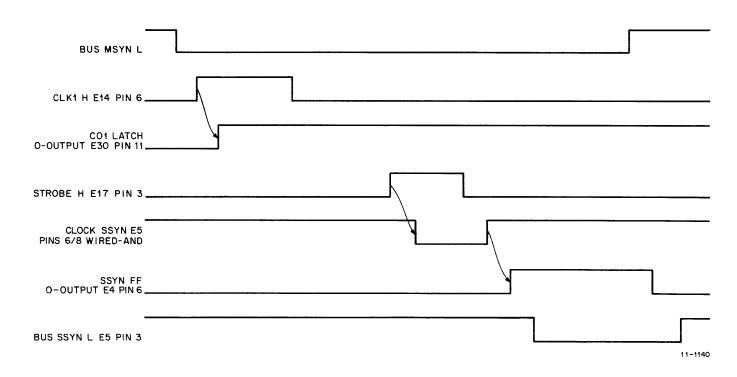

| 2.9.2     | Slave Synchronization (SSYN) Circuit         | 2-47 |

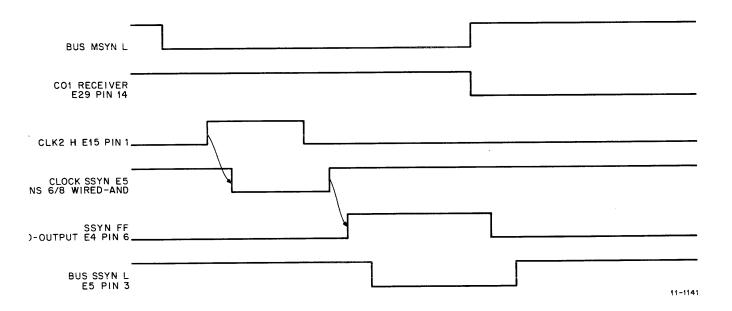

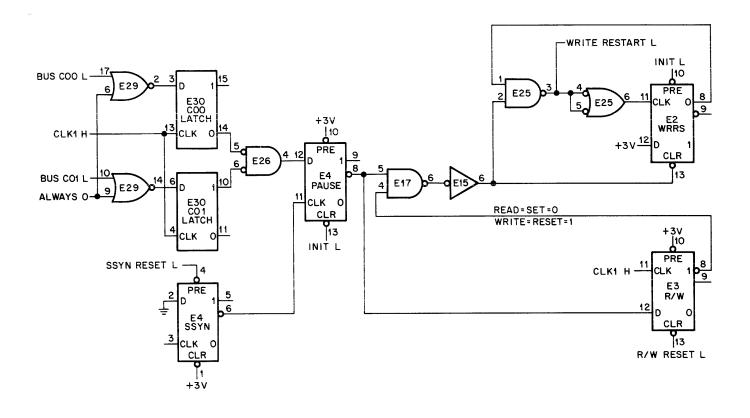

| 2.9.3     | Pause/Write Restart Circuit                  | 2–50 |

| 2.9.4     | Strobe Generating Circuit                    | 2-52 |

| 2.9.5     | Data In (DATI) Operation                     | 2-54 |

| 2.9.6     | Data In Pause (DATIP) Operation              | 2-57 |

| 2.9.7     | Data Out (DATO) Operation                    | 2-58 |

| 2.9.8     | Data Out Byte (DATOB) Operation              | 2–59 |

| CHAPTER 3 | MAINTENANCE                                  |      |

| 3.1       | Introduction                                 | 3-1  |

| 3.2       | Preventive Maintenance                       | 3-1  |

| 3.2.1     | Initial Procedures                           | 3-1  |

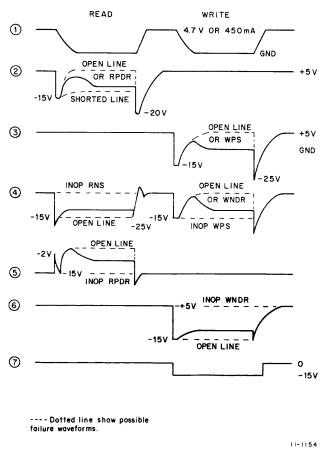

| 3.2.2     | Checking Output of Current Generator         | 3-2  |

| 3.3       | Corrective Maintenance                       | 3–2  |

| 3.3.1     | Strobe Delay Check and Adjustment            | 3-3  |

| 3.3.2     | Corrective Maintenance Aids                  | 3-3  |

| 3.4       | Programming Tests                            | 3-11 |

|           |                                              | Page |

|-----------|----------------------------------------------|------|

| 3.4.1     | Address Test Up (MAINDEC-11-DIAA)            | 3-11 |

| 3.4.2     | Address Test Down (MAINDEC-11-DIBA)          | 3-11 |

| 3.4.3     | No Dual Address Test (MAINDEC-11-DICA)       | 3-12 |

| 3.4.4     | Basic Memory Patterns Test (MAINDEC-11-DIDA) | 3-12 |

| 3.4.5     | Worst-Case Noise Test (MAINDEC-11-DIGA)      | 3-12 |

|           | PART IV - POWER SUPPLY                       |      |

| CHAPTER 1 | GENERAL DESCRIPTION                          |      |

| 1.1       | Introduction                                 | 1-1  |

| 1.2       | Physical Description                         | 1-2  |

| 1.2.1     | Power Control                                | 1-2  |

| 1.2.2     | Power Chassis Assembly                       | 1-3  |

| 1.2.3     | DC Regulator Module                          | 1-3  |

| 1.2.4     | DC Cable                                     | 1-8  |

| 1.2.5     | AC Cable                                     | 1-8  |

| 1.3       | Specifications                               | 1-9  |

| CHAPTER 2 | DETAILED DESCRIPTION                         |      |

| 2.1       | Introduction                                 | 2-1  |

| 2.2       | AC Input Circuit                             | 2-1  |

| 2.3       | DC Regulator Module Operation                | 2-4  |

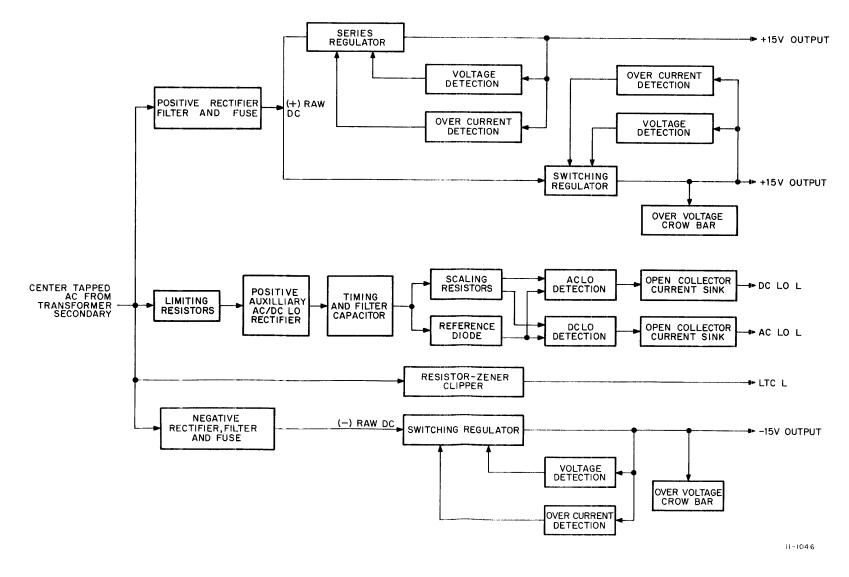

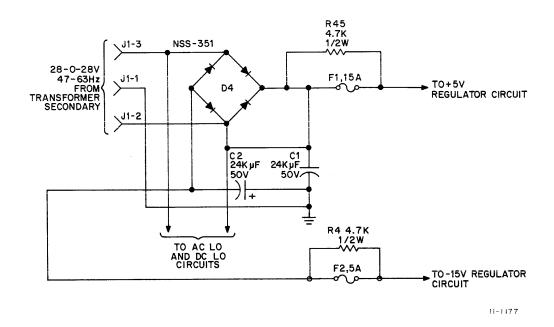

| 2.3.1     | Generation of $\pm$ Raw DC                   | 2-6  |

| 2.3.2     | LTC L Circuit                                | 2-6  |

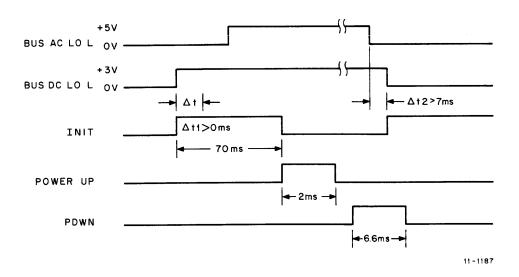

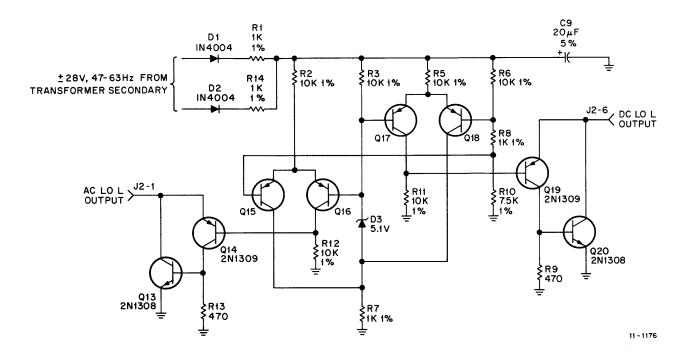

| 2.3.3     | BUS AC LO and BUS DC LO L Circuits           | 2-7  |

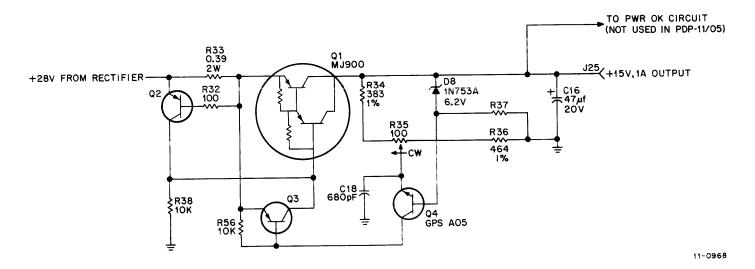

| 2.3.4     | +15V Regulator Circuit                       | 2-9  |

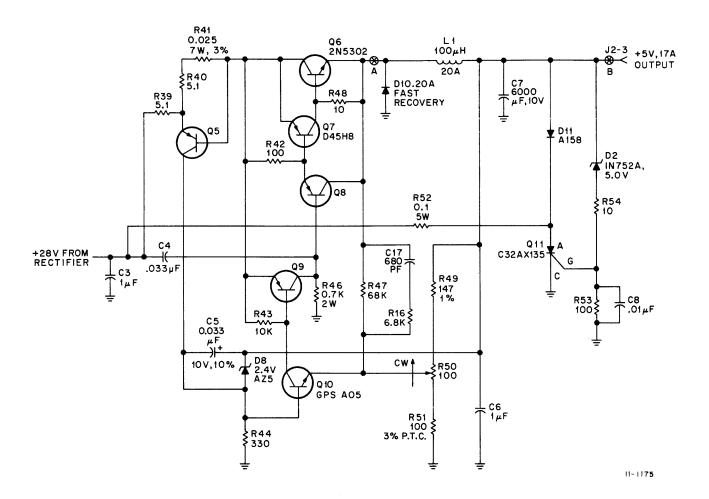

| 2.3.5     | +5V Regulator Circuit                        | 2-10 |

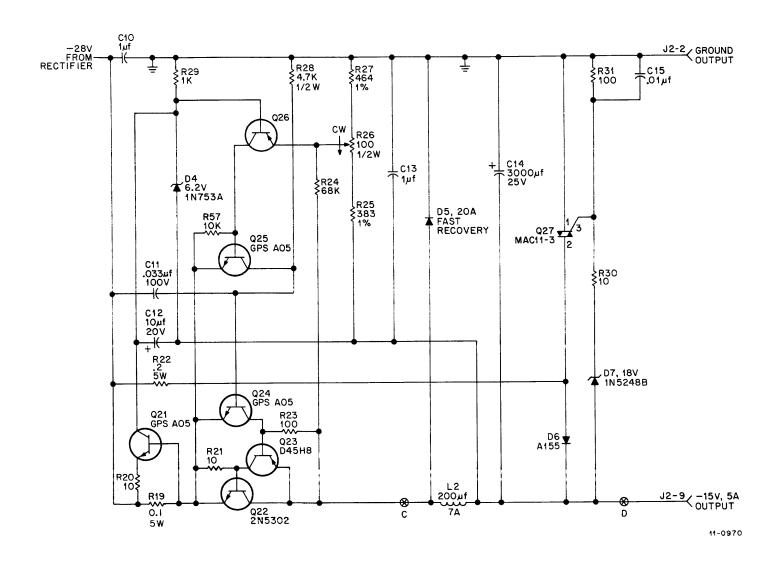

| 2.3.6     | -15V Regulator Circuit                       | 2-12 |

|           |                                                | Page |

|-----------|------------------------------------------------|------|

| CHAPTER 3 | MAINTENANCE                                    |      |

| 3.1       | Introduction                                   | 3–1  |

| 3.2       | Adjustments                                    | 3-1  |

| 3.3       | Circuit Waveforms                              | 3-2  |

| 3.4       | Troubleshooting                                | 3-2  |

| 3.4.1     | Troubleshooting Rules                          | 3-6  |

| 3.4.2     | Troubleshooting Hints                          | 3-6  |

| 3.4.3     | Troubleshooting Chart                          | 3-7  |

| 3.5       | Parts Identification                           | 3-9  |

|           | TABLES                                         |      |

|           | PART I                                         |      |

| 4-1       | Significance of Address/Data Indicators        | 4-4  |

| 4-2       | Bootstrap Loader Instructions                  | 4-9  |

| 4–3       | Memory Bank Assignments                        | 4-10 |

|           | PART II                                        |      |

| 2-1       | Addressing Modes                               | 2-3  |

| 2-2       | Addressing Times                               | 2-4  |

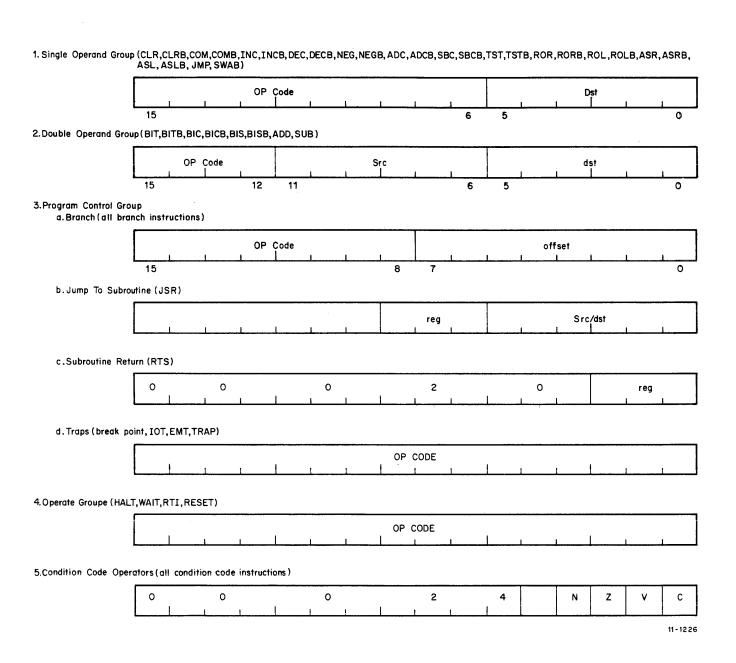

| 2-3       | Single Operand Instructions                    | 2-6  |

| 2-4       | Double Operand Instructions                    | 2-10 |

| 2-5       | Program Control Instructions                   | 2-13 |

| 3-1       | Scan Address Signal Generation                 | 3-4  |

| 3-2       | Counter States                                 | 3-9  |

| 4-1       | Utilization of SP                              | 4-7  |

| 4-2       | Scratch Pad Address Sources through SPAM       | 4-8  |

| 4–3       | Contents of the Constants Generator (E025) ROM | 4-9  |

| 4-4       | Unihus Addresses                               | 4-22 |

# TABLES (Cont)

|     |                                               | Page |

|-----|-----------------------------------------------|------|

| 4-5 | Trap Priorities                               | 4-25 |

| 5-1 | KD11-B Control Store Fields                   | 5-3  |

| 5-2 | Microprogram Branches (BUT)                   | 5-8  |

| 5-3 | Flow Notation Glossary                        | 5-15 |

| 6-1 | Test Equipment and Tools                      | 6-2  |

| 6-2 | Baud Rate Adjustment                          | 6-5  |

| 6-3 | Engineering Drawing Print, List and Functions | 6-6  |

| 6-4 | KM-1 and KM-2 Overlay Designations            | 6-10 |

|     | PART III                                      |      |

| 1-1 | MM11-K and L Memory Specifications            | 1-2  |

| 2-1 | Addressing Functions                          | 2-7  |

| 2-2 | Enabling Signals for Word Register Gating     | 2-17 |

| 2-3 | Word Address Decoding Signals                 | 2-25 |

| 2-4 | Selection of Bus Transactions                 | 2-38 |

| 2-5 | Generation of Memory Operating Signals        | 2-39 |

|     | PART IV                                       |      |

| 1-1 | Power Supply Specifications                   | 1-9  |

| 3-2 | Troubleshooting Chart                         | 3–7  |

# **ILLUSTRATIONS**

| Figure No. | Title                                                            | Page |

|------------|------------------------------------------------------------------|------|

|            | PART 1-COMPUTER DESCRIPTION                                      |      |

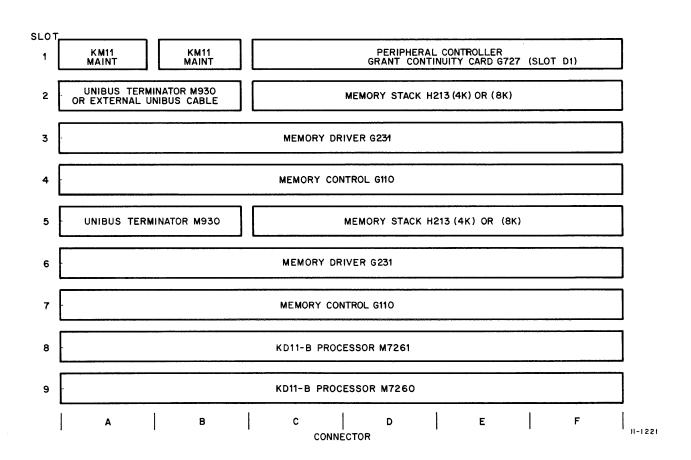

| 1-1        | Module Utilization Diagram For Configuration 1 (16K)             | 1-6  |

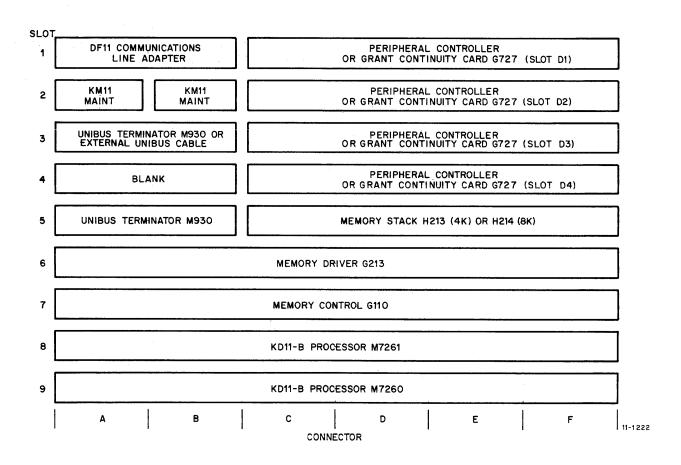

| 1-2        | Module Utilization Diagram For Configuration 2 (8K)              | 1-7  |

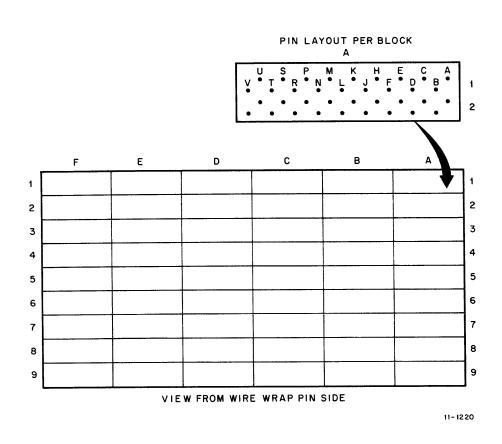

| 1-3        | Computer Backplane Connector and Pin<br>Designations             | 1-8  |

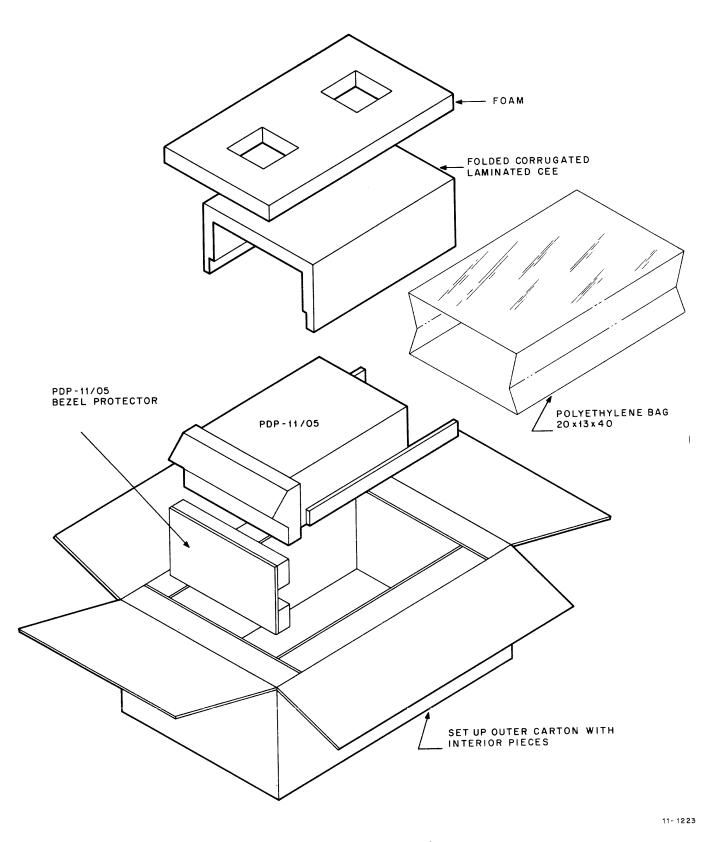

| 3-1        | Computer Packaging                                               | 3-2  |

| 3-2        | Computer Mounting Box                                            | 3-4  |

| 3-3        | Computer Box With Top Cover Removed                              | 3-5  |

| 3-4        | Computer Box With Top and Side Covers<br>Removed                 | 3-6  |

| 3-5        | Computer Chassis (showing both peripheral cables and the Unibus) | 3-7  |

| 3-6        | Mounting Box Without Modules                                     | 3-8  |

| 3-7        | Rear of Computer Showing Cable Strain<br>Reliefs                 | 3-9  |

| 3-8        | Typical Cabinet Power Control System<br>Wiring Diagram           | 3-13 |

| 4-1        | Console Illustrating Switch Movements                            | 4-2  |

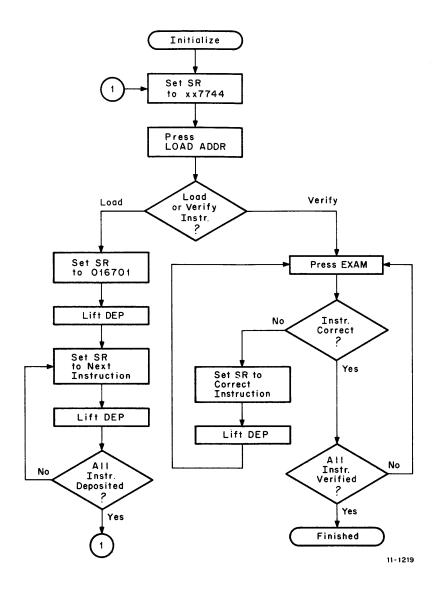

| 4-2        | Loading and Verifying the Bootstrap Loader                       | 4-12 |

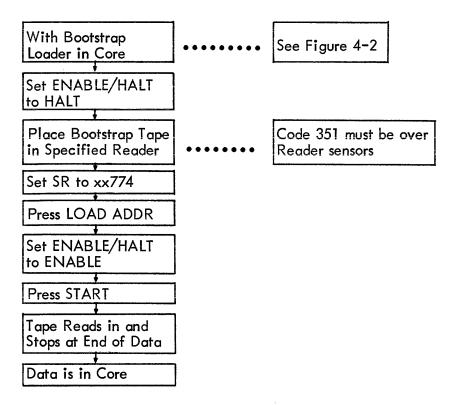

| 4-3        | Loading Bootstrap Tapes Into Memory                              | 4-13 |

|            | PART 2-KD11-B PROCESSOR                                          |      |

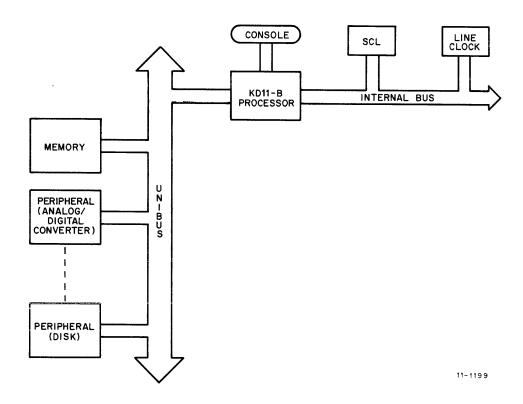

| 1-1        | KD11-B With Interconnections to Memory and Peripherals           | 1-2  |

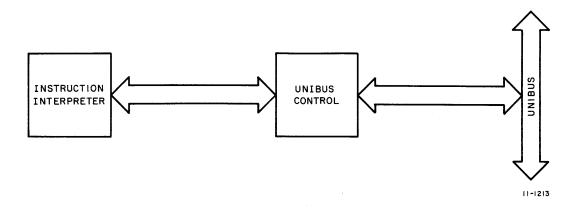

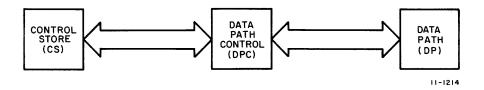

| 1-2        | KD11-B Processor Block Diagram                                   | 1-4  |

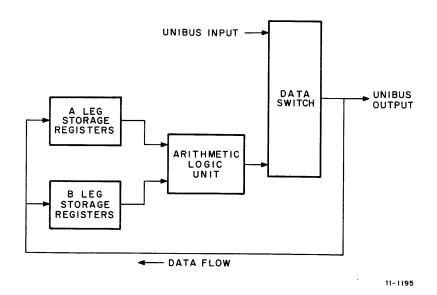

| 1-3        | Instruction Interpreter Block Diagram                            | 1-4  |

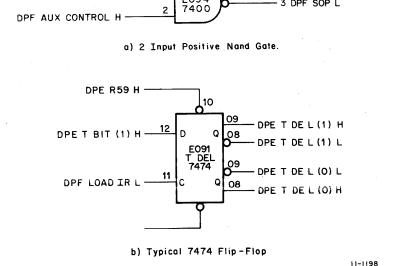

| 1-4        | Typical Small Scale Integrated Circuit Representations           | 1-5  |

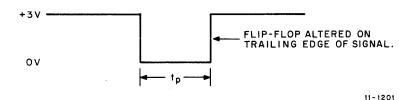

| 1-5        | DPF LOAD IRL Signal                                              | 1-6  |

| 1-6        | ALV, MSI Circuit Type 74181 Representation                       | 1-7  |

| 1-7        | E068 ROM Map Example                                             | 1-9  |

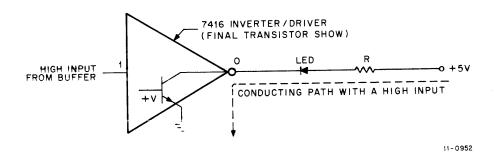

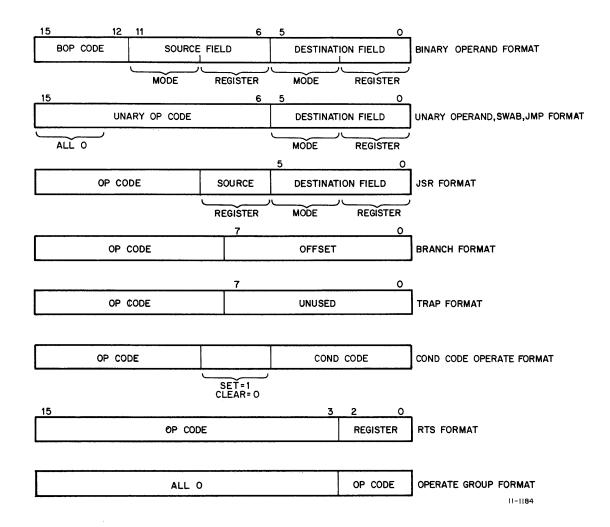

#### ILLUSTRATIONS (Cont) Figure No. Title Page 2-1 Addressing Mode Instruction Formats 2-2 2-2 PDP-11 Instruction Formats 2-5 3-1 Console Functional Block Diagram 3-2 3-2 Console Clock, Schematic and Timina 3-5 Diagram 3-3 3-7 Counter, Simplified Logic Diagram 3-4 Display Buffer and Driver, Simplified Logic Diagram 3-11 3-5 LED Driver Circuit 3-11 3-6 Control Switches and Bounce Buffers, Logic Diagram 3 - 134-1 1024-Bit and 256-Bit ROMs 4-1 4-2 32 x 8 ROM used as Generalized Gate 4-3 4-3 KD11-B Simplified Data Path Block Diagram 4-4 4-4 KD11-B Detailed Block Diagram 4-5 4-5 Byte Format for Shifting Instructions 4-13 4-6 KD11-B Processor Clock Phasing 4-14 4-7 KD11-B Basic Oscillator 4-14 4-8 DATI and DATO Timing 4-17 4-9 4-24 Unibus Address Decoding 4-10 4-27 Bus Request (BR) Timing 4-11 4-29 Double Buffering Data Flow 4-12 Bus AC LO and Bus DC LO Timing Diagram 4-32 5-1 Control Store Word Bit and Field Format 5-3 5-2 KD11-B Simplified Flow Diagram 5-12 5-3 Excerpt from Microprogram Flow (K-NL-KD11-B-1) 5-14 CMP #15, CHAR (022767) Simplified Flow 5-4 5-17 Diagram 5-5 Excerpt of (K-WL-KD-11-B-2) Microprogram Symbolic Listing 5-29 5-6 Excerpt of Microprogram Binary Listing 5-30 (K-W-KD11-B-3)6-1 KM11 Maintenance Module, KD11-B

**Overlays**

6-9

| Figure No. | ILLUSTRATIONS (Cont)<br>Title                                                    | Page |  |

|------------|----------------------------------------------------------------------------------|------|--|

| -          | PART 3-MM11-K, MM11-L MEMORIES                                                   |      |  |

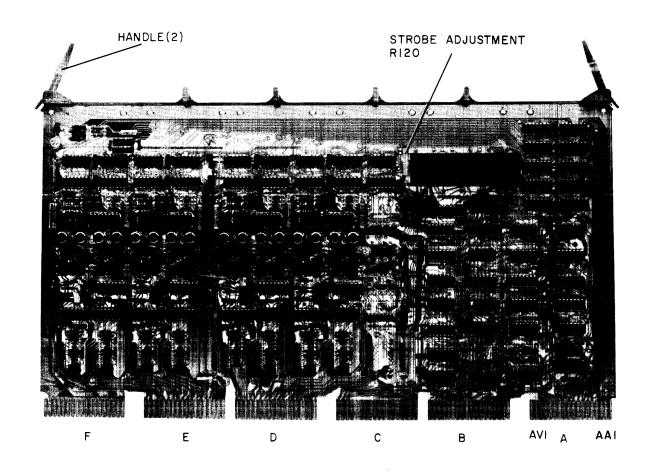

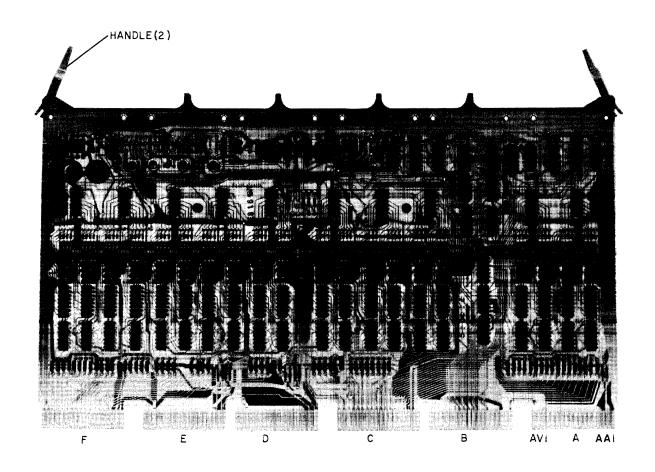

| 1-1        | Component Side of G110 Control Module                                            | 1-4  |  |

| 1-2        | Component Side of G231 Drive Module                                              | 1-5  |  |

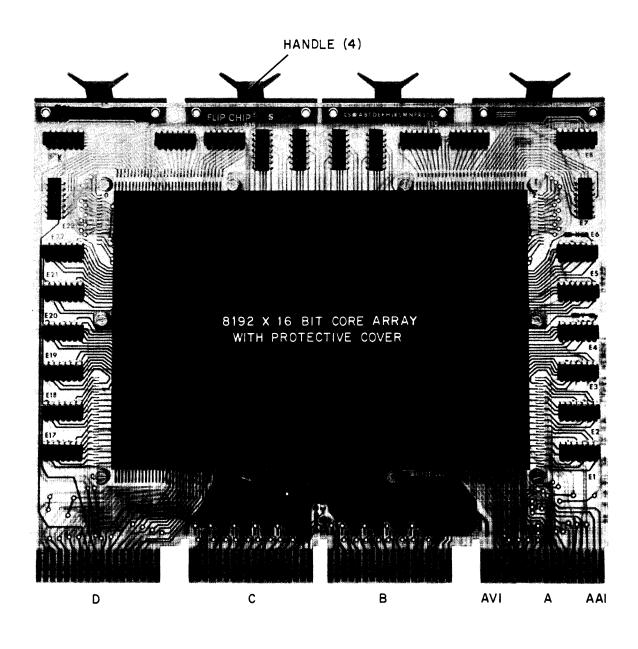

| 1-3        | Component Side of 8K H214 Stack Module                                           | 1-6  |  |

| 1-4        | MM11-K, L Memory Block Diagram                                                   | 1-8  |  |

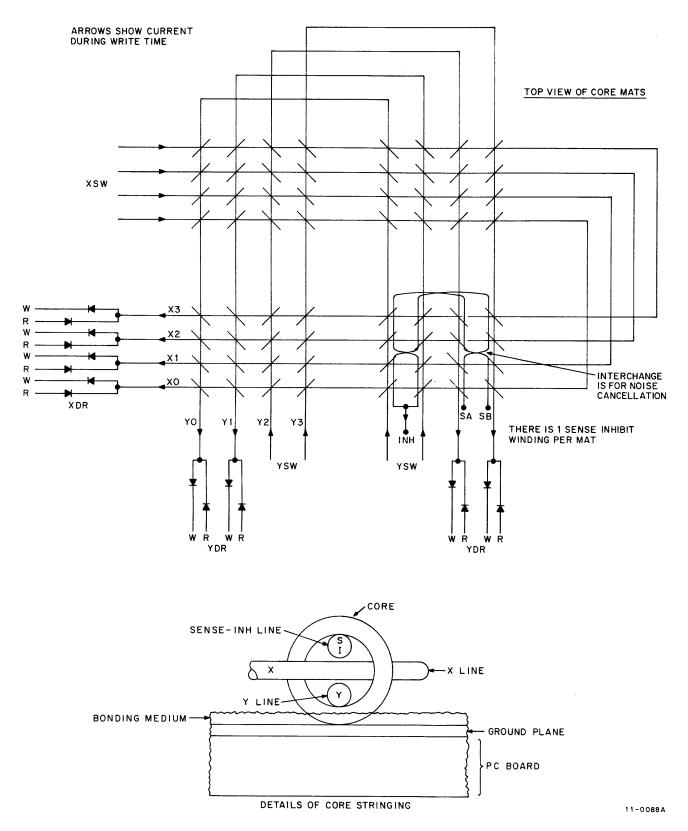

| 2-1        | Three-Wire Memory Configuration                                                  | 2-2  |  |

| 2-2        | Hysteresis Loop for Core                                                         | 2-4  |  |

| 2-3        | Three-Wire 3D Memory, Four Mats Shown for a 16-Word - 4-Bit Memory               |      |  |

| 2-4        | Device and Word Address Selection Logic,<br>Block Diagram                        |      |  |

| 2-5        | Memory Organization for 8K Words                                                 | 2-9  |  |

| 2-6        | Address Assignments For Three Banks of 8K<br>Words Each                          | 2-11 |  |

| 2-7        | Jumper Configuration For A Specific<br>Memory Address                            | 2-13 |  |

| 2-8        | Device Decoding Guide                                                            | 2-15 |  |

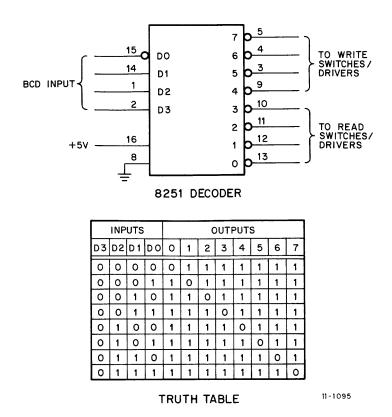

| 2-9        | Type 8251 Decoder, Pin Designation and Truth Table                               | 2-18 |  |

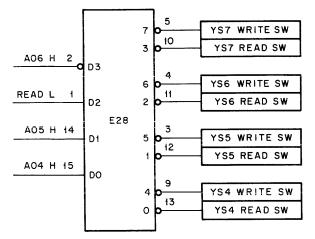

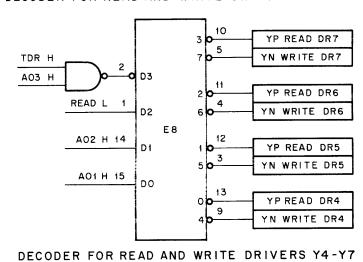

| 2-10       | Decoding of Read/Write Switches and Drivers Y4–Y7                                |      |  |

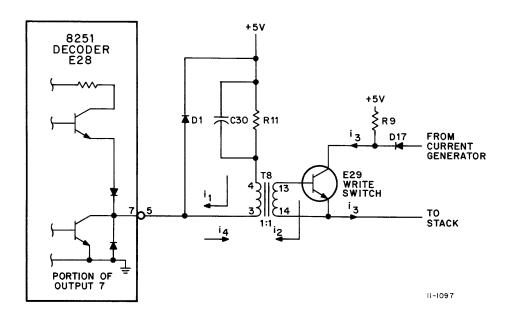

| 2-11       | Switch or Driver Base Drive Circuit                                              | 2-20 |  |

| 2-12       | Y-Line Selection Stack Diode Matrix                                              | 2-22 |  |

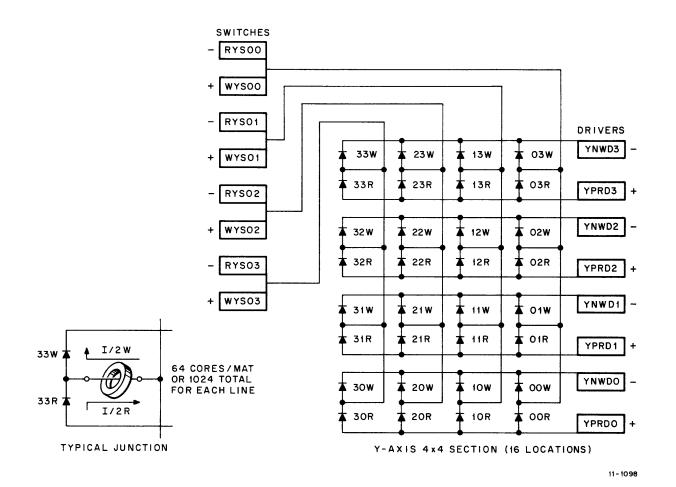

| 2-13       | Typical Y-Line Read/Write Switches and Drivers                                   | 2-23 |  |

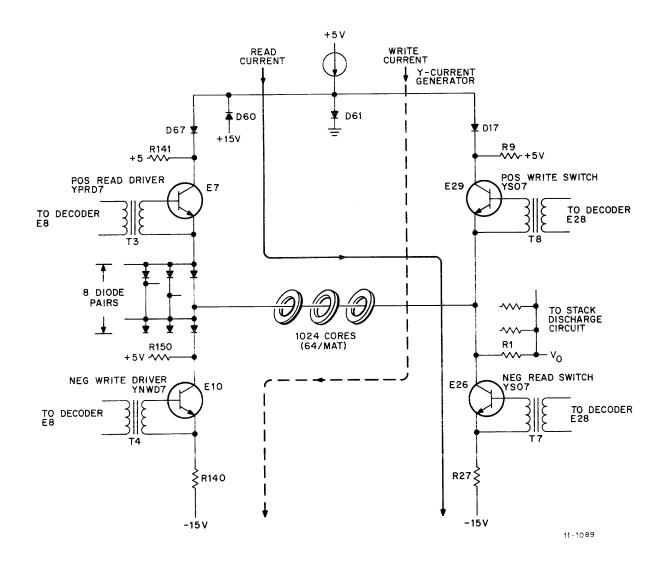

| 2-14       | Interconnection of Unibus, Data Register,<br>Sense Amplifier, and Inhibit Driver | 2-27 |  |

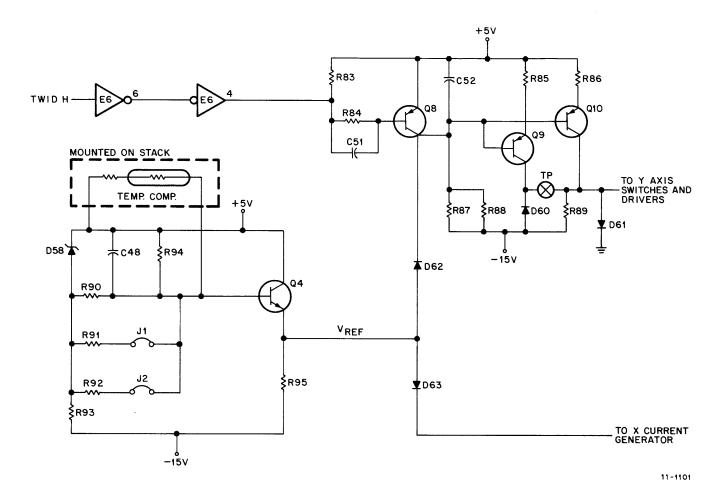

| 2-15       | Y-Current Generator and Reference<br>Voltage Supply                              | 2-30 |  |

| 2-16       | Sense Amplifier and Inhibit Driver                                               | 2-31 |  |

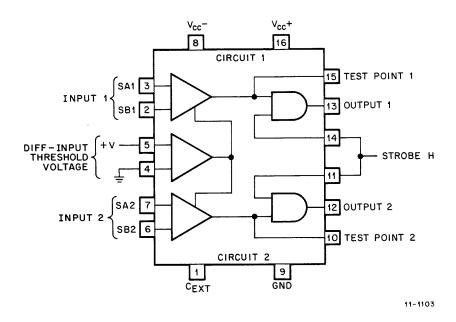

| 2-17       | Type 7528 Dual Sense Amplifiers With Preamplifier Test Points                    | 2-34 |  |

| 2-18       | Stack Discharge Circuit                                                          | 2-35 |  |

| 2-19       | DC LO Circuit, Schematic Diagram                                                 | 2-37 |  |

| 2-20       | Basic Timing and Control Signal Functions                                        | 2-41 |  |

| 2-21       | TWID H and TNAR H Control Logic                                                  | 2-44 |  |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                    | Page         |  |  |

|------------|----------------------------------------------------------|--------------|--|--|

| 2-22       | Generation of MSEL RESET L                               | 2-46         |  |  |

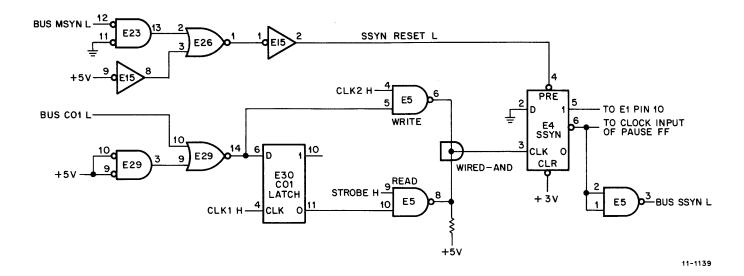

| 2-23       | Slave Sync (SSYN) Circuit                                | 2-48         |  |  |

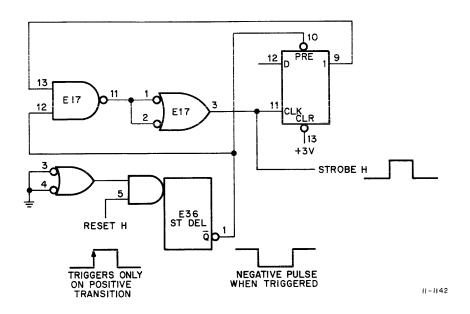

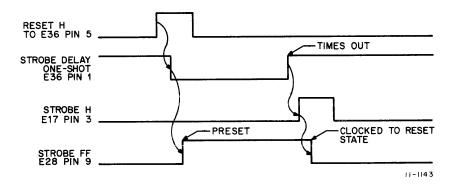

| 2-24       | Pause/Write Restart Circuit                              | 2-51         |  |  |

| 2-25       | Strobe Generating Circuit                                | 2-53         |  |  |

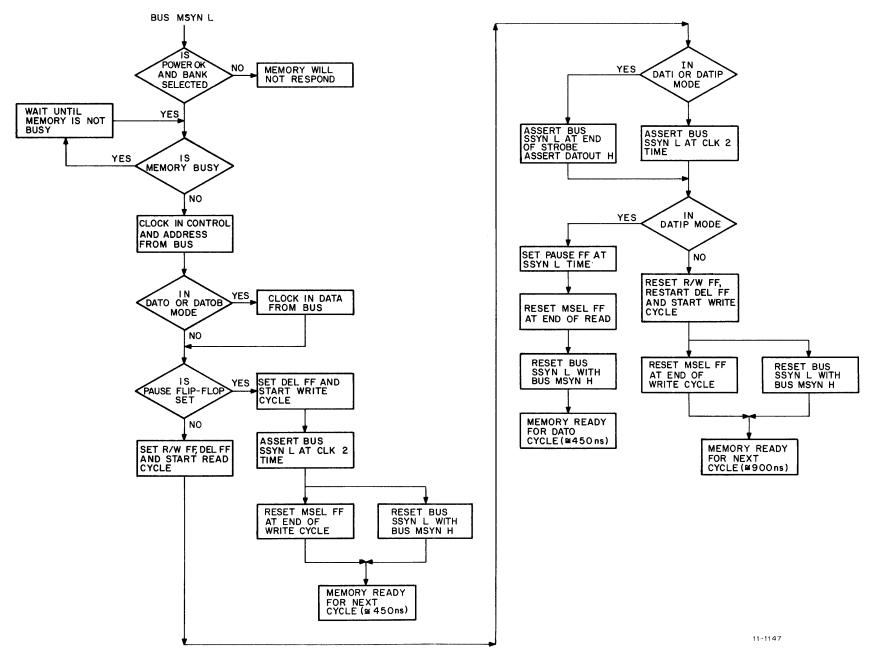

| 2-26       | Flow Chart For Memory Operation                          | 2-56         |  |  |

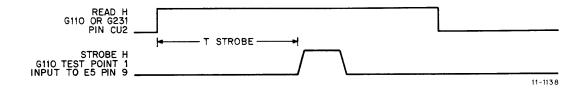

| 3-1        | Strobe Pulse Waveform                                    | 3-3          |  |  |

| 3-2        | Troubleshooting Chart                                    | 3-5          |  |  |

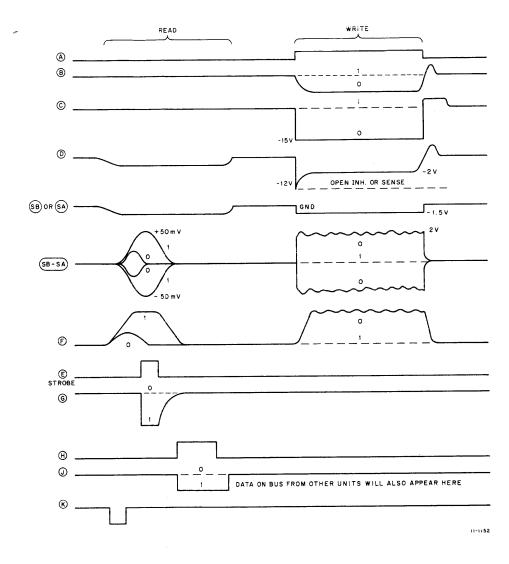

| 3-3        | MM11-K Sense/Inhibit Waveforms                           | 3 <b>-</b> 7 |  |  |

|            | PART 4-POWER SUPPLY                                      |              |  |  |

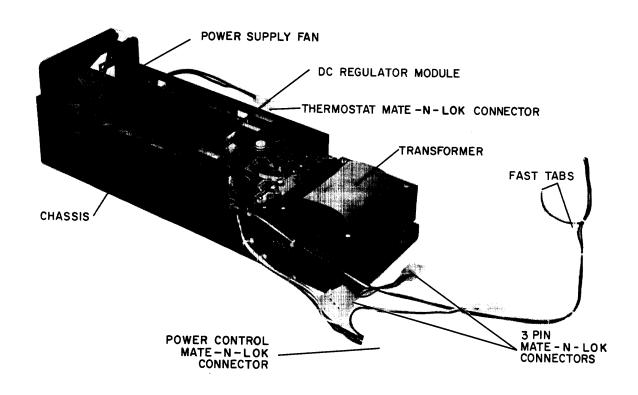

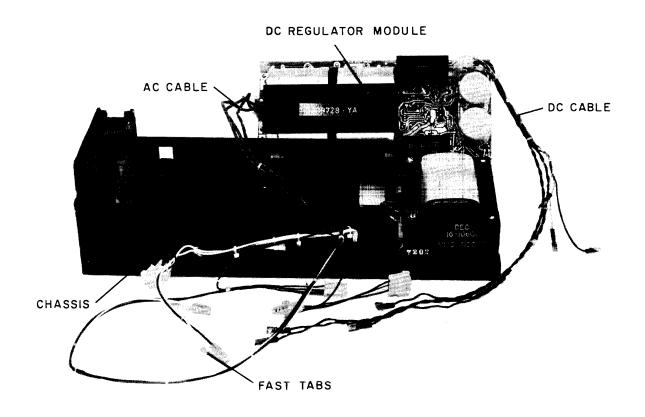

| 1-1        | Power Chassis Assembly (With DC<br>Regulator Module)     | 1-4          |  |  |

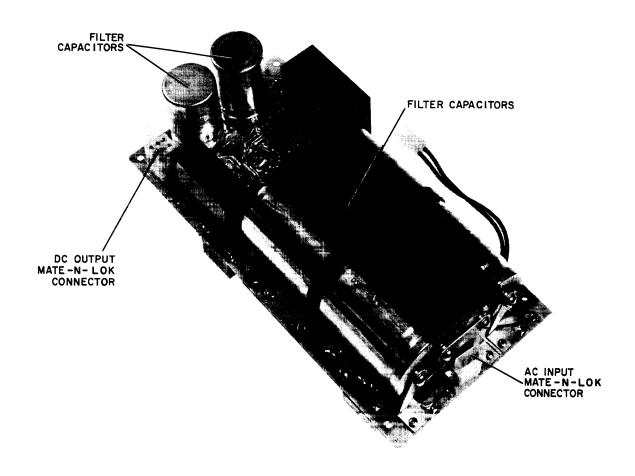

| 1-2        | Power Supply Assembly (With DC Regulator Module Removed) | 1-5          |  |  |

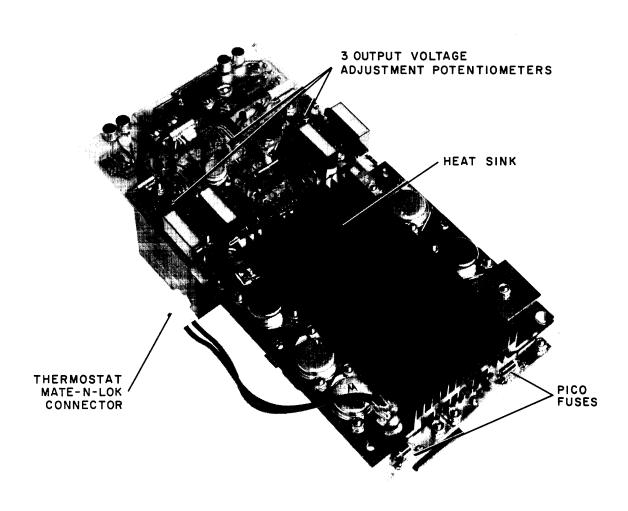

| 1-3        | DC Regulator Module (Top View)                           | 1-6          |  |  |

| 1-4        | DC Regulator Module (Bottom View in Mounting Box)        | 1-7          |  |  |

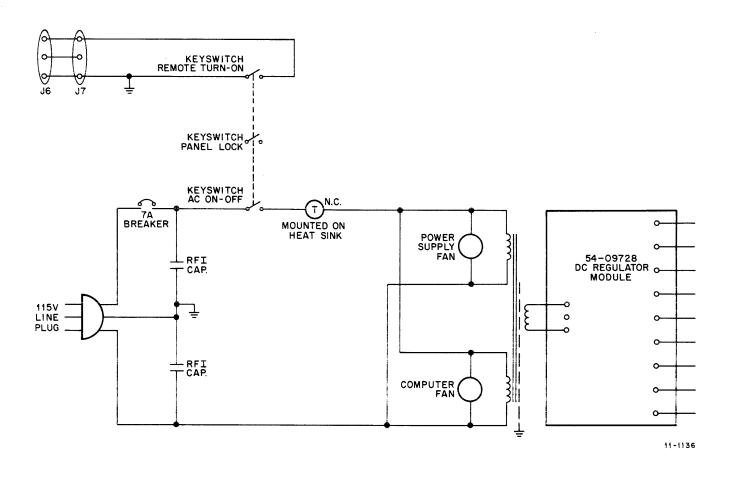

| 2-1        | Detailed AC Interconnection Diagram                      | 2-2          |  |  |

| 2-2        | 115V Connections – Simplified Schematic<br>Diagram       | 2-3          |  |  |

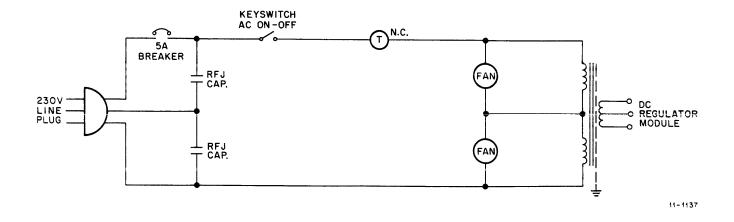

| 2-3        | 230V Connection Diagram                                  |              |  |  |

| 2-4        | Regulator Module Block Diagram                           | 2-5          |  |  |

| 2-5        | Rectifier and LTC L Circuits                             | 2-7          |  |  |

| 2-6        | BUS AC LO and BUS DC LO Circuits                         |              |  |  |

| 2-7        | +15V Regulator Circuit                                   |              |  |  |

| 2-8        | +5V Regulator Circuit                                    | 2-10         |  |  |

| 2-9        | -15V Regulator Circuit                                   | 2-13         |  |  |

| 3-1        | +5V Regulator Circuit Waveforms                          | 3-3          |  |  |

| 3-2        | -15V Regulator Circuit Waveforms                         | 3-4          |  |  |

| A          | INTEGRATED CIRCUIT (IC) DESCRIPTIONS                     | A-1          |  |  |

| В          | ` '                                                      |              |  |  |

| C          | COMPUTER CONNECTORS                                      | B-1<br>C-1   |  |  |

| D          | INTERFACE CIRCUITS AND HARDWARE                          | D-1          |  |  |

| <u> </u>   | HAILM ACE CINCOHO AIND HANDWANE                          | D- 1         |  |  |

This manual describes the PDP-11/05 and PDP-11/10 Computers. The PDP-11/05 and PDP-11/10 are electrically identical. The PDP-11/05 is specified for the Original Equipment Manufacturer (OEM) market and the PDP-11/10 is specified for the end user market.

The PDP-11/05 is available in two versions: one provides a maximum of 8K words of core memory and the other provides a maximum of 16K words of core memory. The PDP-11/10 is available only with a maximum of 8K words of core memory.

This manual is divided into four parts.

| Part 1 | Computer Description    |

|--------|-------------------------|

| Part 2 | KD11-B Processor        |

| Part 3 | MM11-K, MM11-L Memories |

| Part 4 | Power Supply            |

Chapter outlines of each part are shown below.

# Part 1 COMPUTER DESCRIPTION

Chapter 1 Computer Components

Chapter 2 Unibus

Chapter 3 Unpacking and Installation

Chapter 4 Operation

## Part 2 KD11-B PROCESSOR

Chapter 1 General Description

Chapter 2 Instruction Set

Chapter 3 Console Description

Chapter 4 Detailed Description

Chapter 5 Microprogram Control

Chapter 6 Maintenance

# Part 3 MM11-K, MM11-L MEMORIES

Chapter 1 General Description

Chapter 2 Detailed Description

Chapter 3 Maintenance

## Part 4 POWER SUPPLY

Chapter 1 General Description

Chapter 2 Detailed Description

Chapter 3 Maintenance

A bound volume of engineering drawings is supplied with each computer.

The following related documents are valuable as references.

PDP-11/05, 11/10 Processor Handbook

PDP-11 Peripherals and Interfacing Handbook

PDP-11 Paper-Tape Software Programming Handbook (Document No. DEC-11-GGPB-D)

PART 1

Computer Description

CHAPTER 1

COMPUTER COMPONENTS

## 1.1 INTRODUCTION

This chapter briefly describes the major components of the computer. It includes module utilization diagrams for both computer configurations and a backplane connector and pin designation diagram.

## 1.2 COMPUTER COMPONENTS

The computer consists of a mounting box, console, processor, core memory, prewired back-plane, power supply, fans, and interconnecting cables. The processor is contained on two modules, and each 4K or 8K memory is contained on three modules.

# 1.2.1 KD11-B Processor

The processor modules are M7260 Data Paths and M7261 Control Logic and Microprogram. They are hex height modules and measure 8 1/2 in. long x 15 in. high. A hex height module contains six edge-connectors (A-F).

All the processor functional components are contained on these modules, as shown below.

The M7260 Data Path Module contains:

Data path logic

Processor status word logic

Auxiliary arithmetic logic unit control

Instruction register and decoding logic

Serial communications line interface

# The M7261 Control Logic and Microprogram Module contains:

Internal address detecting logic

Stack control logic

Unibus control logic

Priority arbitration logic

Unibus drivers and receivers

Micro branch logic

Micro program counter

Control store logic

Power fail logic

Line clock

Processor clock

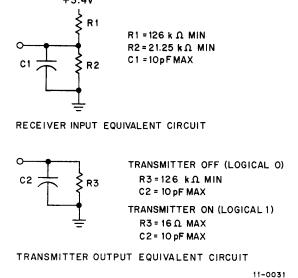

The serial communications line (SCL) interface is directly connected to the desired serial communications device. It can operate at speeds of 110-300 baud and is program compatible with the KL11 Teletype Control Interface option. The SCL is compatible with the LA30 DECwriter at 30 characters per second, the VT05 Alphanumeric CRT Display Terminal at 30 characters per second, and the Teletype Model 33 ASR at 10 characters per second.

The line time clock (LTC) allows the program to measure time by sensing the 50 Hz or 60 Hz ac line frequency. This clock is program compatible with the KW11-L Line Time Clock option.

The line time clock and the serial communications line interface are not connected to the Unibus. They use an internal bus and can be addressed only by the processor and the console.

## 1.2.2 Core Memory

The PDP-11/05 is available in two versions: one provides a maximum of 8K words of core memory and the other provides a maximum of 16K words of core memory. The PDP-11/10 is available only with a maximum of 8K words of core memory. A separate add-on core memory system (ME11-L) is available to provide an additional 8K, 16K, or 24K words of core memory. A PDP-11/05 or PDP-11/10 processor provides program control for a maximum of 32K words of memory; therefore, the self-contained memory plus the ME11-L must not be greater than 32K words.

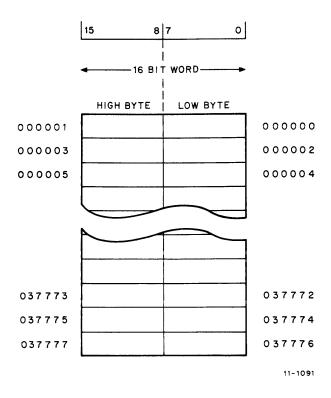

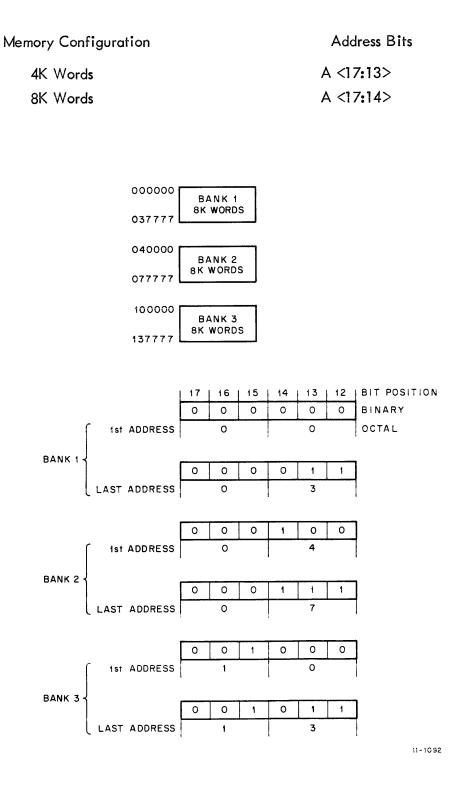

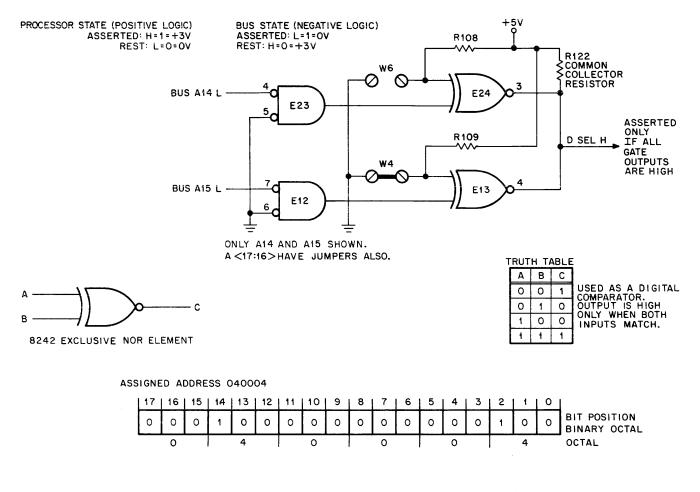

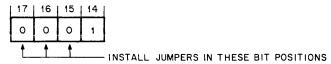

1.2.2.1 Memory Organization - The memory is organized in 16-bit words consisting of two 8-bit bytes. The bytes are identified as low and high. The memory contains 8192 words or 16,384 bytes; therefore, 16,384 locations are assigned. The address locations are specified as 6-digit octal numbers. The 16,384 locations for the 8K memory are designated 000000 through 037777.

Each byte is addressable and has its own address location: low bytes are even numbered and high bytes are odd numbered. Words are addressed at even numbered locations only, and the high (odd) byte is automatically included. Consecutive words are therefore found in even numbered addresses.

The PDP-11 address word contains 18 bits A <17:00>, which provides the capability of addressing 262,144 (256K) locations (bytes) or 131,072 (128K) words. The basic processor provides 16 bits (A <15:00>) of address information, which handles 65,536 (64K) bytes or 32,768 (32K) words. During an addressing operation, if bits A <15:13> are all 1s, bits A <17:16> are forced to 1s, which relocates the last 8K bytes (4K words) to become the highest locations accessed by the bus. These top 4,096 word locations are reserved for peripheral and register addresses, and the user therefore has 28,672 (28K) words of memory to program.

1.2.2.2 Memory Specifications - The core memory is a read/write, random access, coincident current type with a cycle time of 900 ns and an access time of 400 ns. It is organized in a 3D, 3-wire planar configuration. Word length is 16 bits, and the memory is offered in two word capacities: model MM11-K contains 4096 words and model MM11-L contains 8192 words. Each memory is contained on three modules called the control, driver, and stack. For the MM11-K memory, the stack module is H213; H214 is the stack module for the MM11-L memory. The G110 Control Module and the G231 Driver Module are the same for both models.

# 1.2.3 Power Supply

The power supply consists of a dc regulator module, transformer, and fan, mounted in a chassis. It is installed in the computer mounting box. The power supply converts 115V or 230V, 47-63 Hz line voltage to three regulated dc voltages that are used by the processor, memory, and optional modules. The regulated voltages are:

+5V at 17A -15V at 6A +15V at 1A

An associated component, the power control, provides the ac line voltage to the power supply and cooling fans. The power control is installed in the rear panel of the computer mounting box. It consists of a line cord, circuit breaker, and output connector, A model is available for each of the two line voltages (115V or 230V), as shown below.

| Part Number | <u>Rating</u>       |  |  |

|-------------|---------------------|--|--|

| BC05H       | 7A at 115V/47-63 Hz |  |  |

| BC05J       | 4A at 230V/47-63 Hz |  |  |

The power supply provides three additional outputs. Signal LTC L is the Line Time Clock signal that drives the line time clock. The BUS AC LO L and BUS DC LO L signals actuate the processor power fail-auto restart circuitry.

# 1.2.4 Backplane

The backplane is a connector assembly into which the computer modules are plugged. It provides interconnections between the Unibus, processor, memory, and optional modules. The interconnections are made via a printed circuit board and wirewrapped pins that are part of the backplane assembly.

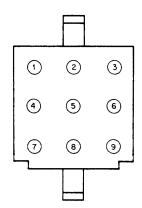

There are two versions of the computer (8K memory and 16K memory). The backplane is wired differently for each version. As a result, the modules must be installed in specific locations as shown in Figure 1-1 for the 16K version and Figure 1-2 for the 8K version. These illustrations show the backplane as viewed from the module side. The slots are numbered 1 through 9 from top to bottom, and the connectors are lettered A through F from left to right.

Configuration 1 is the 16K version (Figure 1-1). Unibus M930 Terminator Modules are installed in slots A2-B2 and A5-B5. If other peripherals are to be connected to the computer, the terminator module in slot A2-B2 must be replaced with a BC11A Unibus cable, and a terminator module must be installed in the last device in the system. Slot C1-F1 provides the only space for a small peripheral controller. If this slot is not used, a G727 Grant Continuity Module must be installed in slot D1. If a small peripheral controller is

to be installed, the G727 module must be removed first. Slots A1 and B1 are wired for the KM11 Maintenance Module. The core memories (3 modules each) are physically interchangeable as systems.

Configuration 2 is the 8K version (Figure 1-2). Unibus M930 Terminator Modules are installed in slots A3-B3 and A5-B5. If required, a BC11A Unibus cable can be installed in place of the terminator in slot A3-B3. Slots C1-F1, C2-F2, C3-F3, and C4-F4 can be used for small peripheral controllers. Slot A1-B1 is wired for a DF11 Communications Line Adapter that provides signal conditioning for communications devices using signals that are not TTL compatible. Slots A2 and B2 are wired for the KM11 Maintenance Module.

Figure 1-3 shows the backplane connector block configuration as viewed from the wirewrap pin side. The pin arrangement for each connector block is identical. It represents the total pins (36) available on the double-sided edge connector of a single height module. Connector A1 is shown in detail.

#### 1.3 ME11-L CORE MEMORY SYSTEM

Additional core memory is available for the computer in the ME11-L self-contained add-on core memory system. The basic ME11-L consists of an 8K MM11-L memory and power supply installed in a mounting box. It is expandable to 16K words or 24K words maximum by adding one or two more MM11-L memories. The ME11-L uses the same backplane construction as the computer. Nine slots are provided, and they are wired to accommodate three MM11-L memories. These core memories (3 modules each) are physically interchangeable as systems and as individual modules within a system for troubleshooting purposes. If only one memory is used, the modules must be installed in the three bottom slots (numbers 7, 8, and 9).

### 1.4 EXTENSION MOUNTING BOX

Additional interface logic for the computer is installed in an extension mounting box identical to those used for the rest of the PDP-11 Family. A rack-mounted box (BA11-ES) or a tabletop box (BA11-EC) can be used. The mounting box contains cooling fans, filter, and power cord. Space is provided to install six system units and an H720 Power Supply. Details of the extension mounting box, system units, and H720 Power Supply are included in the PDP-11 Peripherals and Interfacing Handbook.

Figure 1-1 Module Utilization Diagram For Configuration 1 (16K)

Figure 1-2 Module Utilization Diagram For Configuration 2 (8K)

Figure 1-3 Computer Backplane Connector and Pin Designations

## 2.1 INTRODUCTION

This chapter describes in general the operation of the Unibus.

The following documents, in conjunction with this manual, will aid the reader in understanding interface techniques and the overall PDP-11 system.

- a. PDP-11/05-11/10 Processor Handbook

- b. PDP-11 Peripherals and Interfacing Handbook

- c. Digital Logic Handbook

All communication between PDP-11 system components is through the high-speed Unibus. The Unibus operational concepts are vital to the understanding of the hardware and software implications of the Unibus.

#### 2.2 UNIBUS STRUCTURE

The Unibus is a single, common path that connects the processor, memory and all peripherals. Addresses, data, and control information are transmitted along the 56 lines of the bus.

Every device on the Unibus employs the same form of communication; thus, the processor uses the same set of signals to communicate with memory and with peripheral devices.

Peripheral devices also communicate with the processor, memory, or other peripheral devices via the same set of signals.

All instructions applied to data in memory can be applied equally well to data in peripheral device registers, enabling peripheral device registers to be manipulated by the processor with the same flexibility as memory. This feature is especially powerful, considering the capability of PDP-11 instructions to process data in any memory location as though it were an accumulator.

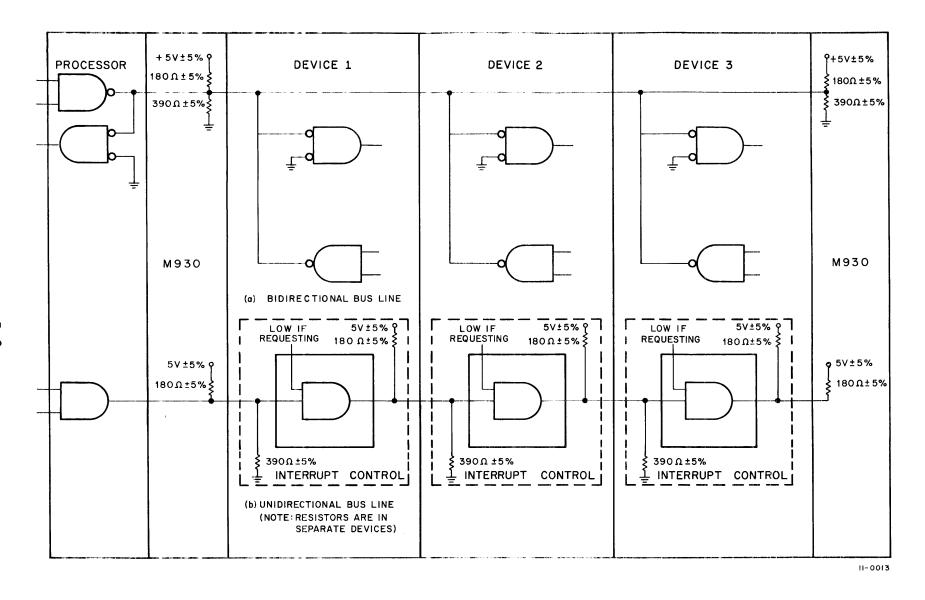

#### 2.2.1 Bidirectional Lines

Most Unibus lines are bidirectional, allowing input lines to also be driven as output lines. This is significant in that a peripheral device register can be either read or can be used for transfer operations. Thus, the same register can be used for both input and output functions.

## 2.2.2 Master-Slave Relationship

Communication between two devices on the bus is a master-slave relationship. During any bus operation, one device has control of the bus. This device, the bus master, controls the bus when communicating with another device on the bus, the salve. A typical example of this relationship is the processor, as the master, transferring data to memory, as slave. Master-slave relationships are dynamic. The processor, for example, passes bus control to a disk. The disk, as master, then communicates with a slave memory.

The Unibus is used by the processor and all I/O devices; thus, a priority structure determines which device gains control of the bus. Consequently, every device on the Unibus capable of becoming bus master has an assigned priority. When two devices capable of becoming bus master have identical priority values and simultaneously request use of the bus, the device that is electrically closest to the bus receives control.

#### 2.2.3 Interlocked Communication

Communication on the Unibus is interlocked between devices. Each control signal issued by the master device must be acknowledged by a response from the slave to complete the transfer. Consequently, communication is independent of the physical bus length and the response time of the master and slave devices. The maximum transfer rate on the Unibus, with optimum device design, is one 16-bit word every 400 ns or 2.5 million 16-bit words per second.

## 2.3 PERIPHERAL DEVICE ORGANIZATION AND CONTROL

Peripheral device registers are assigned addresses similar to memory; thus, all PDP-11 instructions that address memory locations can become I/O instructions, enabling data registers in peripheral devices to take advantage of all the arithmetic power of the processor.

The PDP-11 controls devices differently than most computer systems. Control functions are assigned to a register address, and then the individual bits within that register can cause control operations to occur. For example, the command to make the paper-tape reader read a frame of tape is provided by setting a bit (the reader enable bit) in the control register of the device. Instructions such as MOV and BIS may be used for this purpose. Status conditions are also handled by the assignment of bits within this register, and the status is checked with TST, BIT, and CMP instructions.

## 2.4 UNIBUS CONTROL ARBITRATION

The Unibus is capable of performing two basic and parallel tasks in order to allow transfers by multiple peripherals at maximum speed. The first is the actual transfer of data between the current bus master and its addressed slave. The second is the selection of the next bus master, the peripheral which, as soon as the bus becomes free, will be allowed to assert control. It is important to note that the granting of future mastership is in no way influenced by either the current master or its method of obtaining the bus. It is this fact which allows these functions to be performed in parallel and allows transfers on the bus at a maximum rate.

# 2.4.1 Priority Transfer Requests

To gain mastership of the Unibus, a peripheral must first make a request to the processor for the bus and then wait for its selection. The processor contains the logic necessary to arbitrate these requests because normally there are several requests pending at any given time.

There are two classes of requests: Bus Requests and Non Processor Requests. A Bus Request (BR) is simply a request by a peripheral to obtain control of the Unibus with the understanding by the processor that the peripheral may end its use of the bus with a processor interrupt. An interrupt is a command to the processor to begin executing a new routine pointed to by a location selected by a device. A Non Processor Request (NPR) is similarly a request for the bus, but with the exception that it may not interrupt the processor. Since the granting of an NPR cannot affect the execution of the processor, it can occur during or between instructions. BRs however, by possibly causing execution to be diverted to a totally new routine, can only be granted between instructions. In this way, NPRs are assigned priority over any BR.

Between Bus Requests, there are four levels of priority created by four separate requests lines. These are assigned priority levels 4 through 7. BR4 is the lowest and BR7 is the highest. These levels are associated with the program controlled priority level of the processor controlled by bits 7, 6, and 5 of the processor status register. Only BRs on a priority level higher than the level of the processor are eligible for receiving a bus grant. Thus, during high priority program tasks, all or selected Unibus requests (hence interrupts) can be inhibited by raising the level of the processor priority.

Another form of priority arbitration occurs through the system configuration. When the processor grants a request, the grant travels along the bus until it reaches the first requesting device which terminates the grant. Therefore, along the same grant line, the device electrically nearest the processor has the highest priority. Also note that in the KD11-B, the internal line clock is logically the last device on BR6, and the serial communication line interface is logically the last device on BR4.

After a requesting device receives a bus grant it asserts its selection as next bus master until the bus is free, thus inhibiting other requests from being granted. When the bus becomes free, the selected device asserts control of the bus and relinquishes its selection as next bus master so that the priority arbitration among pending requests may continue.

# 2.4.2 Processor Interrupts

After gaining control of the bus through a BR, a device can perform one or more transfers on the bus and/or request a processor interrupt. This is typically requested after a device has completed a given task, for instance typing a character or completing a block data transfer through NPRs. If a peripheral wishes to interrupt the processor, it must assert the interrupt after gaining control of the bus but before relinquishing its selection as next bus master. Thus the processor knows that it still shouldn't continue to fetch the next instruction, but must wait for the interrupt to be completed. Along with asserting the interrupt, the device asserts the unique memory address, known as the interrupt vector address, containing the starting address of the device service routine. Address vector +2 contains the new PSW to be used by the processor when beginning the service routine. After recognizing the interrupt, the processor reads the vector address and saves it in an internal register. It then pushes the current PSW and program counter onto the stack and loads the new PC and PSW from the vector address specified. The service routine is then executed.

#### NOTE

These operations are performed automatically and no device polling is required to determine which routine to execute.

The device service routine can cause the processor to resume the interrupted process by executing the return from interrupt, RTI, instruction which pops the top two words from the processor stack and transfers them back to the PC and PS registers.

## 2.4.3 Data Transfers

After asserting control of the Unibus, the device does not release control until it has completed either one or more data transfers or an interrupt. Typically, only one transfer is

completed each time the device gains control of the bus because few single devices can give or receive information at the maximum Unibus rate. Holding the bus for multiple transfers inhibits other devices from using the bus.

A transfer is initiated by the master device asserting a slave address and control signals on the bus and a master or address validity signal. The appropriate slave recognizes the valid address, reads or writes the data, and responds with a transfer complete signal. The master, recognizes the transfer complete, sends or accepts data and drops the address validating signal. It then can assert a new address and repeat the process or release control of the bus completely.

The importance of this type of structure is that it enables direct device to device transfers without any interaction from the central processor. An NPR device, such as a high speed CRT display, can gain fast access to the bus and transfer data at high rates while refreshing itself from memory without slowing down the processor.

#### 3.1 INTRODUCTION

The computer is shipped ready to operate in either a protective box or a 19-inch cabinet. Unless required by peripherals, there are no special shipping mounts internal to the computer. Prior to final electrical testing each computer is thermal cycled, vibrated, and subjected to mechanical shock with all modules in place.

Basic computers are shipped in the package illustrated in Figure 3-1. Sufficient hardware is included in the shipping carton to rack mount the computer.

#### 3.2 UNPACKING

The basic computer should be carefully removed from its box. Slide mounts are attached to the computer, but mounting screws are packed in a bag located in the same box. Also included is one 83600 SCL (Serial Communication Line) cable and two keys for the console lock. The 83600 SCL cable has a Berg 127009-0, 40-pin connector on one end that matches the SCL output connector on the computer. The other end of the 83600 SCL cable terminates in a Mate-N-Lock 1209340 that matches that used on the VT05, LA30, and ASR Teletype Model 33.

If the computer was ordered as a system with options requiring small peripheral controllers, the controllers may be inside the computer box. Small peripheral controllers are used to interface options such as line printers and paper-tape reader/punches as well as to implement programmable clocks and bootstrap loaders.

Figure 3-1 Computer Packaging

After removing the computer from its package, it should be inspected for damage. It is advisable to save the packing carton in case it is necessary to return the unit for service.

#### 3.3 MECHANICAL DESCRIPTION

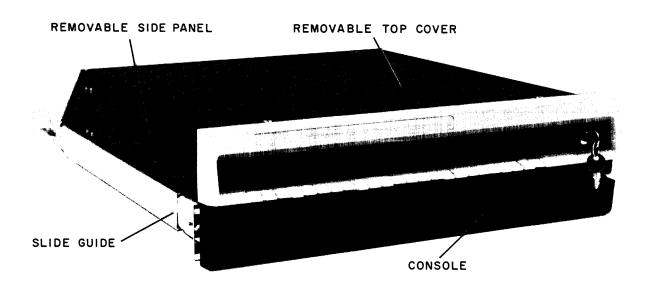

Figure 3–2 illustrates the 5–1/4 by 19 by 20 inch computer mounting box, including rack-mountable slide and console. The removable top cover of the mounting box is fastened by four Cam-Lock screws. The removable side panel is fastened by four Phillips-head screws.

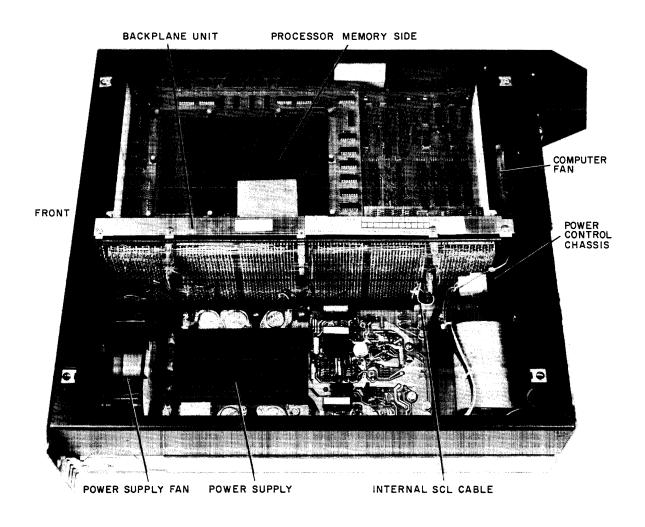

Figure 3–3 shows the mounting box with the top cover removed. The backplane unit divides the power supply from the memory and processor side of the mounting box. The internal SCL cable runs from the backplane under the power supply unit to the rear of the mounting box.

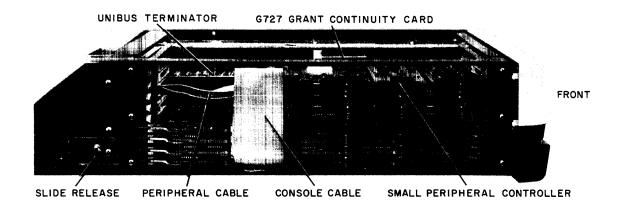

Figure 3-4 depicts the mounting box with top cover and side panel off, and the processor and memory modules plugged in. In this case, the computer is a Configuration 2 machine, using an MM11-L, 8K memory unit. Three small peripherals are shown with the external cables attached. A G727 Grant Continuity Card is in the top peripheral slot and a M930 Unibus Terminator Card is in slot A3, B3 (Figure 3-6 also). In Figure 3-5, the Unibus cable is in place, replacing the Unibus terminator card.

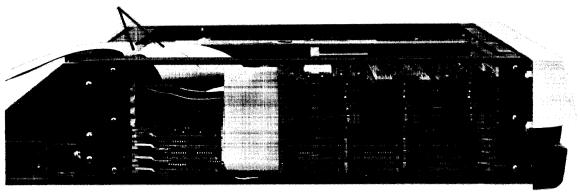

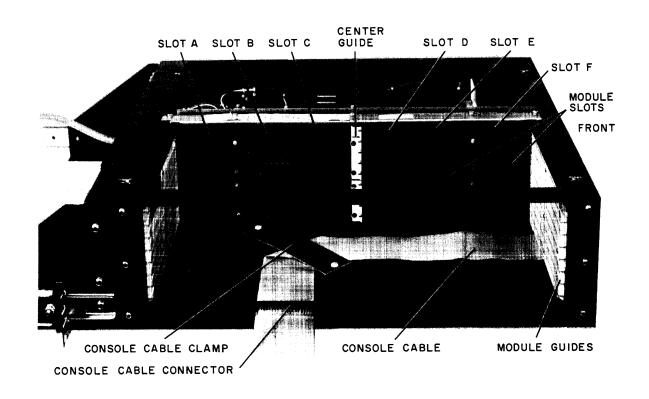

Figure 3–6 shows the mounting box without any modules. The path of the console cable is under the M7260 Processor Module. The cable then comes over to plug into the top of the M7260. The module guides aid in inserting the modules into the proper slots.

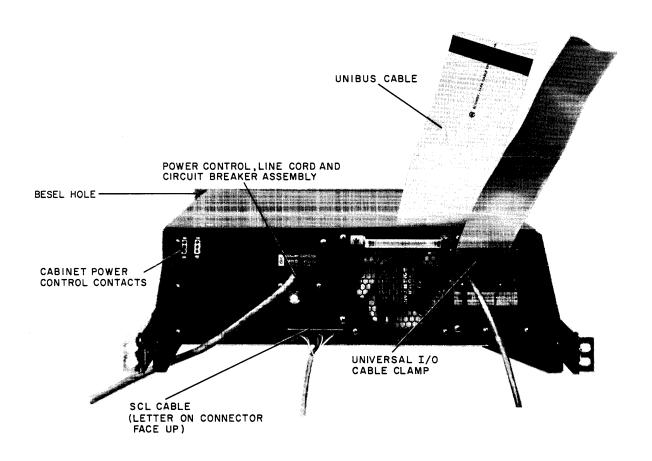

Figure 3–7 is a rear view of the mounting box with attached rack-mountable slides. If the computer contains any peripheral controllers outside the mounting box, the Unibus is extended from under the top cover. The power control circuit breaker protects the power supply from overload. It is rated at 7A for 110 V units or 4A on 230 V. The SCL connector and ac remote power control connectors are also shown.

Figure 3-2 Computer Mounting Box

Figure 3-3 Computer Box With Top Cover Removed

Figure 3-4 Computer Box with Top and Side Covers Removed

UNIBUS CABLE AND UNIBUS CABLE CLAMP

Figure 3–5 Computer Chassis (showing both peripheral cables and the Unibus)

Figure 3-6 Mounting Box Without Modules

Figure 3-7 Rear of Computer Showing Cable Strain Reliefs

#### 3.4 INSTALLATION

The computer mounts in a standard 19-inch wide by 20-inch deep equipment bay. The computer is mounted on slides for easy service. To mount the unit, first attach the fixed portion of the slides to the cabinet; the fixed portion of the slides can be removed from the computer by actuating the slide release shown in Figure 3-4.

Be sure to mount the slides so that the fixed guides are parallel and level with the ground.

## 3.4.1 Mounting Computer on Installed Slides

Once the slide guides have been securely fastened in the cabinet using all eight screws, lift the computer and slide it carefully onto the slide guides until the slide release locks. Carefully lift the slide release and push the computer fully into the rack, being careful not to tear any existing cabling.

The computer should then be fully extended until the slide release locks. As shown in Figure 3-4, the panel on the module side of the computer should be removed to permit installation of I/O cables and the Unibus if required. The panel is removed by loosening and removing four Phillips-head screws.

### 3.4.2 Securing Computer to Cabinet Rack

If the rack-mounted computer is used in a moving environment, it must be secured to the cabinet rack to prevent the machine from moving on its slides. This option, if desired, is implemented as follows:

- Remove the console bezel from the computer by removing the four screws at the rear of the bezel, being careful not to tear the cable that connects the console and processor.

- 2. Drill the partial 7/32 inch holes at each top inside corner of the bezel through from the rear of the bezel (Figure 3-7).

- 3. Counter-bore the 7/32 inch holes at the front of the console bezel 1/2 inch in diameter.

- 4. Replace the console bezel.

- 5. Use two 10-32 x 2 inch Phillips-head screws and two Tinnerman nuts to secure the computer to the cabinet rack through the bezel holes at the desired rack position.

- 6. To make the 10-32 x 2 inch Phillips-head screws captive, notch a 1/8 inch long segment in each 10-32 x 2 inch Phillips-head screw just above the threads and insert a 1/8 I.D. O-Ring in each notch.

#### 3.4.3 Installation of I/O Cables

Flat and round I/O cables should be fed through the Universal I/O cable clamp shown in Figure 3-6 for strain relief. They should then be connected to the appropriate small peripheral controllers. Note that the strain relief clamp prevents tension on the cables from damaging the connector block inside the computer. The wide Unibus cable, if required, should be folded as shown in Figure 3-5 and routed over and through a clamp attached to the top of the fan as shown in Figure 3-7. Note that there is a guide extending from the fan that prevents the Unibus cable from blocking air flow to the computer.

As shown in Figure 3-4, systems in which the Unibus is terminated in the computer box must have an M930 Terminator Card in slot A3-B3 as well as slot A5-B5.

#### 3.5 INTERCHANGEABLE PERIPHERAL SLOTS

Note that the four peripheral slots in Configuration 2 are identical; therefore, it is possible to arrange the small peripheral controllers for the best mechanical convenience. For instance, if it is necessary to diagnose a failure in a small peripheral controller, it may be convenient to place the selected option in the top slot where its components will be exposed.

#### 3.6 SIDE AND TOP COVER INSTALLATION

Figures 3-4 and 3-5 show the computer ready for installation of the side cover. Note that the console cable is folded into a flat loop in order to clear the side cover. Attached to the side cover is the continuation of the left-hand slide. All four 8-32 screws that hold the cover in place should be inserted and tightened securely. The top cover can now be installed using the four Cam-Lock screws.

#### 3.7 AC POWER SUPPLY CONNECTION

Computers designed for use on 115 Vac circuits are equipped with a three-prong connector, which when inserted into a properly wired 115 Vac outlet grounds the case of the computer. It is unsafe to operate the computer unless the case is grounded because normal leakage current from the power supply flows into metal parts of the chassis.

If the integrity of the ground circuit is questionable, the user is advised to measure the potential between the computer case and a known ground with an ac voltmeter.

## 3.7.1 Connecting to Voltages Other than 115V

The computer will operate at voltages ranging from 95V to 135V and from 190V to 270V (47 Hz - 63 Hz), providing the proper power control is attached to the computer. The computer is ordered for nominal voltages of 115V or 230V. The standard three-prong connector for 115V is identical with that found on most household appliances. A standard three-prong connector is also used for 230V.

On installations outside of the United States or where the National Electrical code does not govern building wiring, the user is advised to proceed with caution.

## 3.7.2 Quality of AC Power Source

The computer is a complex electronic device. Computer systems consisting of CPU, memory, and peripherals are often sensitive to the interference present on some ac power lines. If a computer system is to be installed in an electrically "noisy" environment, it may be necessary to condition the ac power line. DEC Field Service engineers can assist customers in determining if their ac line is satisfactory.

#### 3.8 CABINET POWER CONTROL

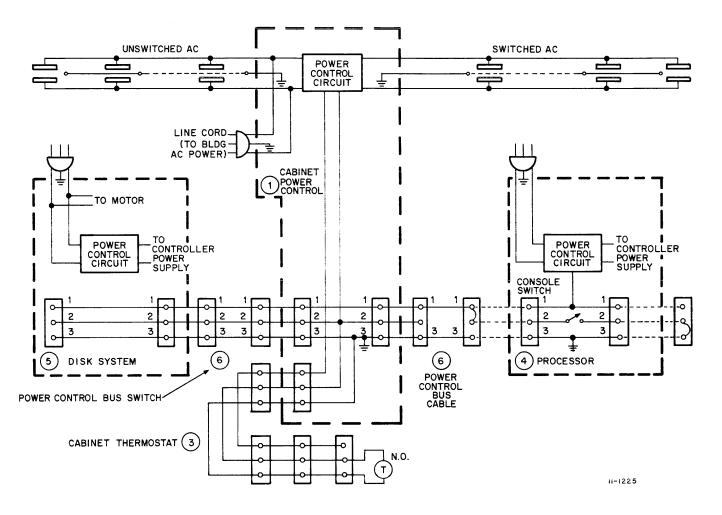

Provisions have been made for the computer switch to operate a cabinet power control.

This feature permits the computer key lock switch to control the power supply for peripherals

attached to the computer (refer to Part 4). The power control contacts are closed when the key lock switch is in the POWER or PANEL LOCK positions. The wiring diagram for a typical cabinet power control systems is shown in Figure 3–8. The power control contacts of the computer may be used to switch a maximum of 230V at 4A.

Figure 3-8 Typical Cabinet Power Control System Wiring Diagram

## 3.9 INSTALLATION CERTIFICATION

Once the computer has been installed, it is seriously recommended that a system diagnostic be run to ensure that the equipment operates correctly and that installation has been properly performed. Because system configurations widely vary, no one diagnostic will completely exercise all the attached devices.

It is recommended that the MAINDEC User's Manual that comes with the diagnostic package be consulted for the appropriate diagnostic to be run, depending upon the attached devices. The MAINDEC User's Manual lists the devices that each diagnostic will exercise. The three system exercisers presently available are T17 System Exerciser (MAINDEC-11-DZKAP) for relatively small systems, General Test Program (MAINDEC-11-DZQGA) for medium to large systems, and Communications Test Program (MAINDEC-11-DZQCA) for communications-oriented systems. At least one of the above diagnostics and, if appropriate, the other two, should be used to verify system operation.

Once the diagnostic is selected, the respective diagnostic write-up should be consulted for specific operating instructions. If the user is not familiar with console operation and/or procedures for loading paper tapes, he should read Part 1, Chapter 4, Operation of this manual.

## 3.10 WARRANTY SERVICE (Domestic Only)

If the machine is still covered under the 30 day return-to-factory warranty, and it is desired to return it for factory service, the following procedure should be used. If the machine is no longer on warranty, the local DEC Field Service office should be contacted.

- 1. Call the Maynard, Massachusetts Repair Depot, Telephone 617–897–5111, X4079 or X2135.

- 2. The caller will receive an RA (Return Authorization) number, which must appear on the shipping label of the package being returned.

- Package the machine in an equivalent shipping container, similar to the one the computer arrived in. If possible, use the original computer shipping container.

- 4. Send the machine to the following address:

Digital Equipment Corporation 146 Main Street Maynard, Massachusetts 01754 Atten: Depot Repair, Bldg. 21-4

RA # XXXX

#### 4.1 INTRODUCTION

This chapter assumes that the computer is installed and connected to the ac power line. It is also assumed that the reader has access to the appropriate diagnostic materials, and a copy of the absolute loader paper tape. It is further assumed that the user is using paper tapes to load software and diagnostics. For systems that have mass storage services, i.e., Disks or DEC tape, the user should refer to the appropriate software manuals for mass storage operating systems.

#### 4.2 POWER SWITCH OPERATION

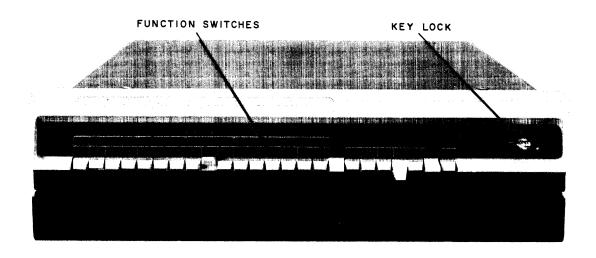

The key-lock power switch shown in Figure 4-1 has three positions.