## 2080 ENGINEERING FUNCTIONAL SPECIFICATION

Major edition: 3

Edit: 40

## COMPANY CONFIDENTIAL

This document contains confidential information on new products that should be disclosed only to those people engaged in the Program. Under no circumstances should any non-DEC persons be informed about any aspects of the Program or its existence.

This document should not be duplicated. Additional copies are available from:

Laura Chu MR1-2/E85 DTN # 231-6355

| This  | is    | copy |  |

|-------|-------|------|--|

| Issue | .a. 4 |      |  |

This specification is the property of Digital Equipment Corporation and must be surrendered upon termination of employment.

## CHAPTER 1

## INTRODUCTION

# 1.1 TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1.1 TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1                                                                                               |

| CHAPTER 2 SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |

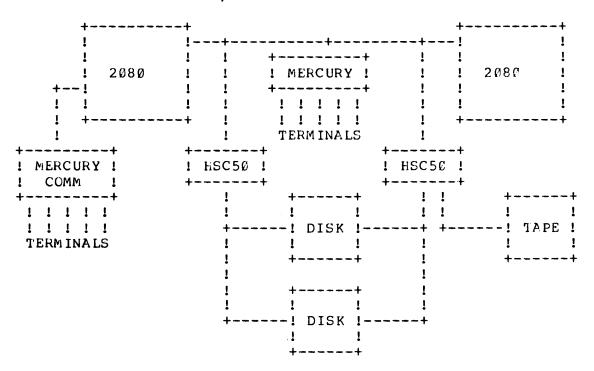

| 2.1 OVERVIEW  2.1.1 PRODUCT STRATEGY  2.1.2 CPU CLUSTER BLOCK DIAGRAM.  2.1.3 SYSTEM CONFIGURATIONS.  2.1.3.1 INITIAL SHIPMENTS.  2.1.3.2 TARGET SYSTEMS.  2.2 HARDWARE ORGANIZATION.  2.2.1 CONSOLE SUMMARY.  2.2.1.1 BOOTSTRAP.  2.2.1.2 OPERATOR SUPPORT.  2.2.1.3 DIAGNOSTIC SUPPORT.  2.2.2 IBOX SUMMARY.  2.2.3 EBOX SUMMARY.  2.2.4 ARITHMETIC PROCESSING ACCELERATOR SUMMARY.  2.2.5 MBOX SUMMARY.  2.2.6 MLMORY SUMMARY. | 2-1<br>2-2<br>2-3<br>2-6<br>2-6<br>2-6<br>2-7<br>2-7<br>2-7<br>2-7<br>2-9<br>2-16<br>2-11<br>2-11 |

| 2.3.2.1 NEW EXEC AND USER INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                            | 2-12<br>2-12<br>2-12                                                                              |

| COMPANY                                | CONFIDENTIAL Do not duplicate                                                                                                                                                                                   | 9-JUL-80                                                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 2.<br>2.<br>2.<br>2.                   | 2.3.3.2 CHANGED EXEC MODE ONLY INSTRUCTIONS 2.3.3.3 DISCONTINUED EXEC MODE ONLY INSTRUCTIONS. 2.3.3.4 OTHER EXEC MODE ONLY CHANGES 2.3.3.4.1 OVERFLOW FLAG 3.4 IO DIFFERENCES                                   | 2-13                                                                                                                       |

| CHAPTER 3 E                            | XEC MODE PROGRAMMING                                                                                                                                                                                            |                                                                                                                            |

| 3.3<br>3.4<br>3.5<br>3.5<br>3.6<br>3.7 | NEW INSTRUCTIONS VIRTUAL ADDRESSING 5.1 Introduction 3.5.1.1 Pager Data Structure 3.5.1.2 Super Section Pointers PROCESS CONTEXT VARIABLES 6.1 Introduction 3.6.1.1 New PC Double Word 3.6.1.2 Context Changing | 3-1<br>3-3<br>3-32<br>3-35<br>3-46<br>3-47<br>3-47<br>3-47<br>3-48<br>3-48<br>3-48<br>3-48<br>3-49<br>3-50<br>3-50<br>3-50 |

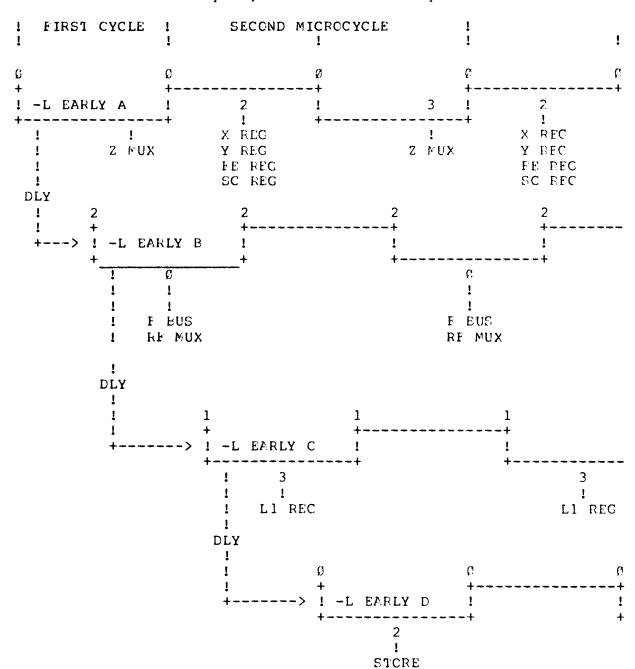

| , , , , , , , , , , , , , , , , , , ,  | INSTRUCTION EXECUTION                                                                                                                                                                                           |                                                                                                                            |

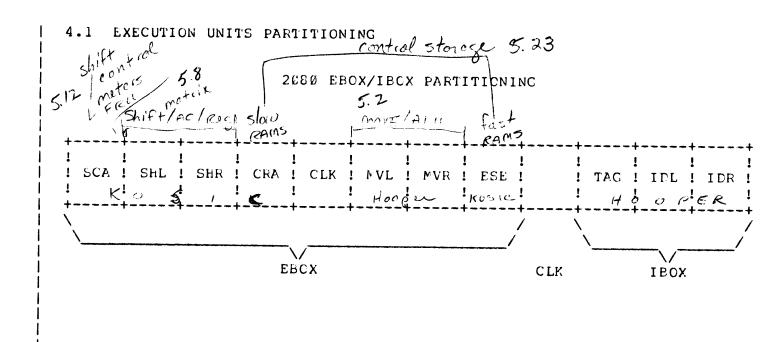

| 4                                      | EXECUTION UNITS PARTITIONING  1.1 Overall  1.2 IDR.  1.3 IDL.  1.4 TAG.  1.5 MVR.  1.6 MVL.  1.7 ESE.  1.8 CRA.  1.9 SHR.  1.10 SHL  1.11 SCA.  1.12 FPI.  1.13 FPA.  1.14 FPB.  1.15 FPC.                      | 4-1<br>4-2<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4                                           |

NUMBER FIELD Ø-17 <CL Bits 84-101>....

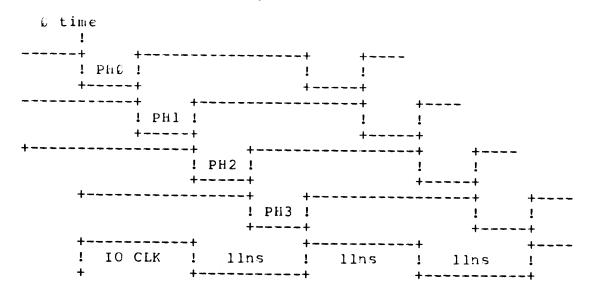

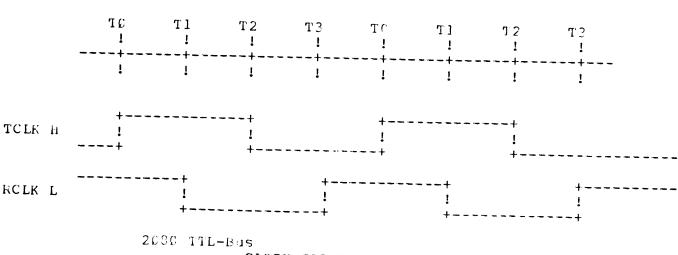

IO BOX INTERFACE TO THE SYSTEM CLOCK....

CPU INTERFACE TO THE SYSTEM CLOCK.....

MEMORY INTERFACE TO THE SYSTEM CLOCK....

4.2.8 SYSTEM CLOCKS.....

4-27

4-27

4-27

4-30

4-30

CHAPTER 5 EBOX

4.2.7.32

4.2.8.1

4.2.8.2

4.2.8.3

| COMPANY     | CONFIDENTIAL Do not duplicate      | 9-JUL-80     |

|-------------|------------------------------------|--------------|

| 5.1         | GENERAL                            | 5-1          |

| 5.2         | MOVE/ALU PATH                      | 5-2          |

| 5.3         | MCVE OPERATION                     | 5-2          |

| 5.4         | ALU OPERATION                      | 5-3          |

| 1 5.5       | L BUS                              | 5-3          |

| 5.6         | ERROR CONTROL                      | 5-4          |

| 5.7         | DIAGNOSTIC INTERFACE               | 5-5          |

| 5.8         | SHIFT/AC/REG PATH                  | 5-6          |

| 5.9         | SHIFT OPERATION                    | 5-6          |

| 5.10        |                                    | 5-6          |

| 5.11        |                                    | 5-6          |

| 5.12        | ERROR CONTROL                      | 5-7          |

| 5.13        |                                    | 5-8          |

| 5.14        | SHIFT CONTROL/METERS/ERROR CONTROL | 5-8          |

| 5.15        |                                    | 5-9          |

| 5.16        |                                    | 5-9          |

| 5.17        | ·                                  | 5-9          |

| 5.18        |                                    | 5-9          |

| 5.19        |                                    | 5-9          |

| 5.20        |                                    | 5-10         |

| 5.21        |                                    | 5-10         |

| 5.22        |                                    | 5-10         |

| 5.23        |                                    | 5-10         |

| •           | .23.1 RAM ARRAYS                   | 5-10         |

| 5.24        |                                    |              |

| 5.24        |                                    | 5-12         |

| 1 5.25      |                                    | 5-12         |

| 5.20        |                                    | 5-13         |

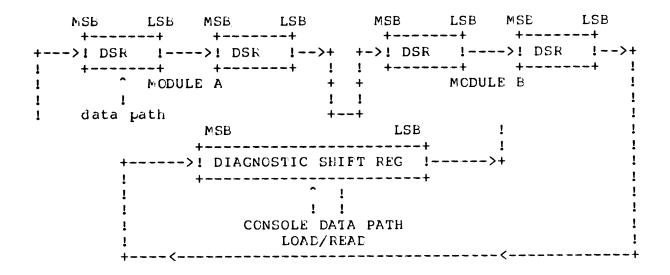

| 3.27        | DIAGNOSTIC INTERFACE               | J 1.5        |

| CHAPTER 6   | IBOX                               |              |

| 6.1         | GENERAL                            | 6-1          |

| 6.2         | MEMORY ADDRESS PATH                | 6-1          |

| 1 6.3       | INDEX AC                           |              |

| 6.4         | EA ALU                             | 6-2          |

| 1 6.5       | I STREAM PREFETCH                  | 6-2          |

| 6.6         | PC                                 | 6-3          |

| 6.7         | CONFLICT COMPARE                   | 6-3          |

| 6.8         | ERROR CONTROL                      | 6-3          |

| 6.9         | DIAGNOSTIC INTERFACE               | 6-4          |

| 6.16        |                                    | 6-4          |

| 6.1         |                                    | 6-4          |

| 6.12        |                                    | 6-4          |

| 6.13        |                                    | 6-5          |

| 6.14        |                                    | 6-5          |

| 6.19        |                                    | 6-5          |

| 6.10        |                                    | 6-7          |

| , , , , , , | 5.16.1 INA <eits g-4=""></eits>    | 6-7          |

| •           | 5.16.2 BR <bits 5-8=""></bits>     | 6-7          |

| •           | 5.16.3 ISTR <bit 11=""></bit>      | 6-9          |

| •           | 5.16.4 OP2 <bit 12=""></bit>       | 6 <b>-</b> 9 |

| •           | 5.16.5 WR <bits 13-14=""></bits>   | 6-9          |

| 1           | 1. TO. 1 MI INTIN IN TAILS         | U J          |

|     | MPANY CONFIDENTIAL Do not duplicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9-JUL-80     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| !   | 6.16.6 XR <bits 15-16=""></bits>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-9          |

| i   | 6.16.7 El <bits 17-18=""></bits>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-1¢         |

| !   | 6.16.8 E2 <bits 19-20=""></bits>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-10         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-1 Ø        |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-10         |

| i   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-11         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-11         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-12         |

| 1   | 6.17 STREAM LRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-12         |

| 1   | TO DOLL DIVIDED TO DOLL DIVIDED TO SECOND TO S | 6-14         |

| !   | 6.19 ISET<br>6.19.1 SKIP/JUMP <bits 0-2=""></bits>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-14         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-14         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-15         |

| 1   | 6.19.3 Y1 DISABLE <bit 4=""></bit>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-15         |

| 1   | 6.19.4 OP MUX <bits 5-6=""></bits>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-15         |

| !   | 6.19.5 P <bit 7=""></bit>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-15         |

| 1   | 6.20 INSTRUCTION VALID BITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-16         |

| 1   | 6.21 SELECTED I CONTROLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-17         |

| !   | 6.22 INDEX REG CONTROLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-17         |

| 1   | 6.23 ERROR CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-18         |

| 1   | 6.24 DIAGNOSTIC INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-18         |

| СНА | ER 7 FPA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| !   | 7.1 GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-1          |

| ļ   | 7.2 ARRAY CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1          |

| !   | 7.3 ARRAY CONTROL STORAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1          |

| ļ   | 7.4 OPERAND BUFFERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-1          |

| !   | 7.5 MULTIPLIER FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-1          |

| 1   | 7.6 DIVIDE ALGORITHM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-1          |

| ļ   | 7.7 POST NCRMALIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-2          |

| !   | 7.8 ERROR CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-2          |

| !   | 7.9 DIAGNOSTIC INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7 <b>-</b> 2 |

| 1   | 7.10 MULTIPLY ARRAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7 <b>-</b> 2 |